场效应管通电短路是指MOS管在上电瞬间或工作过程中 ,漏极(D)与源极(S)之间失去阻断能力,呈现极低电阻(通常<1Ω)的失效状态。这是电力电子系统中最严重的故障之一,可能引发连锁损坏甚至火灾,需从失效机理、检测方法和预防策略三个层面系统应对。

一、短路失效的根本原因

1. 过压击穿(雪崩失效)

当漏源电压Vds超过击穿电压BVDSS时,漂移区发生雪崩倍增效应,电流雪崩式增长导致结温瞬时超过600℃,金属化层熔化、硅熔穿,最终形成永久性短路通道。常见诱因:

-

感性负载关断:电机绕组、变压器漏感在MOS关断时产生反向电动势,尖峰电压可达电源电压3-5倍

-

雷电浪涌:电源输入端未配置有效TVS,±4kV浪涌直接击穿MOS

-

PCB布局失误:功率回路寄生电感过大,开关振铃电压叠加至MOS耐压极限

2. 过流烧毁(热失效)

漏极电流Id超过最大脉冲电流Id,pulse,导致结温超过Tjmax(通常150℃),塑料封装碳化、键合线熔断,最终漏源短路。典型场景:

-

负载短路:电机堵转、电容击穿时,电流不受限制上升至数百安培

-

驱动不足:栅极电压Vgs过低(<Vgs(th)+2V),MOS工作在线性区而非饱和区,功耗剧增(P=I²×RDS(on))

-

散热失效:散热器脱落、导热硅脂干涸,热量无法导出

3. 栅极击穿(栅源短路)

栅源电压Vgs超过最大额定值(±20V),栅氧化层(仅数纳米厚)击穿,形成导电通道,导致栅源短路,继而引发漏源失控性导通。诱因:

-

静电放电(ESD):人体静电(可达8kV)直接接触栅极引脚

-

驱动电路故障:驱动IC失效导致输出电压失控

-

米勒效应:漏极dv/dt通过Cgd耦合抬升栅极电压,超过击穿阈值

4. 制造缺陷(早期失效)

器件出厂时存在 latent defect(隐性缺陷),如氧化层针孔、金属化层空洞,在通电后电场应力下快速扩展,表现为时好时坏 的不稳定短路,最终彻底失效。

二、短路的典型现象与检测

1. 上电即炸

-

现象:系统通电瞬间,MOS管冒烟、爆裂,伴随巨大响声和火光

-

检测:断电后万用表测漏源电阻<1Ω,体二极管压降消失

-

根本原因:栅源短路或漏源已永久击穿

2. 工作一段时间后短路

-

现象:设备运行数分钟至数小时后,MOS突然失效,电流激增,保险丝熔断

-

检测 :热成像仪观测到MOS壳温异常(>100℃),断电后阻值正常,冷却后又短路( 热失控 )

-

根本原因:散热不足导致结温循环,金属化层疲劳

3. 间歇性短路

-

现象:设备时好时坏,震动或高温时故障重现

-

检测:示波器监测漏极波形,出现随机尖峰;用二极管档测量,读数不稳定

-

根本原因:键合线虚焊或芯片裂纹

三、诊断与定位方法

1. 离线检测(断电状态)

-

万用表二极管档:红表笔接源极、黑表笔接漏极,正常应显示0.4-0.9V(体二极管压降);显示0V或OL表示短路或开路

-

电阻档测量:漏源电阻应>1MΩ(关断状态),若<100Ω则已击穿

-

栅极电荷感应:用手指同时触摸栅源极,二极管档读数应变化,无变化说明栅极开路

2. 在线监测(上电状态)

-

示波器测Vds:正常开关波形应陡峭,若Vds在导通时>1V或关断时<0.9×Vbus,说明未饱和导通或已短路

-

电流探头监测Id:短路时电流波形出现远超额定值的尖峰,di/dt可达100A/μs

-

热成像:短路MOS表面温度异常热点,与相邻器件温差>30℃

3. 破坏性分析

对疑似失效MOS进行开封(decap),显微镜下观察:

-

金属化层熔球:过流导致铝层熔化,形成导电桥

-

键合线熔断:金属线断裂或颈部变细,接触电阻剧增

-

芯片裂纹:机械应力或热应力导致硅片开裂

四、预防与保护策略

1. 电压钳位与吸收(防过压)

-

TVS二极管:在漏源极并联TVS(如SMCJ58A),钳位电压< BVDSS×80%

-

RC吸收网络:在漏源极并联100Ω+1nF,抑制开关振铃

-

有源钳位:高端驱动中采用齐纳二极管+快恢复二极管组合,动态钳位尖峰

2. 电流限制与检测(防过流)

-

检流电阻:源极串联0.01Ω电阻,实时监测电流,MCU过流阈值设为Id的120%

-

快速保险丝 :在MOS前串联快熔保险丝(如392系列),响应时间<10ms

-

退饱和检测:监测Vds压降,若Vds > 2V且持续>1μs,判定为过流,立即关断

3. 驱动加固(防栅极击穿)

-

TVS钳位 :栅源极间并联5V TVS(如SMDJ5.0),响应时间<1ps

-

串联电阻:栅极串联10Ω-47Ω电阻,抑制振荡和电流尖峰

-

负压关断:关断时施加-2V至-5V负偏压,加速关断并防止dv/dt误导通

-

ESD防护:操作前佩戴防静电手环,PCB设计时栅极引脚周围铺地保护

4. 热设计冗余(防过热)

-

功率降额:实际功耗< Ptot的70%,留30%热裕量

-

散热器:TO-220封装需加装散热器,热阻<5℃/W

-

温度监测:在MOS封装表面贴NTC,超80℃自动降载或关断

5. 冗余设计(防灾难性失效)

-

双MOS串联:两颗MOS串联,即使一颗短路,另一颗仍可阻断电流

-

智能诊断:MCU实时监测MOS漏源压降,异常时上报故障并锁定输出

五、工程实践要点

-

降额使用:电压降额20%,电流降额30%,功率降额50%

-

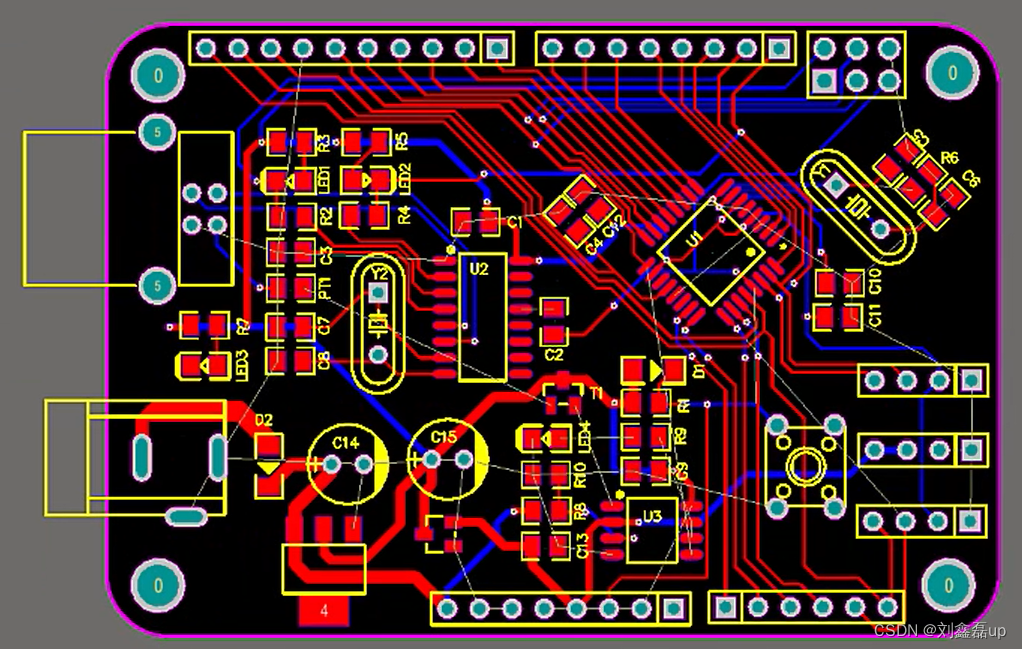

PCB布局:功率回路面积<100mm²,驱动走线<20mm,开尔文源极分离

-

选型匹配:驱动电压> Vgs(th)+2V,驱动电流> Qg/50ns

-

测试验证 :必须通过双脉冲测试 和短路耐受测试,确保在极限工况下不短路

六、失效后的善后处理

MOS短路后必须排查:

-

驱动IC:短路大电流可能烧毁驱动芯片输出级

-

电流采样电阻:是否过热变色、阻值漂移

-

PCB走线:铜箔是否熔断、碳化,形成二次短路路径

-

后级负载:电池是否过充鼓包、电容是否击穿

严禁直接更换MOS上电测试 :必须先断开负载,用可调电源限流(100mA)上电,确认无短路后再逐步加载,否则新MOS会立即再次损坏。

核心警示 :MOS通电短路不是随机事件,而是设计缺陷、参数失配或应力超标的必然结果。90%的短路故障可通过科学降额、完善保护和精细布局预防,剩余10%源于器件早期失效或极端浪涌,需通过冗余设计兜底。