20251219给飞凌OK3588-C开发板适配Rockchip原厂的Buildroot【linux-5.10】后解决启动不了报atf-2的问题

2025/12/18 13:57

https://blog.csdn.net/zjapq/article/details/127672861

【问题排查】RK3588S烧录完后无法启动的问题

DDR?

EMMC?

还是RK3588异常?

这么看着像是内存

TF卡刷机。正常进系统了。我还需要 进一步测试![捂脸]

昨晚都快下班了。有点吓人!

1、飞凌OK3588-C开发板适配Rockchip原厂的Buildroot【linux-5.10】后,直接拨动开关关机。

突然需要看开机的一些LOG打印信息。又拨动开关开机了。

就打印如新信息:

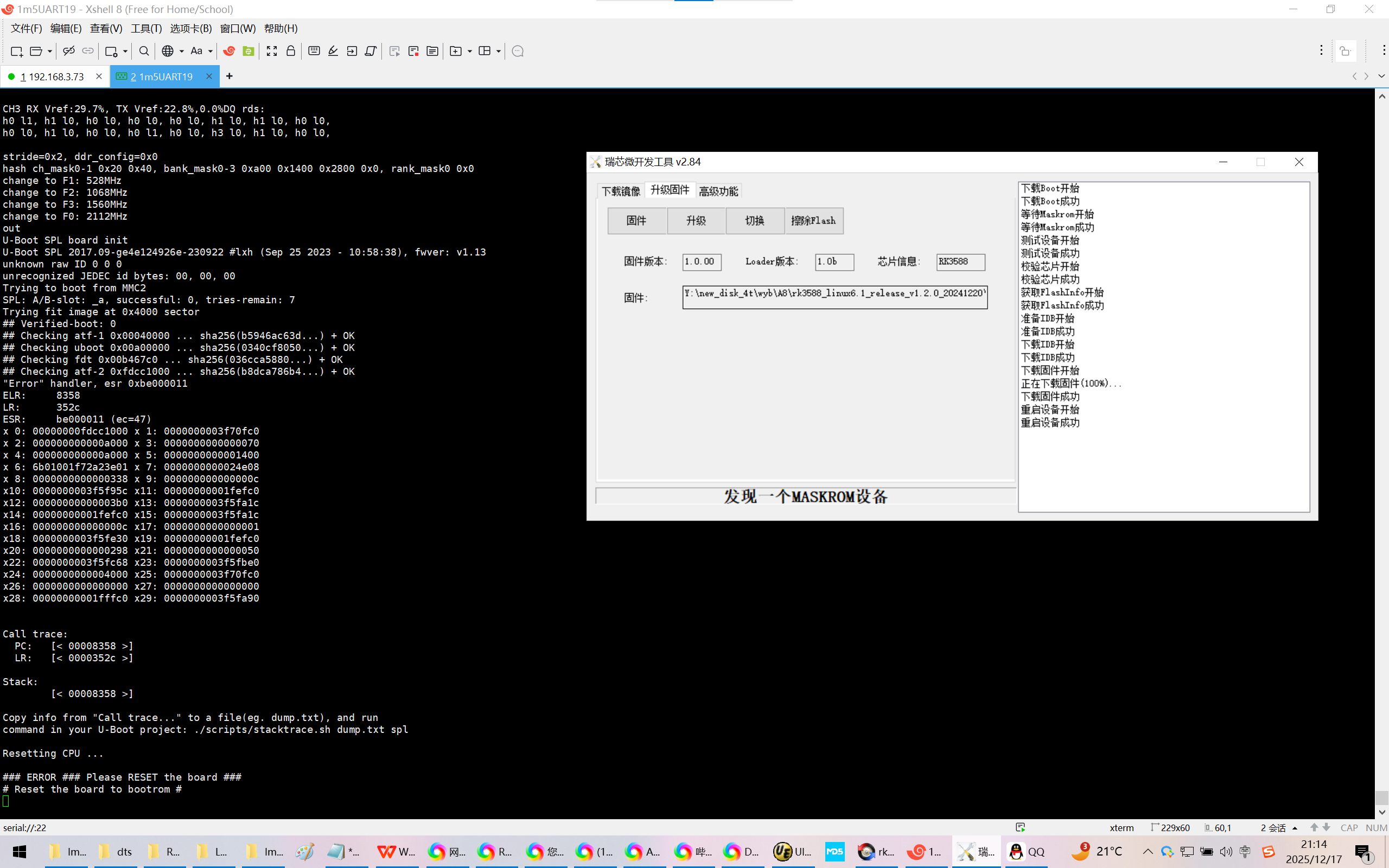

BEGIN\] 2025/12/18 8:50:16 DDR 9fa84341ce typ 25/07/10-12:00.01,fwver: v1.18 ch0 ttot10 ch1 ttot10 ch2 ttot10 ch3 ttot10 ch0 ttot16 LPDDR4X, 2112MHz channel\[0\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB ch1 ttot16 channel\[1\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB ch2 ttot16 channel\[2\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB ch3 ttot16 channel\[3\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB Manufacturer ID:0x13 DQS rds:l0,l0 CH0 RX Vref:29.7%, TX Vref:24.8%,0.0% DQ rds:l0 h1 l0 h1 l0 h1 l0 h1, l0 h1 l0 h1 h1 h1 h2 h3 DQS rds:l0,l0 CH1 RX Vref:28.9%, TX Vref:22.8%,0.0% DQ rds:h1 l0 h1 h2 l1 l0 l0 h1, h1 l0 h1 h4 h1 h1 h1 l0 DQS rds:h1,l0 CH2 RX Vref:31.4%, TX Vref:22.8%,0.0% DQ rds:h1 h1 h1 h3 h2 h2 h2 l0, h1 h3 h2 h2 h3 h3 h1 h1 DQS rds:l0,l1 CH3 RX Vref:29.7%, TX Vref:22.8%,0.0% DQ rds:l1 h1 l0 l0 l0 h2 h1 h1, l0 h1 l0 l1 l0 h3 h1 l0 stride=0x2, ddr_config=0x0 hash ch_mask0-1 0x20 0x40, bank_mask0-3 0xa00 0x1400 0x2800 0x0, rank_mask0 0x0 change to F1: 528MHz ch0 ttot10 ch1 ttot10 ch2 ttot10 ch3 ttot10 change to F2: 1068MHz ch0 ttot12 ch1 ttot12 ch2 ttot12 ch3 ttot12 change to F3: 1560MHz ch0 ttot14 ch1 ttot14 ch2 ttot14 ch3 ttot14 change to F0: 2112MHz ch0 ttot16 ch1 ttot16 ch2 ttot16 ch3 ttot16 out U-Boot SPL board init U-Boot SPL 2017.09-ge4e124926e-230922 #lxh (Sep 25 2023 - 10:58:38), fwver: v1.13 unknown raw ID 0 0 0 unrecognized JEDEC id bytes: 00, 00, 00 Trying to boot from MMC2 SPL: A/B-slot: _a, successful: 0, tries-remain: 7 Trying fit image at 0x4000 sector ## Verified-boot: 0 ## Checking atf-1 0x00040000 ... sha256(b5946ac63d...) + OK ## Checking uboot 0x00a00000 ... sha256(0340cf8050...) + OK ## Checking fdt 0x00b467c0 ... sha256(036cca5880...) + OK ## Checking atf-2 0xfdcc1000 ... sha256(b8dca786b4...) + OK "Error" handler, esr 0xbe000011 ELR: 8388 LR: 352c ESR: be000011 (ec=47) x 0: 00000000fdcc1000 x 1: 0000000003f70fc0 x 2: 000000000000a000 x 3: 0000000000000060 x 4: 000000000000a000 x 5: 0000000000001400 x 6: 6b01001f72a17f61 x 7: 0000000000024e08 x 8: 0000000000000338 x 9: 000000000000000c x10: 0000000003f5f95c x11: 00000000001fefc0 x12: 00000000000003b0 x13: 0000000003f5fa1c x14: 00000000001fefc0 x15: 0000000003f5fa1c x16: 000000000000000c x17: 0000000000000001 x18: 0000000003f5fe30 x19: 00000000001fefc0 x20: 0000000000000298 x21: 0000000000000050 x22: 0000000003f5fc68 x23: 0000000003f5fbe0 x24: 0000000000004000 x25: 0000000003f70fc0 x26: 0000000000000000 x27: 0000000000000000 x28: 00000000001fffc0 x29: 0000000003f5fa90 Call trace: PC: \[\< 00008388 \>

LR: [< 0000352c >]

Stack:

\< 00008388 \>

Copy info from "Call trace..." to a file(eg. dump.txt), and run

command in your U-Boot project: ./scripts/stacktrace.sh dump.txt spl

Resetting CPU ...

ERROR ### Please RESET the board

Reset the board to bootrom

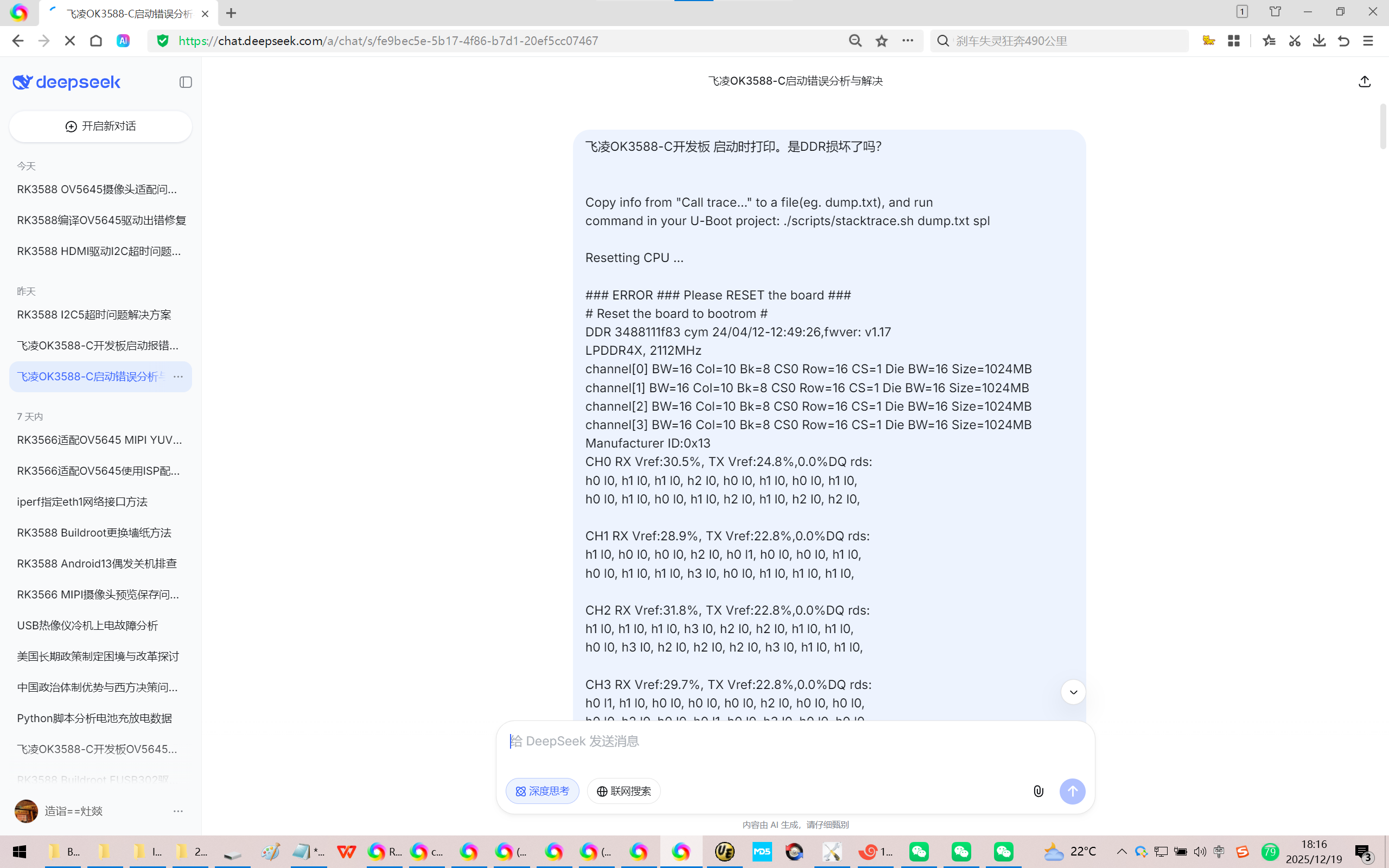

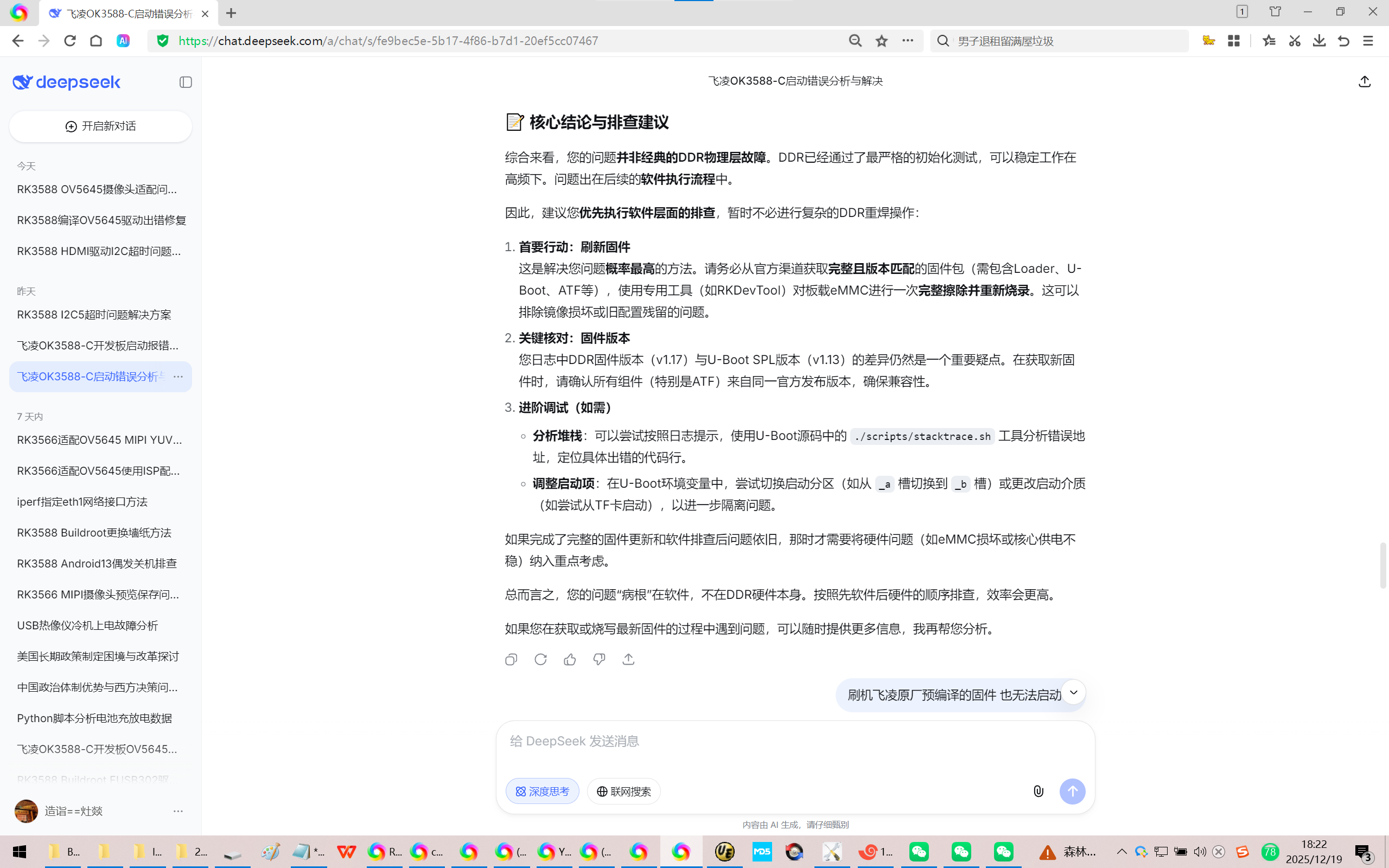

END\] 2025/12/18 9:00:40   2、老规矩,按RECOVERY按键/MASKROM按键刷飞凌原厂预编译的固件。 linux/Buildroot、Android14轮番输出,都可以通过USB线刷工具接USB线RKDevTool_v3.15_for_window正常刷机的。 但是就是启动不了,出错在atf-2的地方! 以为 飞凌OK3588-C开发板 如此之脆弱! 都准备返修了,上DeepSeek。 https://chat.deepseek.com/a/chat/s/fe9bec5e-5b17-4f86-b7d1-20ef5cc07467 飞凌OK3588-C启动错误分析与解决 飞凌OK3588-C开发板 启动时打印。是DDR损坏了吗? Copy info from "Call trace..." to a file(eg. dump.txt), and run command in your U-Boot project: ./scripts/stacktrace.sh dump.txt spl Resetting CPU ... ### ERROR ### Please RESET the board ### # Reset the board to bootrom # DDR 3488111f83 cym 24/04/12-12:49:26,fwver: v1.17 LPDDR4X, 2112MHz channel\[0\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB channel\[1\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB channel\[2\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB channel\[3\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB Manufacturer ID:0x13 CH0 RX Vref:30.5%, TX Vref:24.8%,0.0%DQ rds: h0 l0, h1 l0, h1 l0, h2 l0, h0 l0, h1 l0, h0 l0, h1 l0, h0 l0, h1 l0, h0 l0, h1 l0, h2 l0, h1 l0, h2 l0, h2 l0, CH1 RX Vref:28.9%, TX Vref:22.8%,0.0%DQ rds: h1 l0, h0 l0, h0 l0, h2 l0, h0 l1, h0 l0, h0 l0, h1 l0, h0 l0, h1 l0, h1 l0, h3 l0, h0 l0, h1 l0, h1 l0, h1 l0, CH2 RX Vref:31.8%, TX Vref:22.8%,0.0%DQ rds: h1 l0, h1 l0, h1 l0, h3 l0, h2 l0, h2 l0, h1 l0, h1 l0, h0 l0, h3 l0, h2 l0, h2 l0, h2 l0, h3 l0, h1 l0, h1 l0, CH3 RX Vref:29.7%, TX Vref:22.8%,0.0%DQ rds: h0 l1, h1 l0, h0 l0, h0 l0, h0 l0, h2 l0, h0 l0, h0 l0, h0 l0, h2 l0, h0 l0, h0 l1, h0 l0, h3 l0, h0 l0, h0 l0, stride=0x2, ddr_config=0x0 hash ch_mask0-1 0x20 0x40, bank_mask0-3 0xa00 0x1400 0x2800 0x0, rank_mask0 0x0 change to F1: 528MHz change to F2: 1068MHz change to F3: 1560MHz change to F0: 2112MHz out Boot1 Release Time: Oct 17 2023 17:09:54, version: 1.11 Emmc IO init. Emmc IO init. mmc_set_bus_width: 1 SetEmmcClk: 375000, 2, 64 mmc_switch index:183, value:0x2 mmc_switch index:185, value:0x2 SetEmmcClk: 375000, 2, 64 mmc_set_bus_width: 8 SetEmmcClk: 200000000, 0, 3 Enable PHY CLK: 200000000, timing: 9 SdmmcInit=2 0 BootCapSize=100000 UserCapSize=29600MB FwPartOffset=2000 , 100000 UsbBoot ...52756 powerOn 55009 SoftReset, 35661021 us DDR 3488111f83 cym 24/04/12-12:49:26,fwver: v1.17 LPDDR4X, 2112MHz channel\[0\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB channel\[1\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB channel\[2\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB channel\[3\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB Manufacturer ID:0x13 CH0 RX Vref:30.1%, TX Vref:24.8%,0.0%DQ rds: h0 l0, h1 l0, h0 l0, h1 l0, h0 l0, h1 l0, h0 l0, h0 l0, h0 l0, h1 l0, h0 l0, h1 l0, h1 l0, h1 l0, h2 l0, h2 l0, CH1 RX Vref:28.9%, TX Vref:22.8%,0.0%DQ rds: h1 l0, h0 l0, h1 l0, h2 l0, h0 l1, h0 l0, h0 l0, h1 l0, h1 l0, h1 l0, h1 l0, h4 l0, h1 l0, h1 l0, h1 l0, h0 l0, CH2 RX Vref:31.8%, TX Vref:22.8%,0.0%DQ rds: h2 l0, h1 l0, h1 l0, h1 l0, h2 l0, h2 l0, h3 l0, h1 l0, h0 l0, h3 l0, h2 l0, h2 l0, h2 l0, h3 l0, h1 l0, h0 l0, CH3 RX Vref:29.7%, TX Vref:22.8%,0.0%DQ rds: h0 l1, h1 l0, h0 l0, h0 l0, h0 l0, h1 l0, h1 l0, h0 l0, h0 l0, h1 l0, h0 l0, h0 l1, h0 l0, h3 l0, h1 l0, h0 l0, stride=0x2, ddr_config=0x0 hash ch_mask0-1 0x20 0x40, bank_mask0-3 0xa00 0x1400 0x2800 0x0, rank_mask0 0x0 change to F1: 528MHz change to F2: 1068MHz change to F3: 1560MHz change to F0: 2112MHz out U-Boot SPL board init U-Boot SPL 2017.09-ge4e124926e-230922 #lxh (Sep 25 2023 - 10:58:38), fwver: v1.13 unknown raw ID 0 0 0 unrecognized JEDEC id bytes: 00, 00, 00 Trying to boot from MMC2 SPL: A/B-slot: _a, successful: 0, tries-remain: 7 Trying fit image at 0x4000 sector ## Verified-boot: 0 ## Checking atf-1 0x00040000 ... sha256(b5946ac63d...) + OK ## Checking uboot 0x00a00000 ... sha256(0340cf8050...) + OK ## Checking fdt 0x00b467c0 ... sha256(036cca5880...) + OK ## Checking atf-2 0xfdcc1000 ... sha256(b8dca786b4...) + OK "Error" handler, esr 0xbe000011 ELR: 8358 LR: 352c ESR: be000011 (ec=47) x 0: 00000000fdcc1000 x 1: 0000000003f70fc0 x 2: 000000000000a000 x 3: 0000000000000070 x 4: 000000000000a000 x 5: 0000000000001400 x 6: 6b01001f72a23e01 x 7: 0000000000024e08 x 8: 0000000000000338 x 9: 000000000000000c x10: 0000000003f5f95c x11: 00000000001fefc0 x12: 00000000000003b0 x13: 0000000003f5fa1c x14: 00000000001fefc0 x15: 0000000003f5fa1c x16: 000000000000000c x17: 0000000000000001 x18: 0000000003f5fe30 x19: 00000000001fefc0 x20: 0000000000000298 x21: 0000000000000050 x22: 0000000003f5fc68 x23: 0000000003f5fbe0 x24: 0000000000004000 x25: 0000000003f70fc0 x26: 0000000000000000 x27: 0000000000000000 x28: 00000000001fffc0 x29: 0000000003f5fa90 Call trace: PC: \[\< 00008358 \>

LR: [< 0000352c >]

Stack:

\< 00008358 \>

Copy info from "Call trace..." to a file(eg. dump.txt), and run

command in your U-Boot project: ./scripts/stacktrace.sh dump.txt spl

Resetting CPU ...

ERROR ### Please RESET the board

Reset the board to bootrom

https://blog.csdn.net/zjapq/article/details/127672861

【问题排查】RK3588S烧录完后无法启动的问题

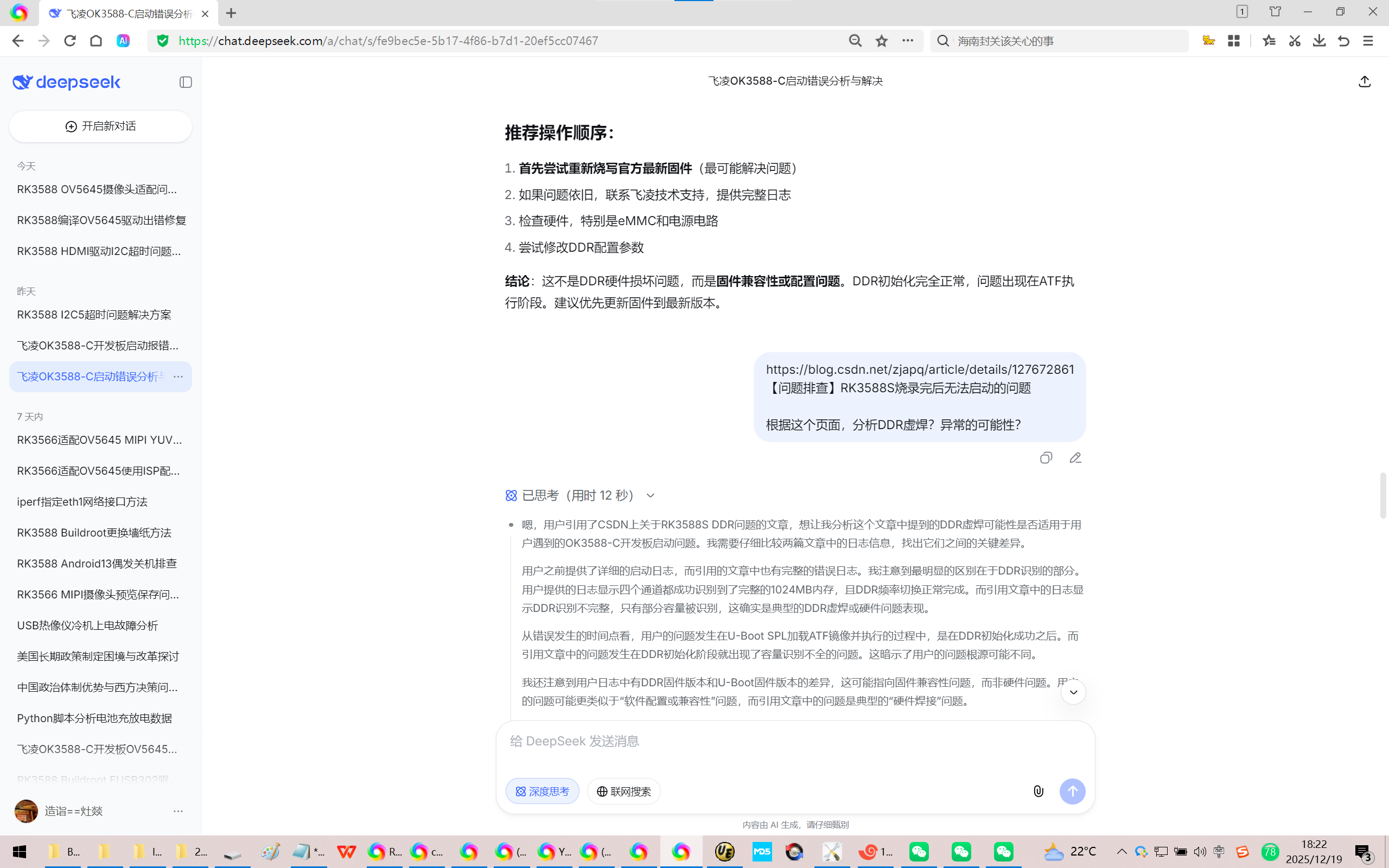

根据这个页面,分析DDR虚焊?异常的可能性?

正在阅读

正在阅读

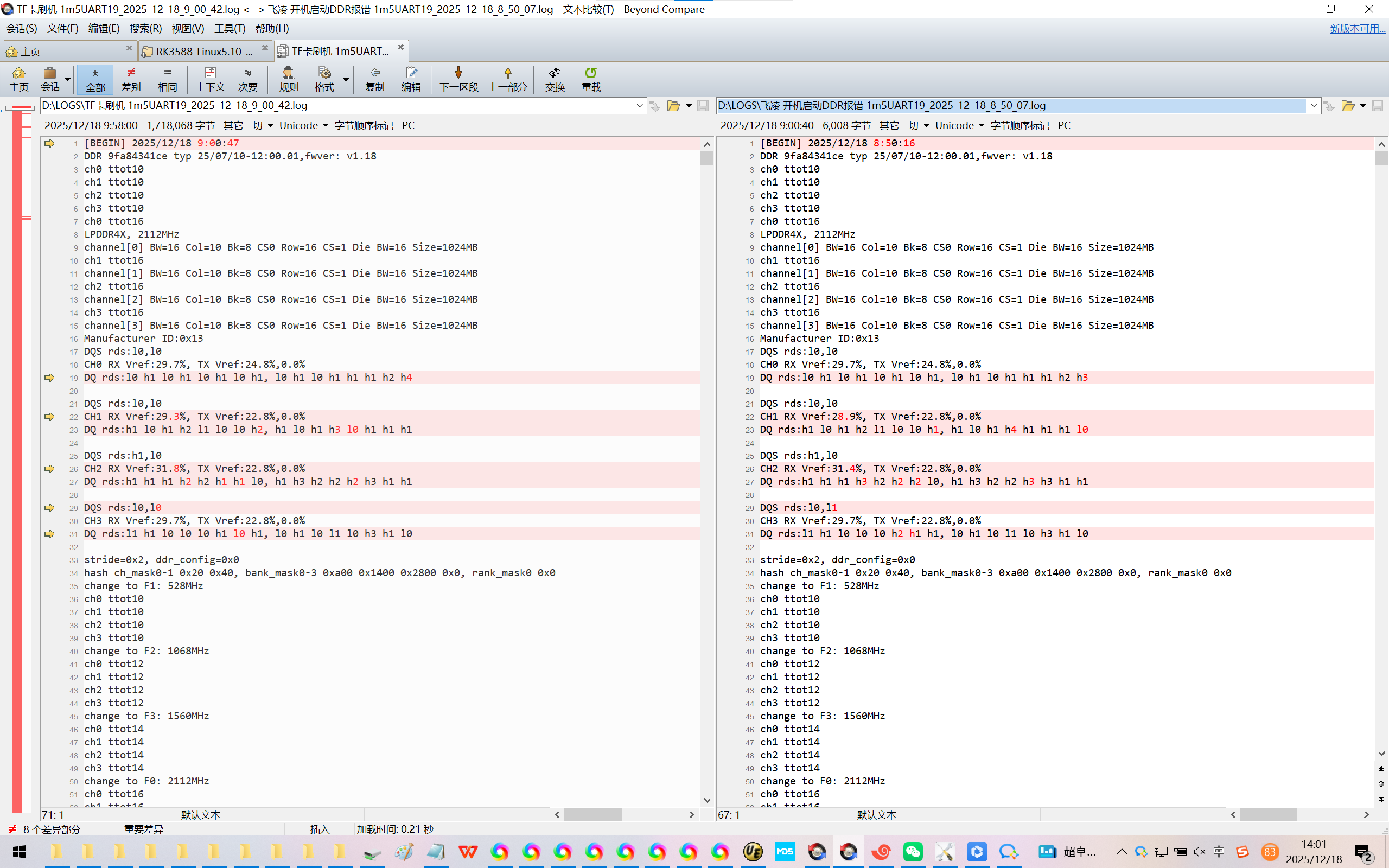

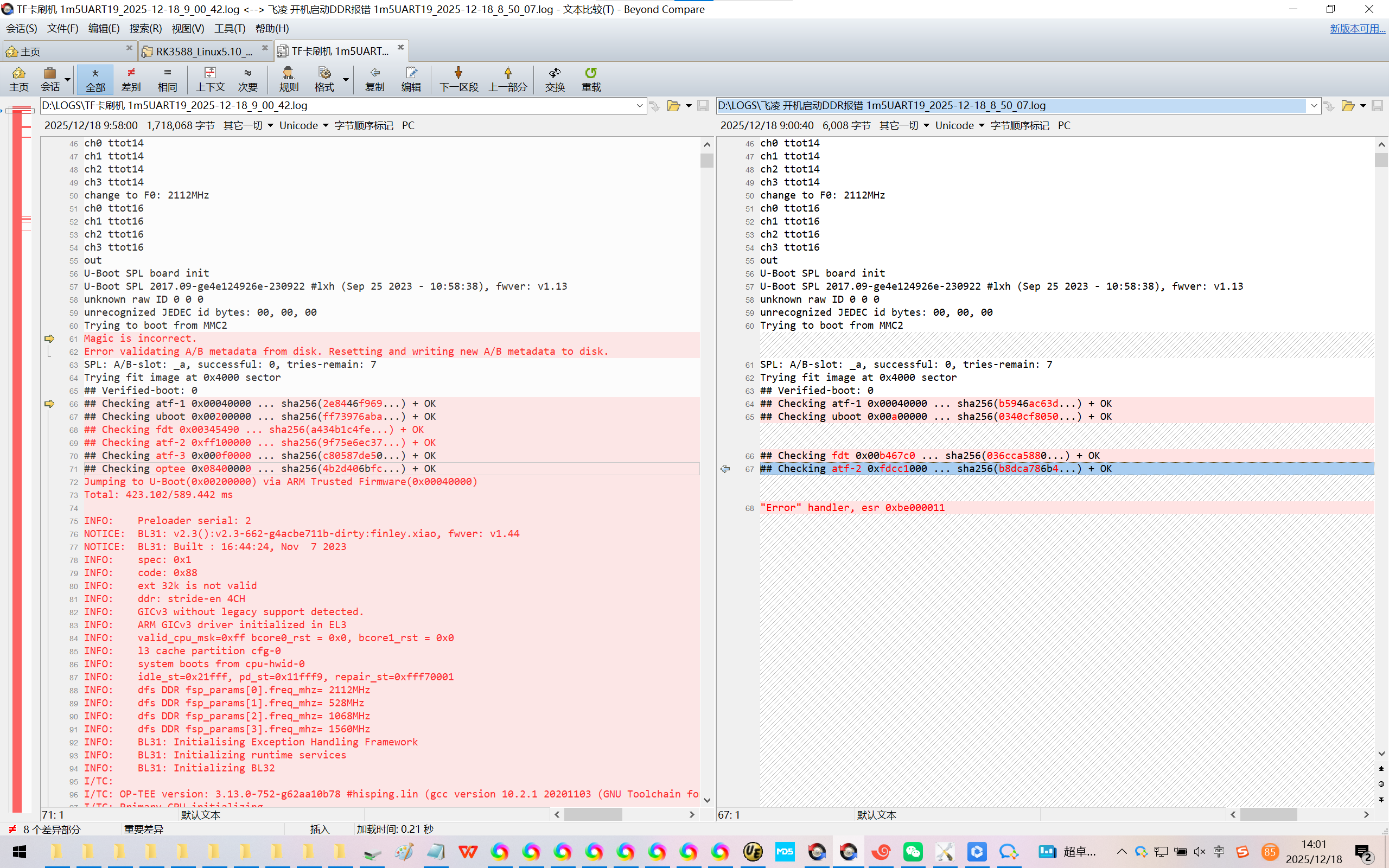

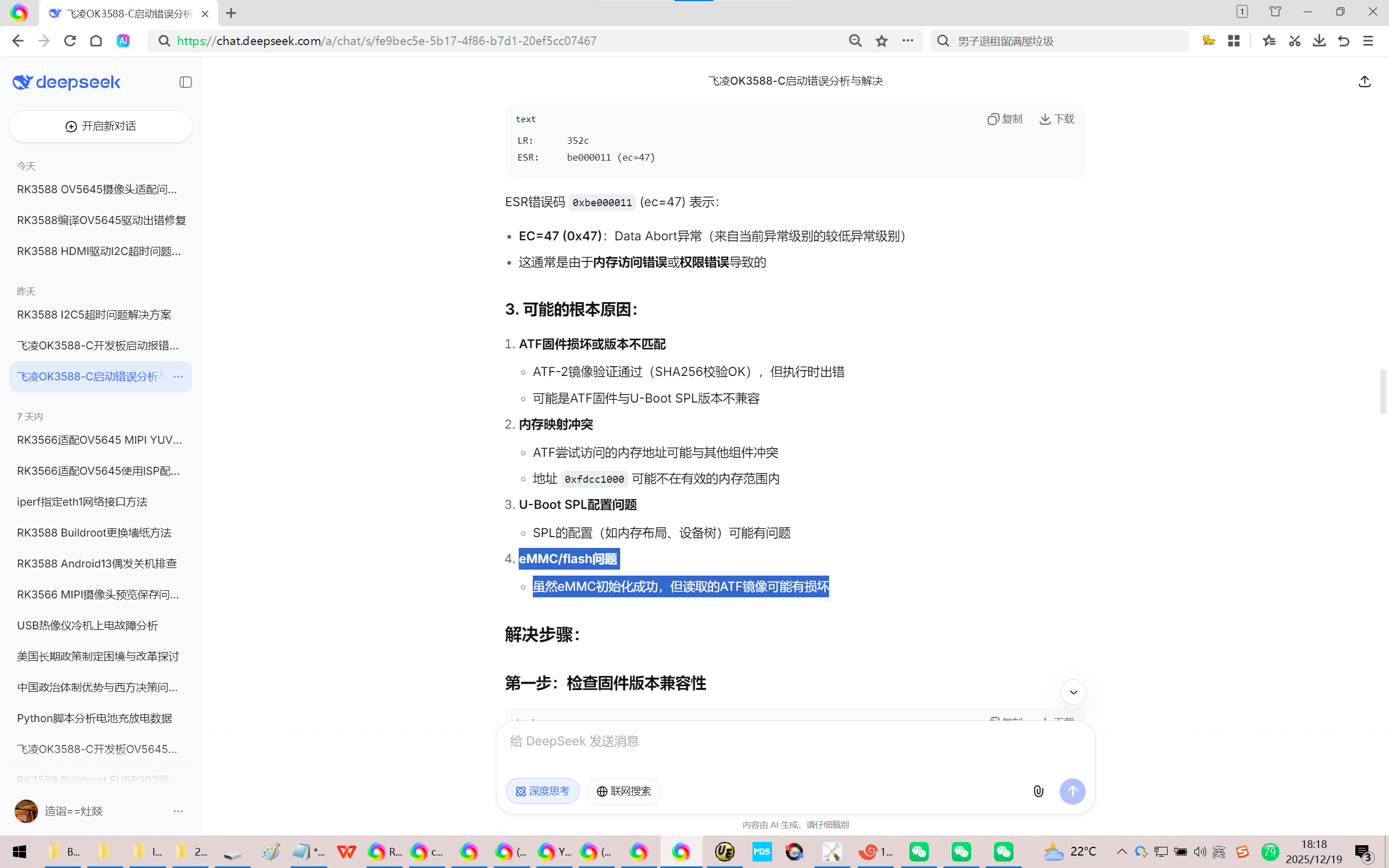

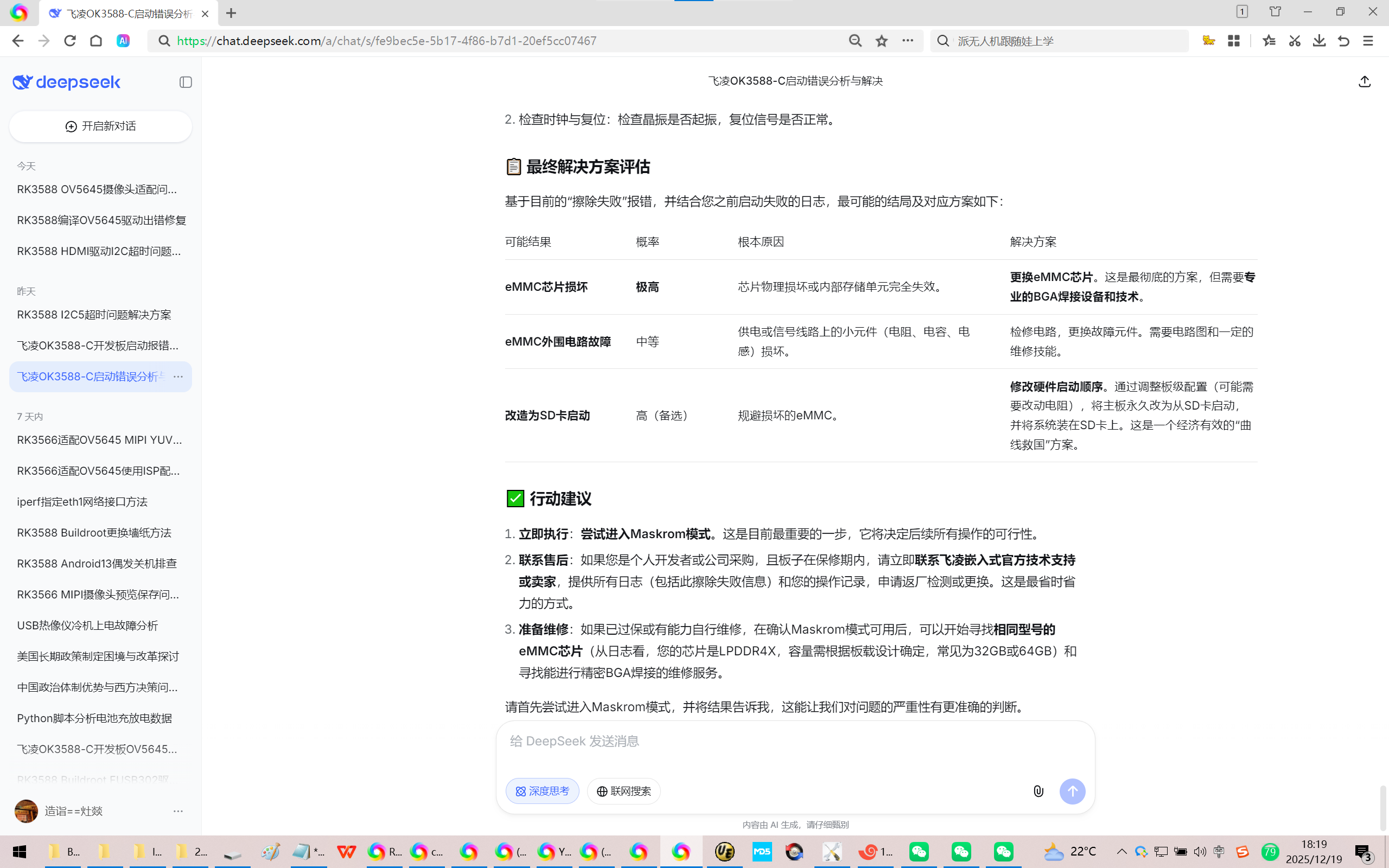

嗯,用户引用了CSDN上关于RK3588S DDR问题的文章,想让我分析这个文章中提到的DDR虚焊可能性是否适用于用户遇到的OK3588-C开发板启动问题。我需要仔细比较两篇文章中的日志信息,找出它们之间的关键差异。

用户之前提供了详细的启动日志,而引用的文章中也有完整的错误日志。我注意到最明显的区别在于DDR识别的部分。用户提供的日志显示四个通道都成功识别到了完整的1024MB内存,且DDR频率切换正常完成。而引用文章中的日志显示DDR识别不完整,只有部分容量被识别,这确实是典型的DDR虚焊或硬件问题表现。

从错误发生的时间点看,用户的问题发生在U-Boot SPL加载ATF镜像并执行的过程中,是在DDR初始化成功之后。而引用文章中的问题发生在DDR初始化阶段就出现了容量识别不全的问题。这暗示了用户的问题根源可能不同。

我还注意到用户日志中有DDR固件版本和U-Boot固件版本的差异,这可能指向固件兼容性问题,而非硬件问题。用户的问题可能更类似于"软件配置或兼容性"问题,而引用文章中的问题是典型的"硬件焊接"问题。

为了更清晰地展示这些差异,我打算设计一个对比表格,从几个关键维度将两个问题进行对比。然后根据分析结果,建议用户不必立即进行DDR重焊,而是优先进行固件更新和软件层面的调试。最后提供分步排查建议,从简单到复杂地解决问题。

3、

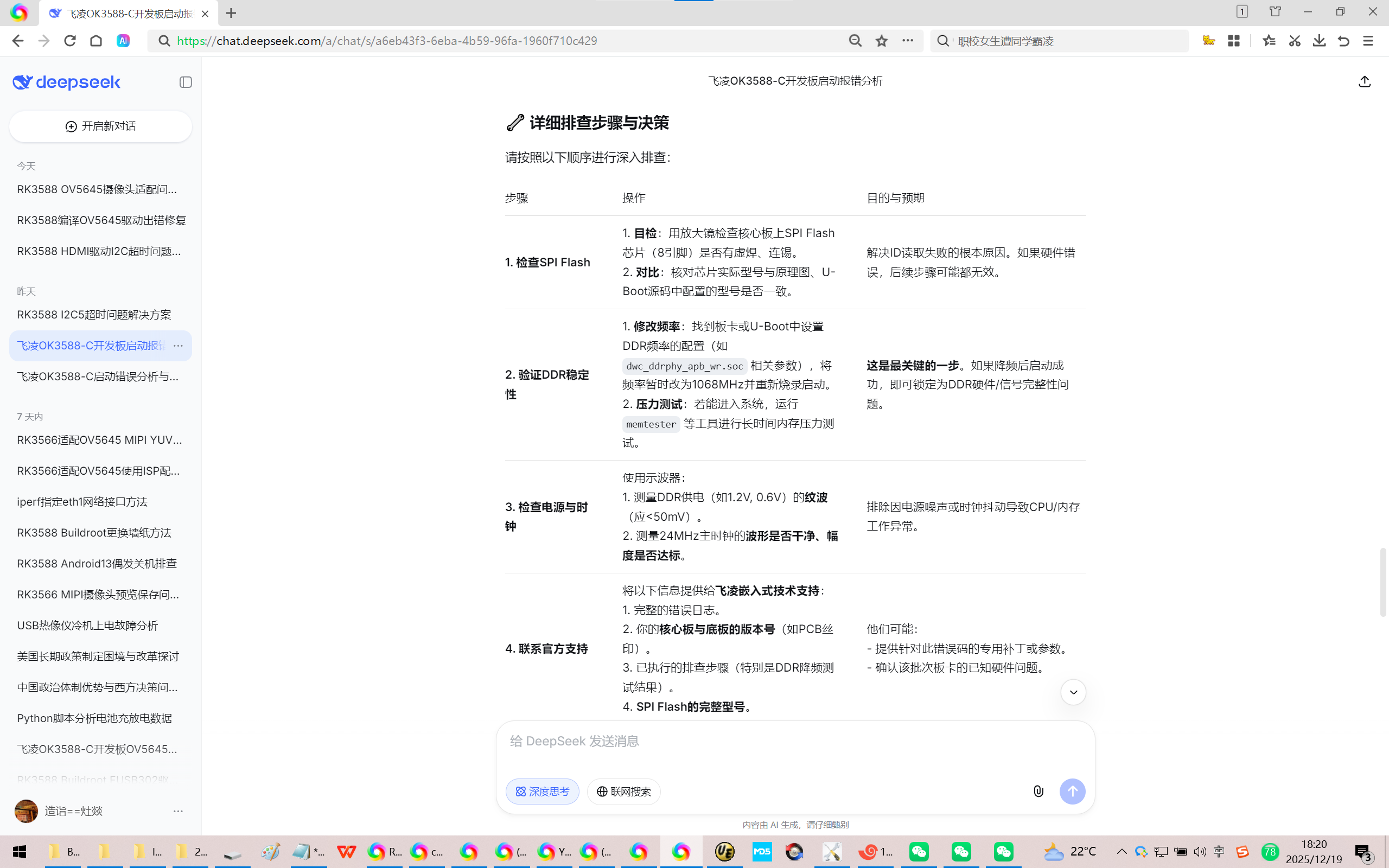

https://chat.deepseek.com/a/chat/s/a6eb43f3-6eba-4b59-96fa-1960f710c429

飞凌OK3588-C开发板启动报错分析

飞凌OK3588-C开发板,启动报错:

Xshell 8 (Build 0087)

Copyright (c) 2024 NetSarang Computer, Inc. All rights reserved.

Type `help' to learn how to use Xshell prompt.

C:\\\~\]$ Connecting to COM19... Connected. DDR 9fa84341ce typ 25/07/10-12:00.01,fwver: v1.18 ch0 ttot10 ch1 ttot10 ch2 ttot10 ch3 ttot10 ch0 ttot16 LPDDR4X, 2112MHz channel\[0\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB ch1 ttot16 channel\[1\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB ch2 ttot16 channel\[2\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB ch3 ttot16 channel\[3\] BW=16 Col=10 Bk=8 CS0 Row=16 CS=1 Die BW=16 Size=1024MB Manufacturer ID:0x13 DQS rds:l0,l0 CH0 RX Vref:29.7%, TX Vref:24.8%,0.0% DQ rds:l0 h1 l0 h1 l0 h1 l0 h1, l0 h1 l0 h1 h1 h1 h2 h3 DQS rds:l0,l0 CH1 RX Vref:28.9%, TX Vref:22.8%,0.0% DQ rds:h1 l0 h1 h2 l1 l0 l0 h1, h1 l0 h1 h4 h1 h1 h1 l0 DQS rds:h1,l0 CH2 RX Vref:31.4%, TX Vref:22.8%,0.0% DQ rds:h1 h1 h1 h3 h2 h2 h2 l0, h1 h3 h2 h2 h3 h3 h1 h1 DQS rds:l0,l1 CH3 RX Vref:29.7%, TX Vref:22.8%,0.0% DQ rds:l1 h1 l0 l0 l0 h2 h1 h1, l0 h1 l0 l1 l0 h3 h1 l0 stride=0x2, ddr_config=0x0 hash ch_mask0-1 0x20 0x40, bank_mask0-3 0xa00 0x1400 0x2800 0x0, rank_mask0 0x0 change to F1: 528MHz ch0 ttot10 ch1 ttot10 ch2 ttot10 ch3 ttot10 change to F2: 1068MHz ch0 ttot12 ch1 ttot12 ch2 ttot12 ch3 ttot12 change to F3: 1560MHz ch0 ttot14 ch1 ttot14 ch2 ttot14 ch3 ttot14 change to F0: 2112MHz ch0 ttot16 ch1 ttot16 ch2 ttot16 ch3 ttot16 out U-Boot SPL board init U-Boot SPL 2017.09-ge4e124926e-230922 #lxh (Sep 25 2023 - 10:58:38), fwver: v1.13 unknown raw ID 0 0 0 unrecognized JEDEC id bytes: 00, 00, 00 Trying to boot from MMC2 SPL: A/B-slot: _a, successful: 0, tries-remain: 7 Trying fit image at 0x4000 sector ## Verified-boot: 0 ## Checking atf-1 0x00040000 ... sha256(b5946ac63d...) + OK ## Checking uboot 0x00a00000 ... sha256(0340cf8050...) + OK ## Checking fdt 0x00b467c0 ... sha256(036cca5880...) + OK ## Checking atf-2 0xfdcc1000 ... sha256(b8dca786b4...) + OK "Error" handler, esr 0xbe000011 ELR: 8388 LR: 352c ESR: be000011 (ec=47) x 0: 00000000fdcc1000 x 1: 0000000003f70fc0 x 2: 000000000000a000 x 3: 0000000000000060 x 4: 000000000000a000 x 5: 0000000000001400 x 6: 6b01001f72a17f61 x 7: 0000000000024e08 x 8: 0000000000000338 x 9: 000000000000000c x10: 0000000003f5f95c x11: 00000000001fefc0 x12: 00000000000003b0 x13: 0000000003f5fa1c x14: 00000000001fefc0 x15: 0000000003f5fa1c x16: 000000000000000c x17: 0000000000000001 x18: 0000000003f5fe30 x19: 00000000001fefc0 x20: 0000000000000298 x21: 0000000000000050 x22: 0000000003f5fc68 x23: 0000000003f5fbe0 x24: 0000000000004000 x25: 0000000003f70fc0 x26: 0000000000000000 x27: 0000000000000000 x28: 00000000001fffc0 x29: 0000000003f5fa90 Call trace: PC: \[\< 00008388 \>

LR: [< 0000352c >]

Stack:

\< 00008388 \>

Copy info from "Call trace..." to a file(eg. dump.txt), and run

command in your U-Boot project: ./scripts/stacktrace.sh dump.txt spl

Resetting CPU ...

ERROR ### Please RESET the board

Reset the board to bootrom