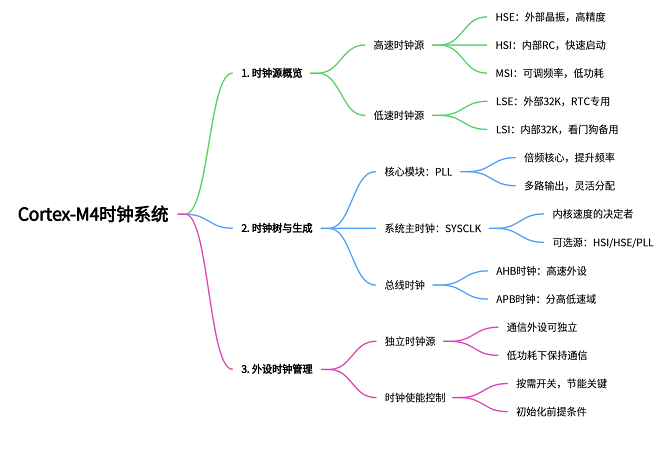

Cortex-M4内核的时钟系统是微控制器高效稳定运行的核心,其设计兼具灵活性与高性能,允许开发者根据应用需求精细配置。以下将基于搜索结果,从时钟源、时钟树结构、配置方法及注意事项等方面进行系统阐述。

一、 主要时钟源

Cortex-M4微控制器通常提供多个时钟源,以满足不同场景下对精度、速度和功耗的需求。主要可分为高速和低速两大类。

-

高速时钟源:

- 高速外部时钟 (HSE):由外部晶振或时钟源提供,频率范围通常在4MHz至26MHz(部分型号可达80MHz),精度高,是高性能应用的首选系统时钟源。

- 高速内部时钟 (HSI):芯片内部集成的RC振荡器,典型频率为16MHz。其启动快,但精度相对较低(例如±1%),常用于系统初始化和时钟备份。

- 主内部振荡器 (MSI):部分系列(如STM32L4)特有,是一个频率可调(如100kHz至48MHz)的内部振荡器,功耗与频率成正比,专为低功耗应用优化。

-

低速时钟源:

- 低速外部时钟 (LSE):通常连接32.768kHz晶振,为实时时钟(RTC)提供高精度、低功耗的时钟源,确保系统掉电后RTC仍能工作。

- 低速内部时钟 (LSI):内部RC振荡器,频率约为32kHz。主要用于独立看门狗(IWDG)和作为低精度RTC的备用时钟源。

二、 时钟树与系统时钟生成

时钟源通过一个复杂的"时钟树"进行管理和分配,最终为内核、总线和外设提供工作时钟。

- 锁相环 (PLL):这是提升系统时钟频率的关键模块。它可以将HSI或HSE等低频时钟进行倍频,生成更高频率的时钟。例如,STM32F4系列可通过PLL将外部8MHz晶振倍频至最高168MHz的系统时钟。PLL通常有多个输出,可分别用于系统时钟、USB(需精确48MHz)、音频接口等。

- 系统时钟 (SYSCLK):这是整个芯片的主时钟,直接决定Cortex-M4内核的运行速度。SYSCLK可以从HSI、HSE或PLL的输出中选择。其最大频率受芯片工艺限制,例如STM32F4系列最高为168MHz。

- 总线时钟 :SYSCLK经过分频后,产生不同总线域的时钟:

- AHB总线时钟 (HCLK):用于高速外设,如内存、DMA和大部分GPIO。其最大频率通常与SYSCLK相同(如168MHz)。

- APB总线时钟:分为高速APB2和低速APB1。HCLK经过预分频后得到它们,分别用于连接不同速度的外设。例如,在STM32F4中,APB2最大频率为84MHz,APB1最大频率为42MHz。

三、 外设时钟分配与灵活性

时钟系统的灵活性不仅体现在时钟源选择上,还体现在对外设时钟的独立管理上。

- 独立时钟源:许多通信外设(如USART、I2C、USB)可以不依赖于系统时钟,而由独立的时钟源驱动。这允许在降低系统主频以节省功耗时,仍能保持通信波特率的稳定。

- 时钟使能控制:每个外设通常都有独立的时钟使能位。在初始化外设前必须先开启其时钟,对于不用的外设则可以关闭其时钟以降低功耗。

四、 配置方法与工具

配置时钟系统是嵌入式开发的关键步骤,主要有两种方式:

- 直接寄存器编程:通过读写复位与时钟控制(RCC)模块的相关寄存器来完成。一般步骤包括:使能目标时钟源(如HSE)并等待其稳定;配置PLL的倍频(N)、分频(M、P、Q)参数并开启PLL;选择PLL输出作为SYSCLK;最后配置AHB、APB等总线分频器。这种方式需要对芯片手册和寄存器有深入了解。

- 使用图形化工具 (如STM32CubeMX):这是更高效的方法。开发者可以在图形界面上选择时钟源,设置期望的系统频率、USB频率等,工具会自动计算并配置PLL参数,生成初始化代码,极大简化了配置过程。

五、 关键注意事项

- 频率限制:必须严格遵守数据手册中规定的各时钟域最大频率限制,如SYSCLK、HCLK、PCLK1、PCLK2等,超频可能导致系统不稳定。

- 时钟安全:部分芯片提供时钟安全系统(CSS),当HSE时钟失效时,可自动切换到HSI,防止系统因外部晶振故障而挂起。

- 低功耗管理:时钟控制器是功耗管理的关键。通过关闭不使用的外设时钟、选择低速时钟源以及让CPU进入睡眠模式(执行WFI指令)等方式,可以显著降低系统功耗。

总结而言,Cortex-M4的时钟系统是一个高度可配置的引擎。理解其时钟源、时钟树结构和配置原则,是充分发挥芯片性能、实现功耗与效能平衡的基础。无论是追求极致性能还是超低功耗,都可以通过灵活的时钟配置来实现。