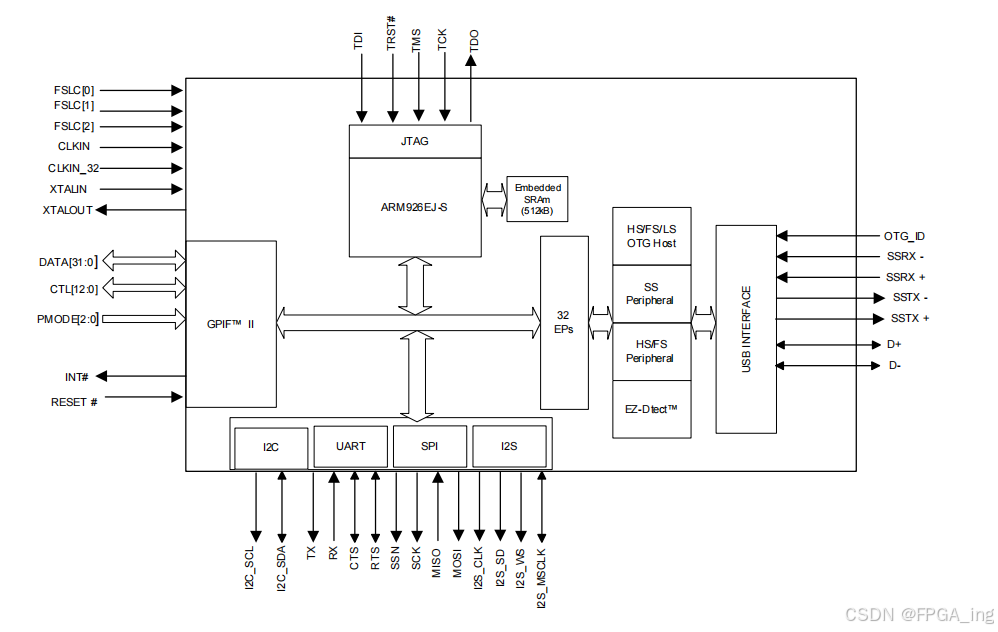

赛普拉斯 EZ-USB FX3 为一款USB3.0外设控制器,拥有一个可进行完全配置的并行通用可编程接口GPIF II,可与FPGA连接。

通用可编程接口 GPIF II 总线位宽有32/16/8位总线,最大速度 100MHz,其控制信号可配置;

外设接口有 I2C、I2S、UART、SPI;

逻辑框图:

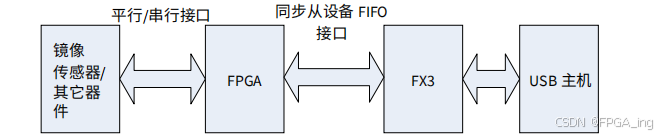

因为该芯片焊接在FPGA开发板上,所以需要使用FPGA控制的管脚只有GPIF II接口管脚,用户需要做GPIF II接口的编程;

FPGA 通过 GPIF II接口传递数据给FX3,FX3内部将数据打包成带有USB3.0协议的数据包,通过USB 标准接口对外传输;所以只需要按照FX3 芯片的要求编写时序,即可将数据传输到USB3.0 接口的主机上。

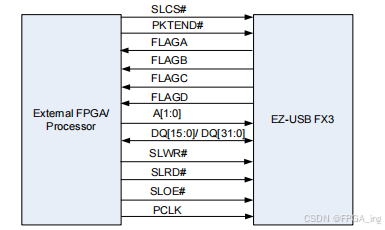

GPIF 接口:

FPGA为主设备,GPIF II为从设备,GPIF II选择同步从设备FIFO 接口模式进行使用;

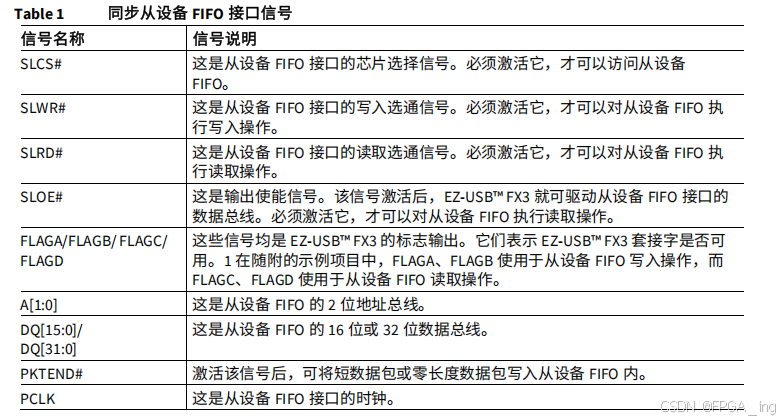

同步从设备FIFO接口:

DQ:从FX3写数据或者从FX3读数据都是共用这一个DQ 数据线,半双工模式;

读写带宽: 100M x 32bit = 3.2Gbps,为最大支持的通信带宽;

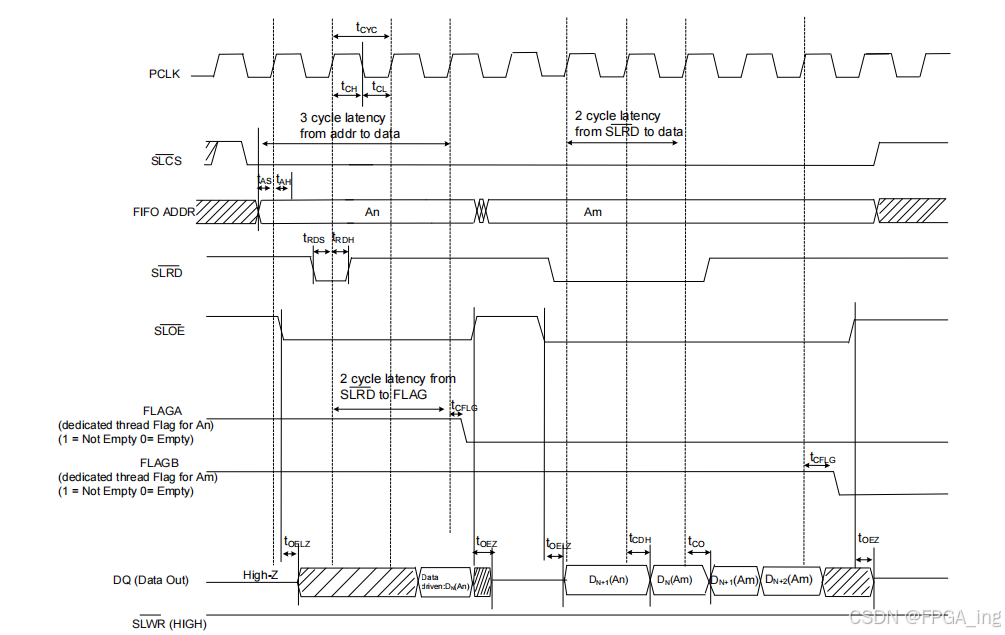

GPIF II同步从设备 FIFO 接口读时序:

读取操作:

时钟PCLK稳定保持;

地址A稳定且SLCS信号被激活,表示地址和芯片选中;

激活SLOE,其为一个使能信号,使能后可以驱动数据总线DQ;

激活SLRD,激活后根据时序,在数据输出有效时取走;

关于读时序:

在操作第一拍,SLCS拉低,地址FIFO ADDR赋值,SLOE拉低;第二拍SLRD拉低读取数据DQ;

地址稳定有效到数据能输出延时3个时钟周期,SLRD拉低激活到该数据能输出间隔2个时钟周期;

FLAGA和FLAGB被分别配置为An 地址和Am 地址的空标志,所以数据读空后就拉低,

同时,SLRD与FLAG拉低之间间隔了两个时钟周期;

读操作完毕后,就可以将SLCS、SLOE拉高,SLRD的控制最好是根据后续配置的FLAG状态进行判断,有多少可读的数据就拉低多少拍;

对于读时序图,通道被读空后有2个时钟周期的延迟,空标志才会更新;

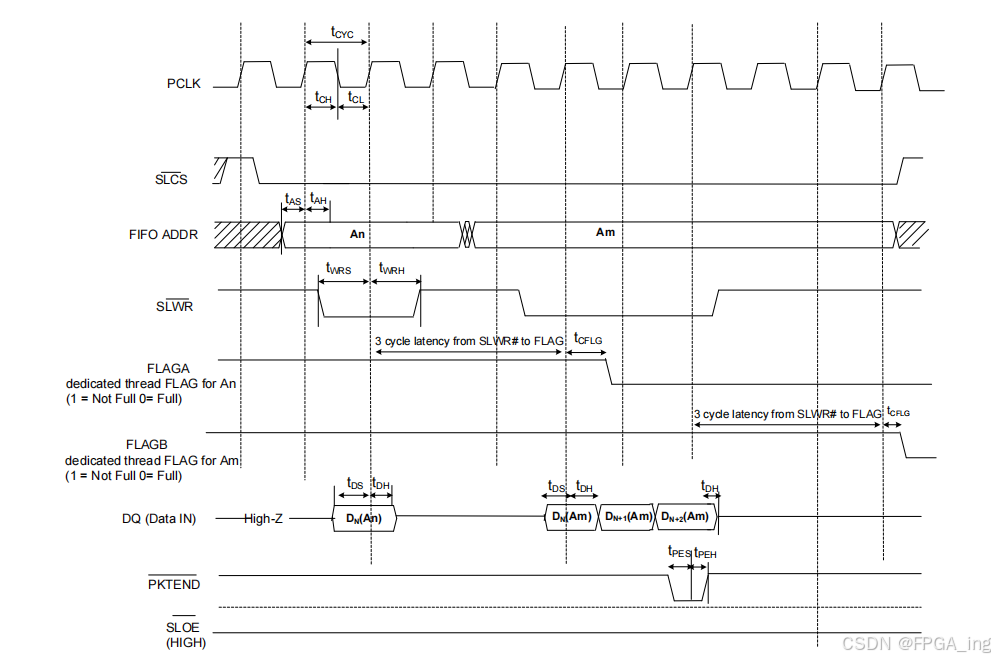

GPIF II同步从设备 FIFO 接口写时序:

写入操作:

时钟PCLK稳定保持;

地址A稳定且SLCS信号被激活,表示地址和芯片选中;

外部主设备将数据输出到数据总线上;

激活SLWR 的同时将写数据放到 DQ总线上,数据将被写入FIFO中,FIFO指针在PCLK上升沿变化,FIFO的满标志将会更新;

关于写时序:

激活片选信号,地址稳定,拉低写使能SLWR,同时将数据放入数据总线DQ上,写入到FIFO,

并监测FLAG信号,判断FIFO为空再写,避免出现写溢出问题;

当两个FLAG 在一个地址时,都同时服务于该地址,如果地址是写通道,就配置为满标志和几乎满标志;如果是读通道,就配置为空标志和几乎空标志;

在写操作的最后一排将 PKTEND拉低,科技标志本次写入的结束;写短数据包时,在写入SLWR拉低的最后一拍拉低PKTEND,然后退出写状态即可正常写入该短包;

包长度由FX3固件配置,当缓冲区长度设置为1024,那写长度低于1024的数据包,均为短数据包;

写短数据包时,PKTEND 必须在最后一拍拉低,不然FX3会一直等待下一拍数据而导致卡在这里;

当写长度等于缓冲区长度的数据包,其最后一拍的PKTEND 可拉低也可不拉低,因在这种情况下写入数据,最后一拍数据刚好填满缓冲区,FX3本次写结束,也不再接收后续数据;

零长度写入包,不写入数据,SLWR不需要拉低,只需要工作时拉低一拍PKTEND即可;

通道被写满后有3个时钟周期的延迟,满标志(FLAGB)才会更新;

当主设备对同步从设备FIFO 进行写入时:

时钟沿到来采集到激活的局部标志后,可写入的数据字的数量=水印值-4;

当设置写通道水印值设置为4,那么FPGA 在采集到激活的局部标志后,可写入的数据量就为0,所以在采集到几乎空满标志激活后,立即停止写入;

当主设备对同步从设备FIFO 进行读取时:

时钟沿到来采集到激活的局部标志后,可用于读取的数据字的数量=水印值-1;

读通到水印值设置为3,当FPGA 采集到激活的几乎空满标志后,可读取的数据量就为2,

但是SLRD激活到总线输出数据存在两个周期延迟,所以在采集到局部标志激活后,立即拉高SLRD停止读取,后续数据维持两拍输出;