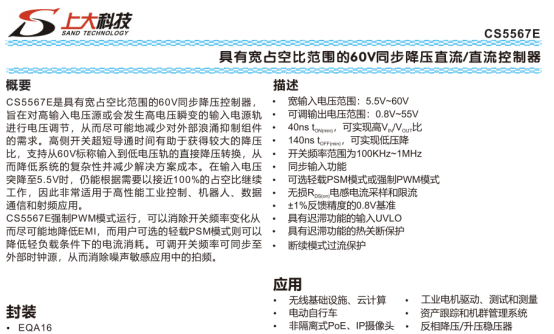

CS5567E是一款具有宽占空比范围的高性能同步降压控制器,输入电压范围5.5~60V,输出电压可调0.8~55V,适用于无线基础设施、云计算、工业电机驱动、电动自行车、IP摄像头及反相降压/升压稳压器等场景。采用EQA16封装,工作结温-40℃~125℃,环境温度-40℃~85℃,热阻45℃/W,底部带散热片,需搭配PCB散热设计保障高压大电流场景稳定运行。

核心特性突出,高侧开关最小导通时间仅40ns,支持高输入输出电压比,输入电压突降至5.5V时仍能以接近100%占空比工作;开关频率可通过外部电阻在100KHz~1MHz范围内调节,也可通过SYNCIN引脚与外部时钟同步,消除拍频噪声。提供轻载PSM模式(浮空或接地选择)与强制PWM模式(接VCC选择),PSM模式降低轻载功耗,强制PWM模式抑制EMI,适配不同噪声与功耗需求。

具备完善保护与控制功能:内置0.8V基准电压(精度±1%),支持无损电感电流采样和限流,ILIMIT引脚可编程电流限制阈值;输入欠压锁定(UVLO)带迟滞功能,175℃热关断保护(20℃滞回),断续模式过流保护(打嗝模式),保障系统可靠运行。支持软启动与电压跟踪功能,软启动时间通过SST引脚电容可调,跟踪功能适配主从电源同步需求,满足DSP、FPGA等设备的内核与I/O电压跟踪场景。

一 CS5567的特性

宽输入电压范围:5.5V~60V

可调输出电压范围:0.8V~55V

40ns ton(min)可实现高Vin/Vout比

140ns toff(min)可实现低降压

开关频率范围为100KHz~1MHz

同步输入功能

可选轻载PSM模式或强制PWM模式

无损Rds(on)电流采样和限流

±1%反馈精度的0.8V基准

具有迟滞功能的输入UVLO

具有迟滞功能的热关断保护

断续模式过流保护

二 CS5567的应用信息

1 典型应用图

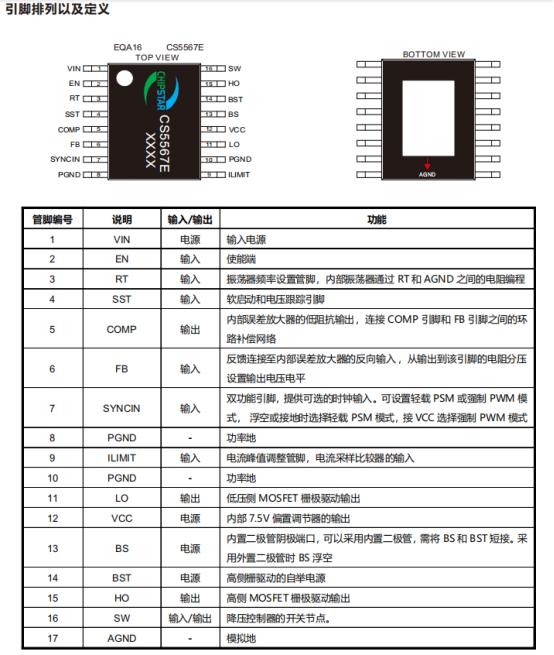

2 引脚排列及定义

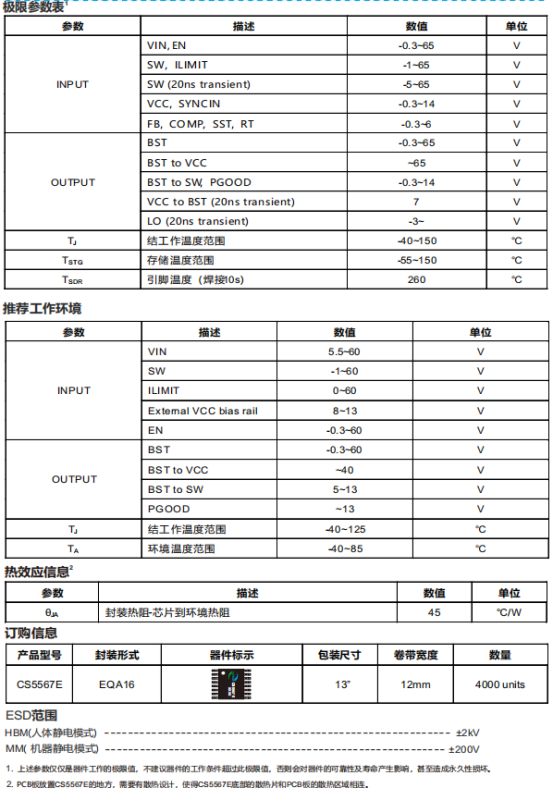

3 基础参数