Xilinx 7 系列 FPGA 包括三个家族:Artix-7、Kintex-7 和 Virtex-7,它们共享相同的 CLB 架构。这个架构与 Virtex-6 FPGA 的 CLB 相同,但与 Spartan-6 有些差异,主要是列式架构且只保留 SliceL 与 SliceM 类型单元。本文主要介绍 Xilinx 7 系列 FPGA 中的可配置逻辑块(CLB)的架构、功能与设计方法。

(图片由 Nano Banana Pro 生成)

目录

[1 CLB 概述与架构特点](#1 CLB 概述与架构特点)

[2 Slice 核心功能模块](#2 Slice 核心功能模块)

[2.1 查找表](#2.1 查找表)

[2.2 时序单元](#2.2 时序单元)

[2.3 分布式 RAM](#2.3 分布式 RAM)

[2.4 移位寄存器](#2.4 移位寄存器)

[2.5 多路复用器](#2.5 多路复用器)

[2.6 进位链](#2.6 进位链)

[3 开发指南与建议](#3 开发指南与建议)

1 CLB 概述与架构特点

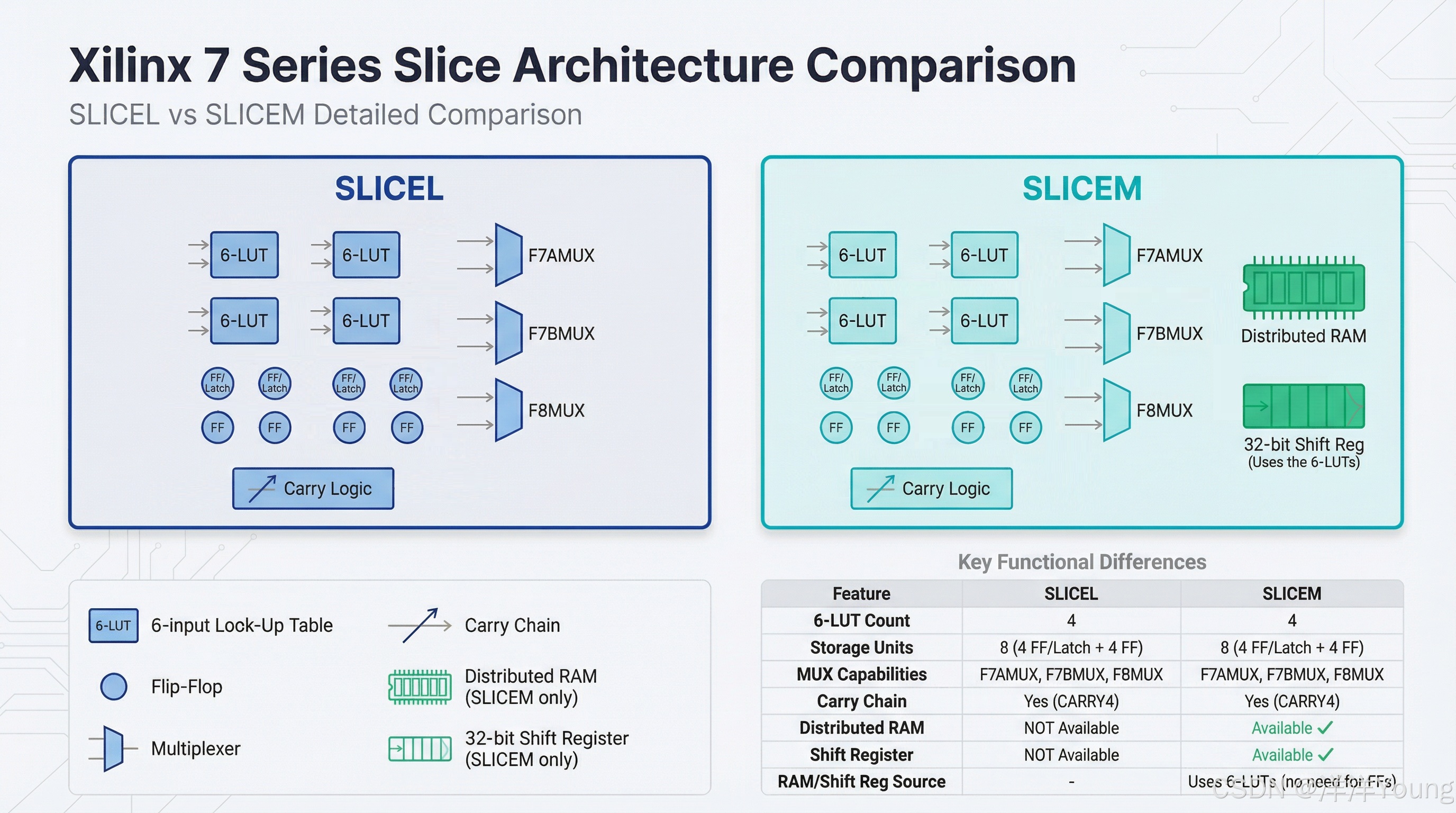

Xilinx 7 系列 FPGA 包括三个家族:Artix-7、Kintex-7 和 Virtex-7,它们共享相同的 CLB 架构。这个架构与 Virtex-6 FPGA 的 CLB 相同,但与 Spartan-6 有些差异,主要是列式架构且只保留 SliceL 与 SliceM 类型单元。

CLB 是 FPGA 的主要逻辑资源,主要用于实现组合与时序逻辑。CLB 由一对切片(Slice)组成。

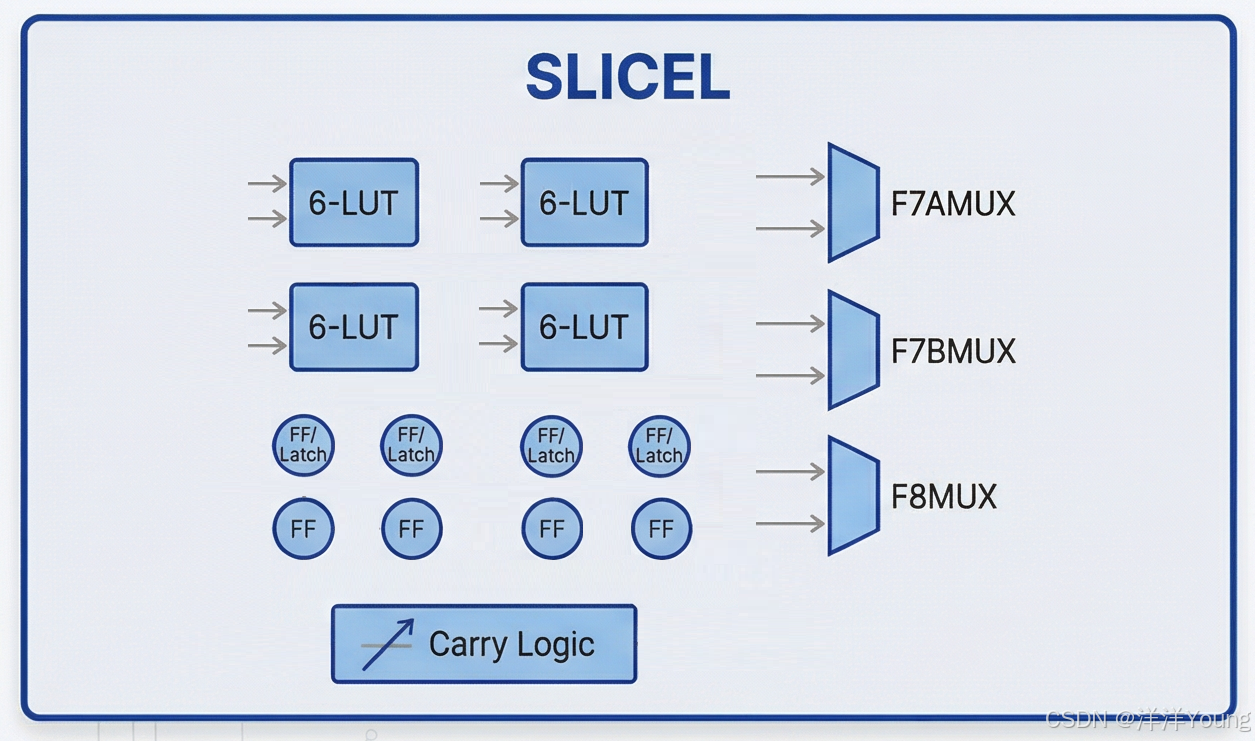

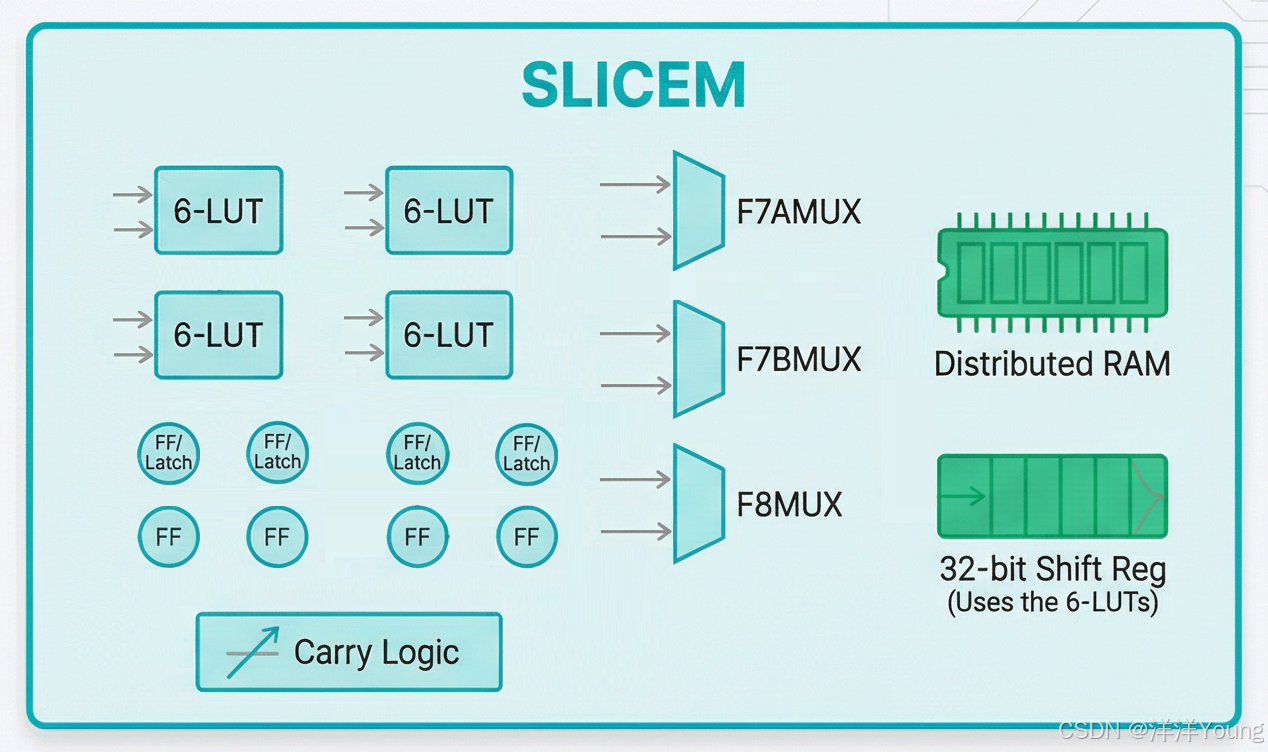

切片类型:

- SLICEL:仅支持逻辑、进位、ROM

- SLICEM:除 SLICEL 功能外,还支持分布式 RAM 和移位寄存器

2 Slice 核心功能模块

2.1 查找表

Xilinx 7 系列器件使用 6 输入 LUT 架构,LUT 可配置为一个 6 输入函数或两个 5 输入函数(共享地址),同时 LUT 还用于实现分布式RAM(仅 SliceM)和移位寄存器(仅 SliceM)。

实现更多输入的组合逻辑,需要使用多路复用器资源。例如 6-LUT 与 F7MUX 组合可以实现 7 输入的 LUT;6-LUT 与 F7MUX、F8MUX 组合可以实现 8 输入的 LUT。

2.2 时序单元

每个 SliceL 或 SliceM 都包含 8 个时序单元,这些时序单元主要用于实现时序逻辑,可配置为:8 个 1-bit 寄存器,或者 4 个 1-bit 锁存器(此时另外 4 个无法使用)。

时序单元支持同步置位、同步复位、异步置位或异步复位。置位或复位逻辑只能选择其一。同时,SliceL 或 SliceM 内部的时序单元共享控制信号(包括 CLK、CE、SR)。

2.3 分布式 RAM

LUT 可配置为小型同步写、异步读 RAM

支持多种配置:

- 单端口(32×1 至 256×1)

- 双端口、四端口、简单双端口

- 适用于小容量、低延迟存储

2.4 移位寄存器

LUT 可配置为 32位移位寄存器

- 可通过级联实现最长128位移位链

- 支持动态读地址,可异步读取任意位

2.5 多路复用器

7 系列器件提供了丰富的多路复用器(MUX)资源

- 支持 4:1、8:1、16:1 MUX

- 使用专用 MUX(F7AMUX、F7BMUX、F8MUX)组合 LUT 输出

2.6 进位链

- 专用快速进位链,用于高效实现加法、减法、计数器

- 每个切片有两个独立进位链,可垂直级联

3 开发指南与建议

推荐设计流程:

- 使用通用 HDL 编写代码,让综合工具自动推断 CLB 资源

- 尽量使用流水线提升性能

- 控制信号尽量少用,避免同时使用 set 和 reset

- 优先使用 SRL 或分布式 RAM 实现小存储/移位功能

注意事项:

- CLB 触发器只能有 set 或 reset,不能同时使用

- 控制信号共享于切片内,尽量减少唯一控制信号数量

- 进位链沿列垂直级联,影响布局

- 在 SSI 设备中,进位链不能跨越 SLR