文章目录

- [1. 逻辑波形和实际波形](#1. 逻辑波形和实际波形)

- [2. 频率提升带来的改变](#2. 频率提升带来的改变)

- [3. 信号完整性问题的本质起因](#3. 信号完整性问题的本质起因)

1. 逻辑波形和实际波形

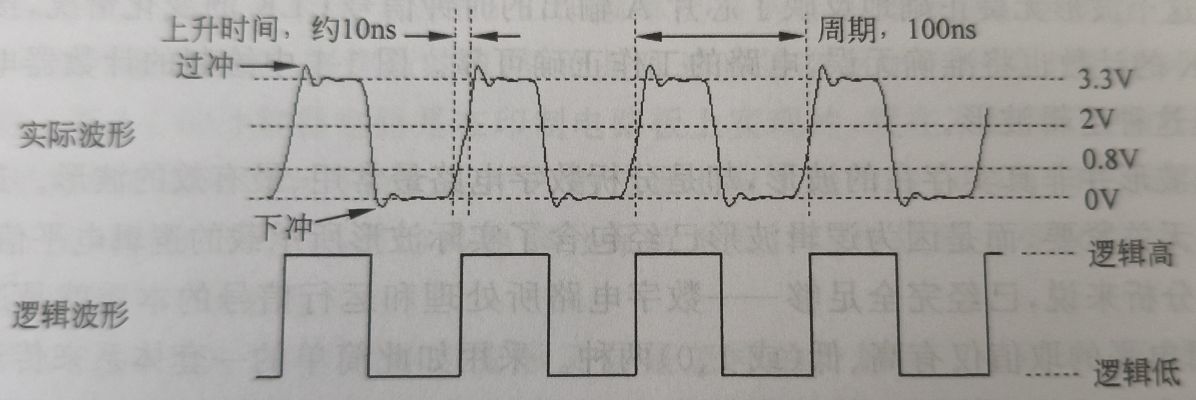

10MHz 时钟信号的波形:

逻辑波形 :理想高电平电压是 3.3V ,理想低电平电压是 0V。

实际波形 :信号在处于高、低电平状态时的电压并不与 3.3V 和 0V 完全重合,特别是在信号经由上升沿到达 3.3V 和经由下降沿到达 0V 之后,会继续向上、向下超出一小段幅度,然后经过几次振荡,才会与 3.3V 和 0V 电压相吻合,超出的部分被称为过冲 和下冲。

上升时间被定义为信号从满伏电压的 10% 爬升到 90% 所经历的时间,下降时间反之,10MHz 时钟信号的上升时间约为 10ns。

电路正常工作的基本前提是接收端能够正确地从波形中识别出发送端输出的逻辑电平。

VIH (例如: 2V):逻辑高电平的最低输入电压 。

VIL (例如: 0.8V):逻辑低电平的最高输入电压。

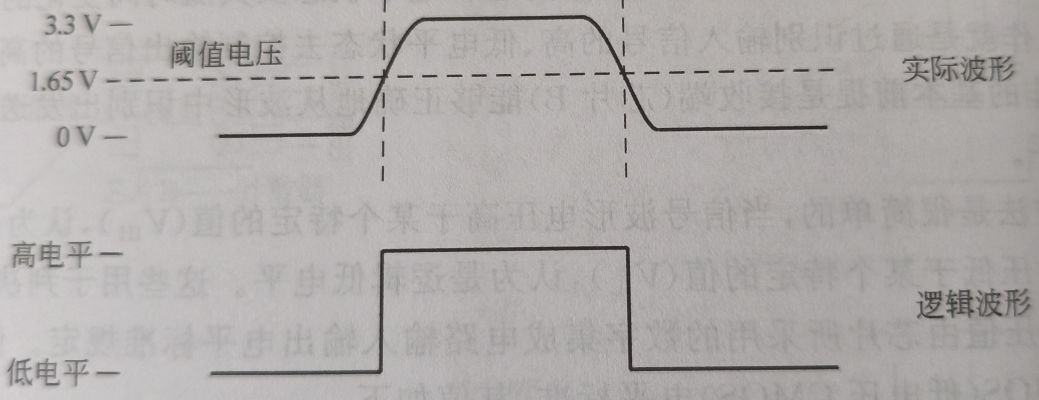

阈值电压 :芯片器件对于输入信号高、低逻辑电平的判定存在的一个临界电压值,一般是电源电压的一半。

2. 频率提升带来的改变

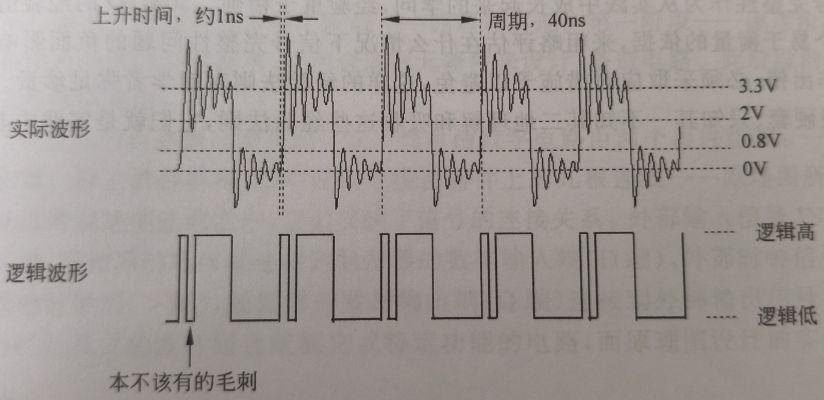

25MHz 时钟信号的波形:

- 时钟周期被缩短到 40ns。

- 上升时间缩短到 4ns。

- 振荡加剧,过冲和下冲的幅度加大。

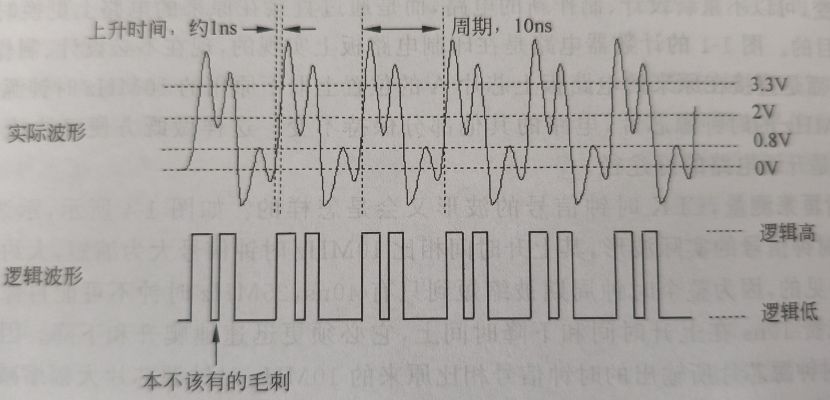

100MHz 时钟信号的波形:

- 波形失真严重,信号电压在经历了上升沿后的第一个过冲向下回落时掉到了 VIH 和阈值电压之下,所以出现了一段短暂的低电平毛刺。

造成信号波形振荡的原因是一种被称作反射的现象,这个现象在每个时钟波形中都存在,只是引起的振荡幅度有大有小。

3. 信号完整性问题的本质起因

- 数字信号越来越快的上升、下降时间,而非频率。

上升时间为 1ns 的 25MHz 时钟信号波形:

- 这个 25MHz 时钟信号波形的过冲,下冲和振荡幅度依然很大,并且在高电平半周期内出现了毛刺现象。

一个经常使用的经验判断标准:数字电路中信号的工作频率大于 50MHz 就是高速电路。

随着电路工作频率的不断提升,信号周期越来越短,上升时间也越来越快。