文章目录

- 前言

- 一、N型三极管基极加下拉电阻

- 二、P型三极管基极加上拉电阻

- 三、三极管的最大耐压

-

- [1. 分析电路中三极管的 "实际最大极间电压"](#1. 分析电路中三极管的 “实际最大极间电压”)

- [2. 选择三极管的耐压参数(优先看 VCEO)](#2. 选择三极管的耐压参数(优先看 VCEO))

- 总结

前言

在实际场景中,会存在信号的干扰导致实际环境中的电平不确定性,因此实际硬件电路中,三极管基极加上下拉电阻,核心是解决实际环境中的电平不确定性问题,确保三极管稳定工作、避免硬件损坏,是保障电路可靠性的必备设计

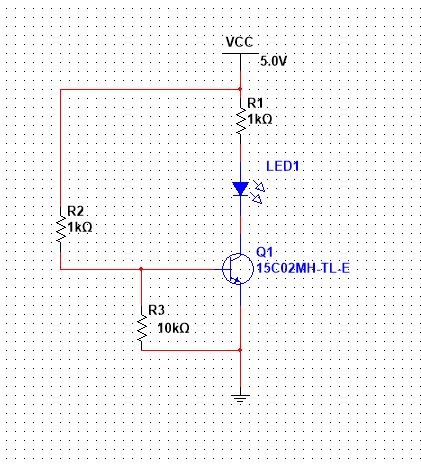

一、N型三极管基极加下拉电阻

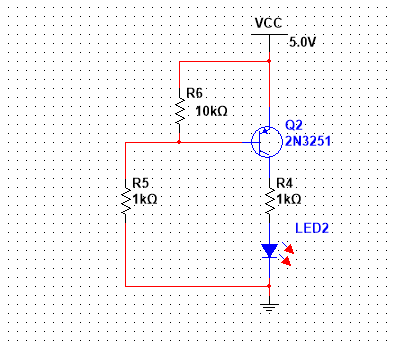

二、P型三极管基极加上拉电阻

三、三极管的最大耐压

实际选型时主要是看Vce之间的反向电压

1. 分析电路中三极管的 "实际最大极间电压"

重点关注三极管截止时的集电极 - 发射极电压(VCE):

三极管在 "截止状态" 时,集电极通常直接接电源(或负载电源),此时电源电压会几乎全部加在集电极→发射极之间,这是电路中 VCE 的最大值。

eg:

若电路中三极管集电极接 12V 电源,负载是 LED / 继电器,三极管截止时 VCE≈12V,这就是实际最大工作电压。

2. 选择三极管的耐压参数(优先看 VCEO)

要求:三极管的 VCEO ≥ 实际最大工作电压 + 安全余量。

安全余量一般留 20%~50%(防止电源波动、负载尖峰电压);

若负载是感性负载(电机、继电器):

断开时会产生 "反向电动势尖峰"(比如 12V 电源可能产生 20V 以上尖峰),此时 VCEO 需覆盖尖峰电压(或额外加续流二极管,但三极管耐压仍需留足余量)。

总结

基极上下拉电阻设计:

- 因实际电路易受干扰导致电平不确定,需为 N

型三极管基极加下拉电阻、P型三极管基极加上拉电阻,以此稳定基极电平、避免误触发,保障三极管工作状态可靠。

最大耐压选型:

- 聚焦三极管截止时集电极 -发射极的实际最大电压(VCE),选型优先参考 VCEO 参数,要求其不小于 "实际最大工作电压 + 20%~50%安全余量";若负载是电机等感性负载,还需覆盖其断开时的反向电动势尖峰。