ALIENTEK-ALPHA EMMC开发板移植uboot Linux buildroot(二)

1. 编译环境及源码版本

1.uboot-imx-v2022.04

2.linux-imx-lf-5.15.y

3.buildroot-2025.02.8

4.Ubuntu-18.04.6

2. 移植Linux到ALIENTEK-ALPHA EMMC开发板

2.1. Linux文件简介

移植Linux之前需要先知道uboot每个目录下存放文件的用途,Linux目录下文件的用途说明如下表所示:

| 目录 | 用途说明 |

|---|---|

| arch | 架构相关的目录 |

| block | 块设备相关目录 |

| crypto | 加密相关目录 |

| Documentation | 文档相关目录 |

| drivers | 驱动相关目录 |

| firmeare | 固件相关目录 |

| fs | 文件系统相关目录 |

| include | 头文件相关目录 |

| init | 初始化相关目录 |

| ipc | 进程间通信相关目录 |

| kernel | 内核相关目录 |

| lib | 库相关目录 |

| mm | 内存管理相关目录 |

| net | 网络相关目录 |

| samples | 例程相关目录 |

| scripts | 脚本相关目录 |

| security | 安全相关目录 |

| sound | 音频处理相关目录 |

| tools | 工具相关目录 |

| usr | 与 initramfs 相关的目录,用于生成initramfs |

| virt | 提供虚拟机技术(KVM) |

| certs | 存储了 认证 和 签名 相关代码 |

| COPYING | 版权声明 |

| CREDITS | Linux 贡献者 |

| Kbuild | Makefile 会读取此文件 |

| Kconfig | 图形化配置界面的配置文件 |

| MAINTAINERS | 维护者名单 |

| Makefile | Linux 顶层 Makefile |

| README | Linux 描述文件 |

Linux移植在ALIENTEK-ALPHA EMMC板子时,需要在以下几个目录中添加相应文件或修改某些文件:

1. 在arch/arm/configs目录下增加ALIENTEK-ALPHA EMMC板子配置文件

2. 在arch/arm/boot/dts目录下增加ALIENTEK-ALPHA EMMC板子设备树描述文件

2.2. 添加ALIENTEK-ALPHA EMMC开发板配置文件

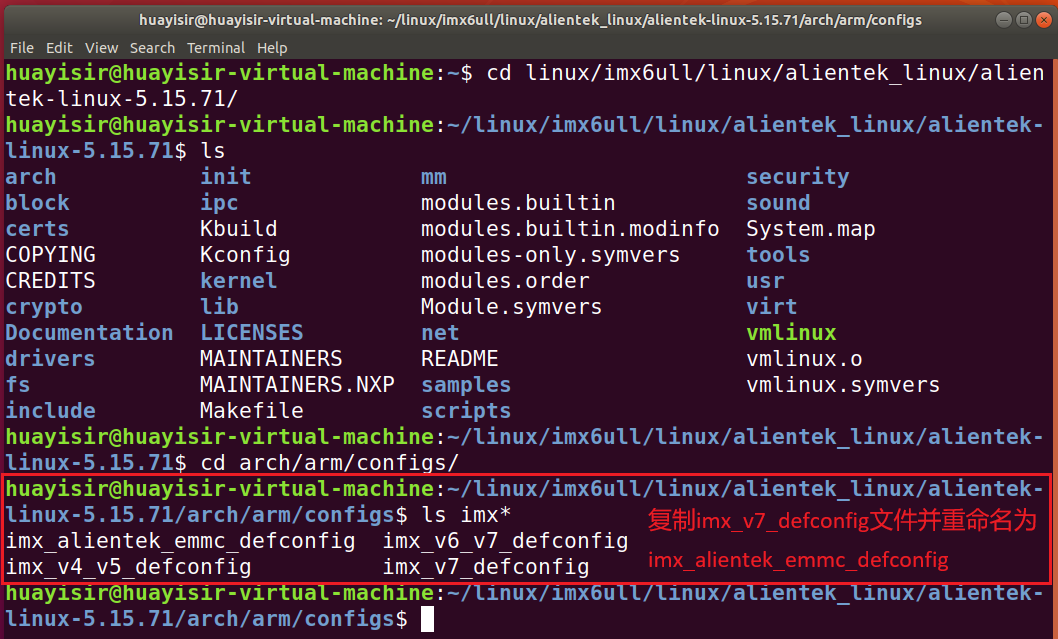

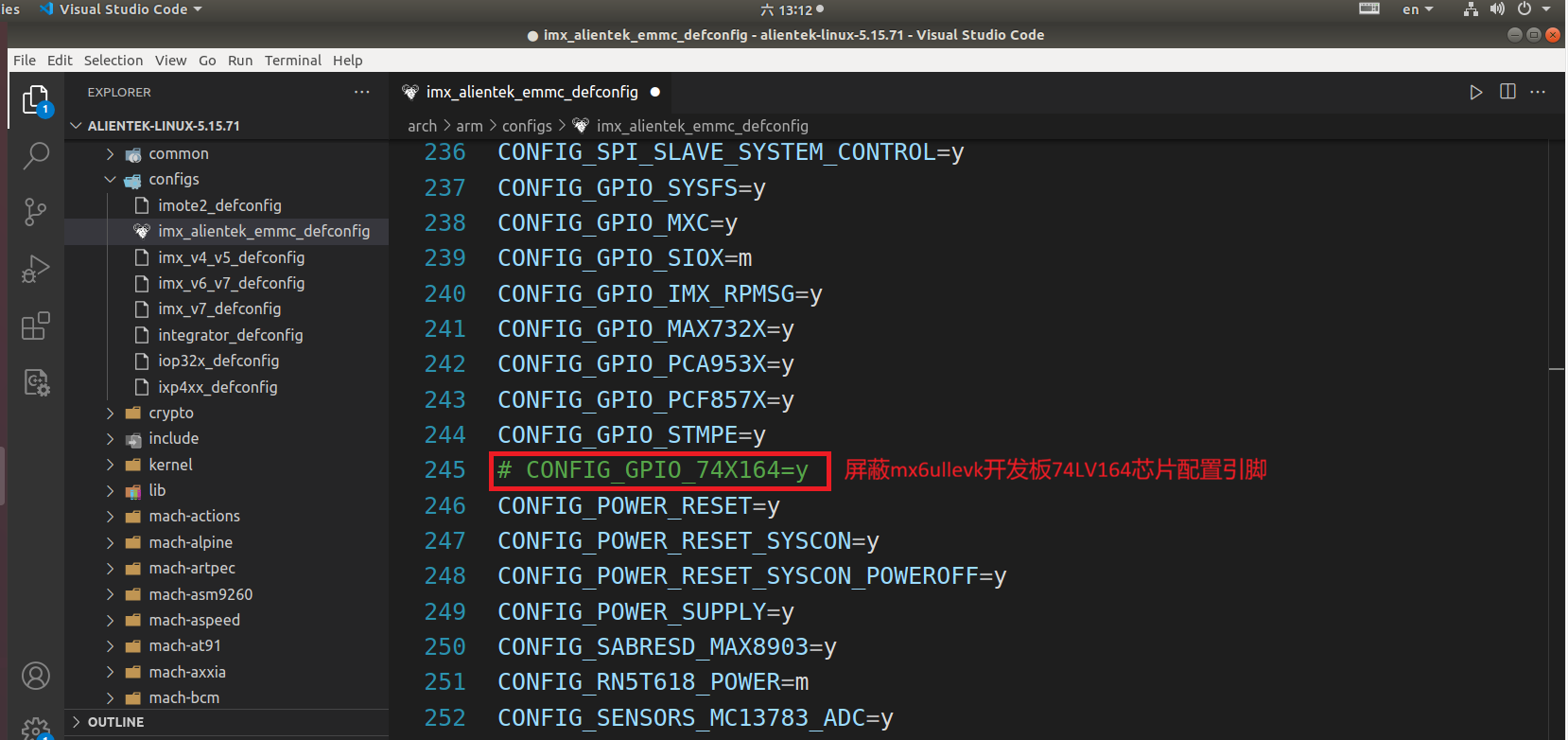

1.进入arch/arm/configs 目录下,复制imx_v7_defconfig 文件并重命名为imx_alientek_emmc_defconfig,如下图所示:

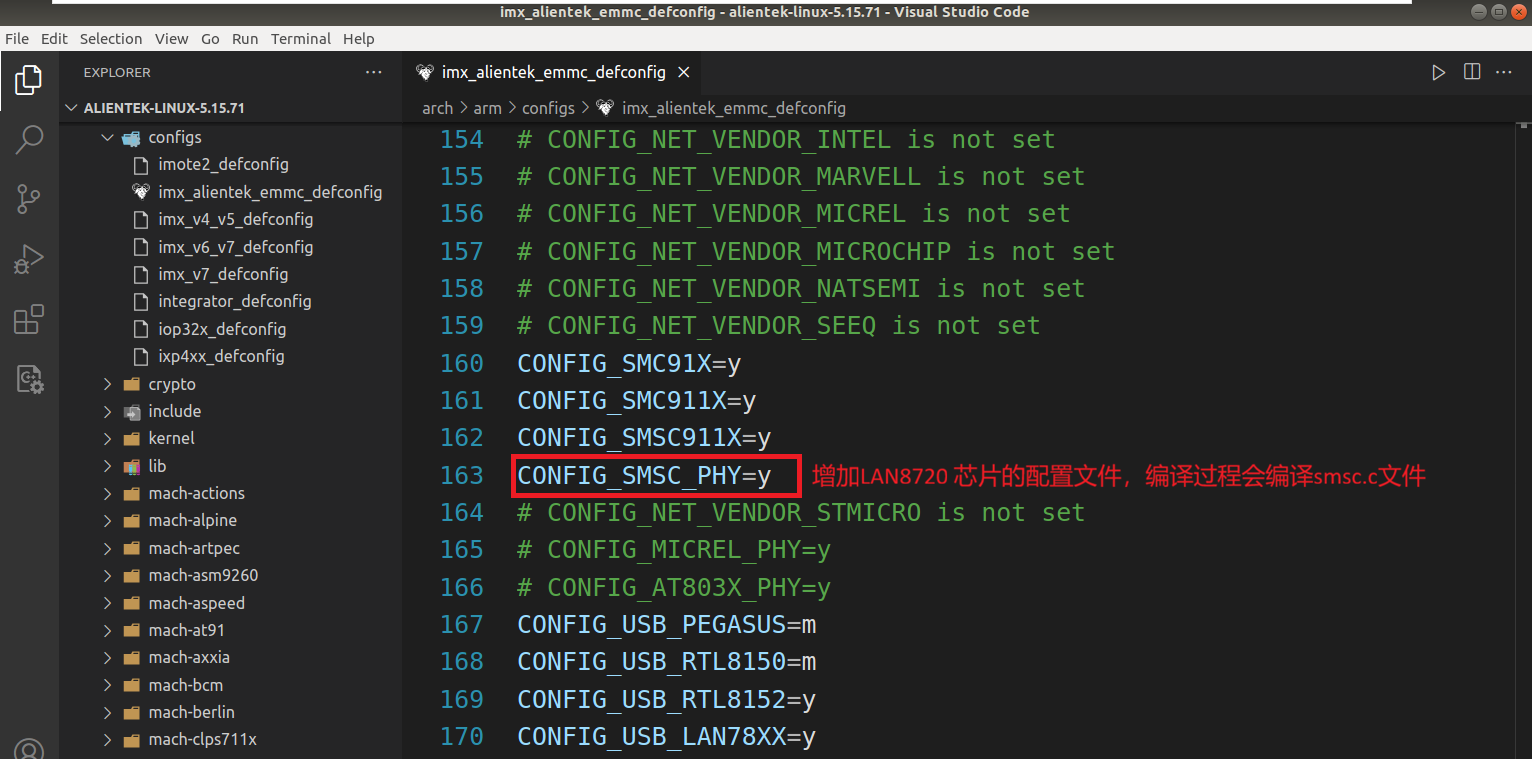

2.打开imx_alientek_emmc_defconfig文件,对该配置文件进行修改如下图所示:

2.3. 添加ALIENTEK-ALPHA开发板对应的设备树文件

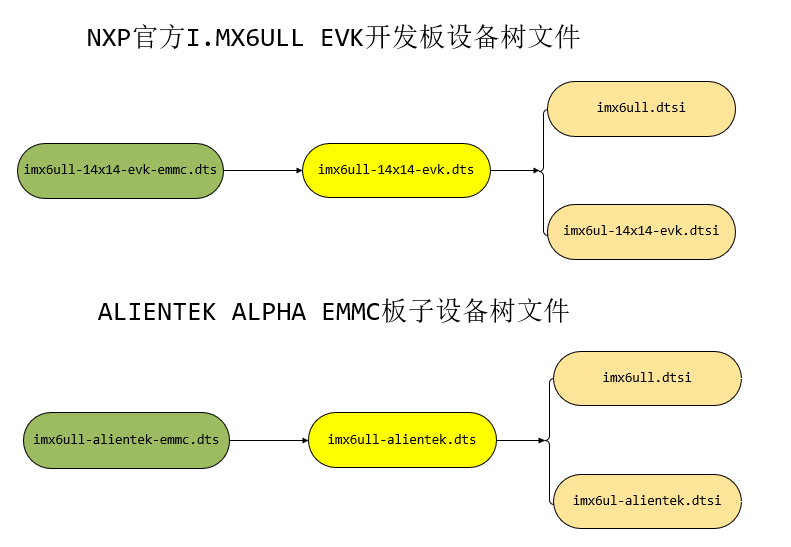

Linux 5.15.71版本使用了设备树描述设备,因此在移植Linux 5.15.71时需要添加ALIENTEK-ALPHA开发板的设备树文件,设备树描述文件存放在arch/arm/boot/dts目录下,因此在此目录下需要增加ALIENTEK-ALPHA开发板设备树描述文件。

NXP官方I.MX6ULL EVK开发板与ALIENTEK-ALPHA开发板设备树对照如下图所示:

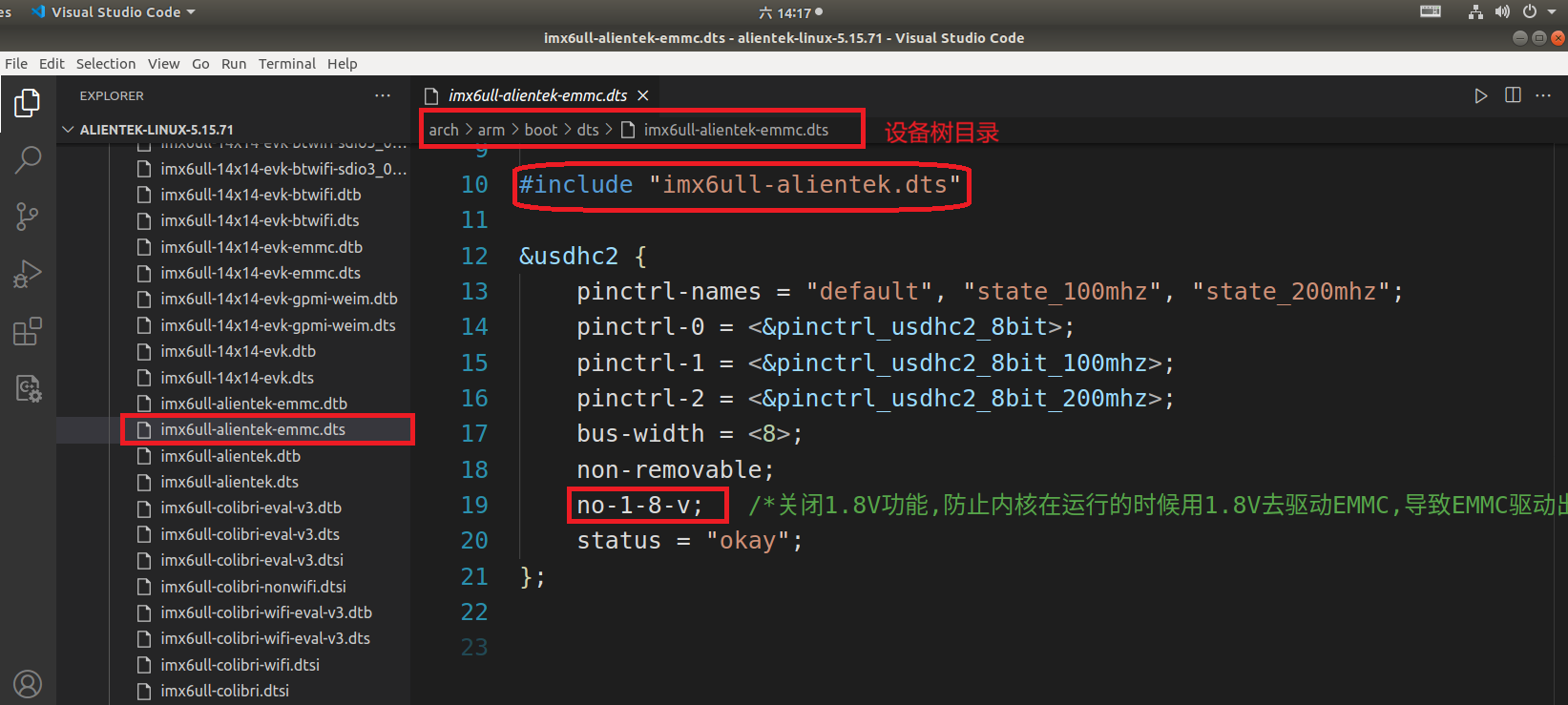

1.进入arch/arm/boot/dts 目录复制imx6ull-14x14-evk-emmc.dts 并重新命名为imx6ull-alientek-emmc.dts并修改如下图所示:

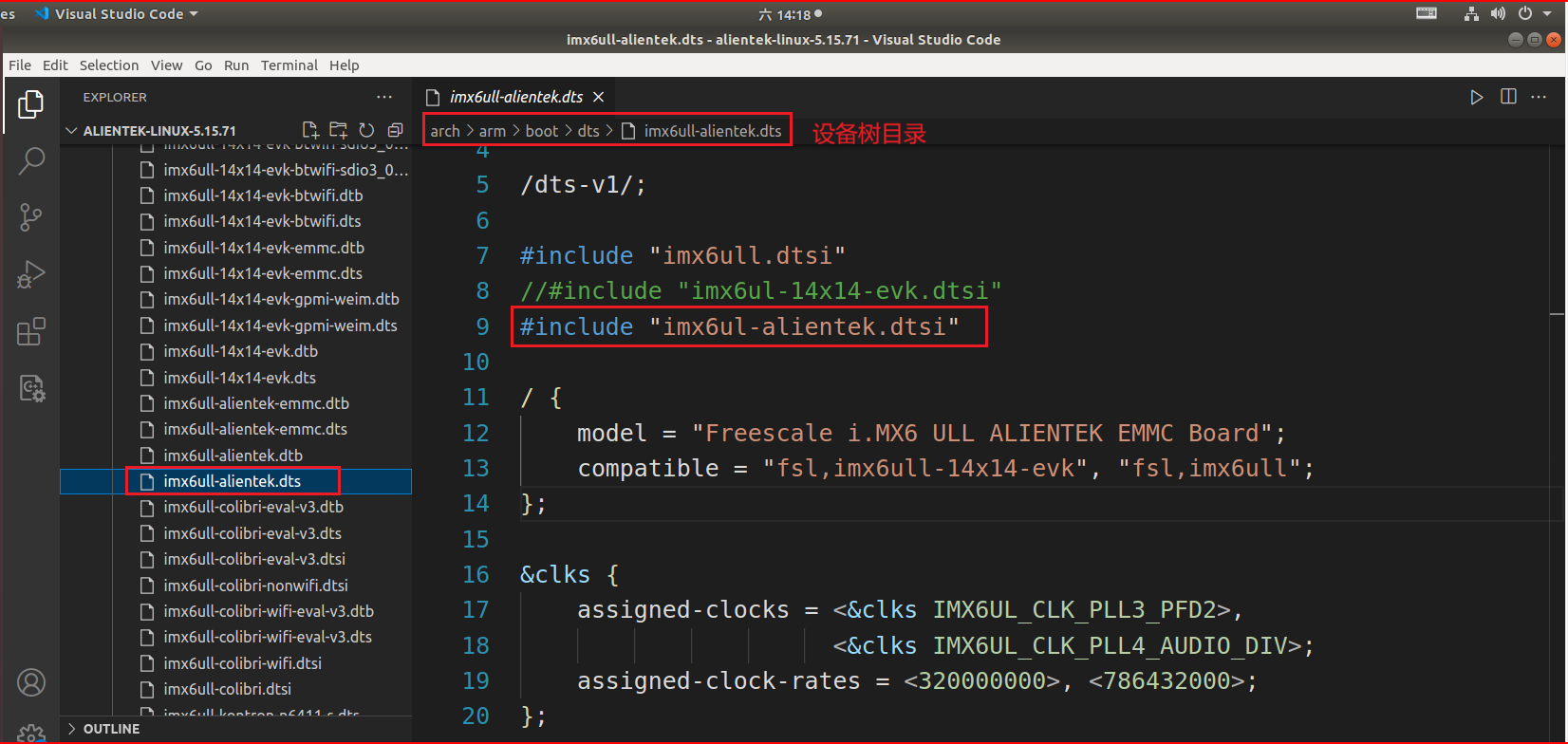

2.进入arch/arm/boot/dts 目录复制imx6ull-14x14-evk.dts 并重新命名为imx6ull-alientek.dts并修改如下图所示:

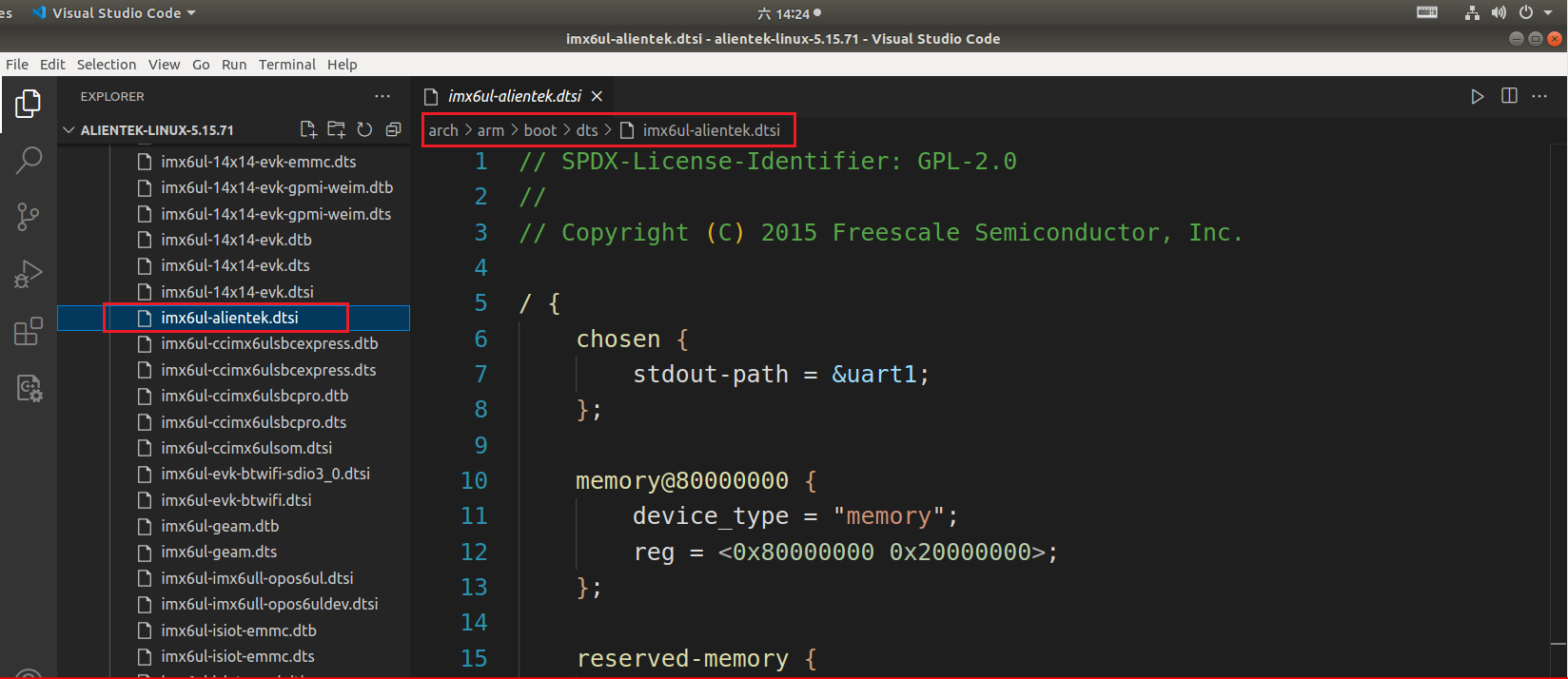

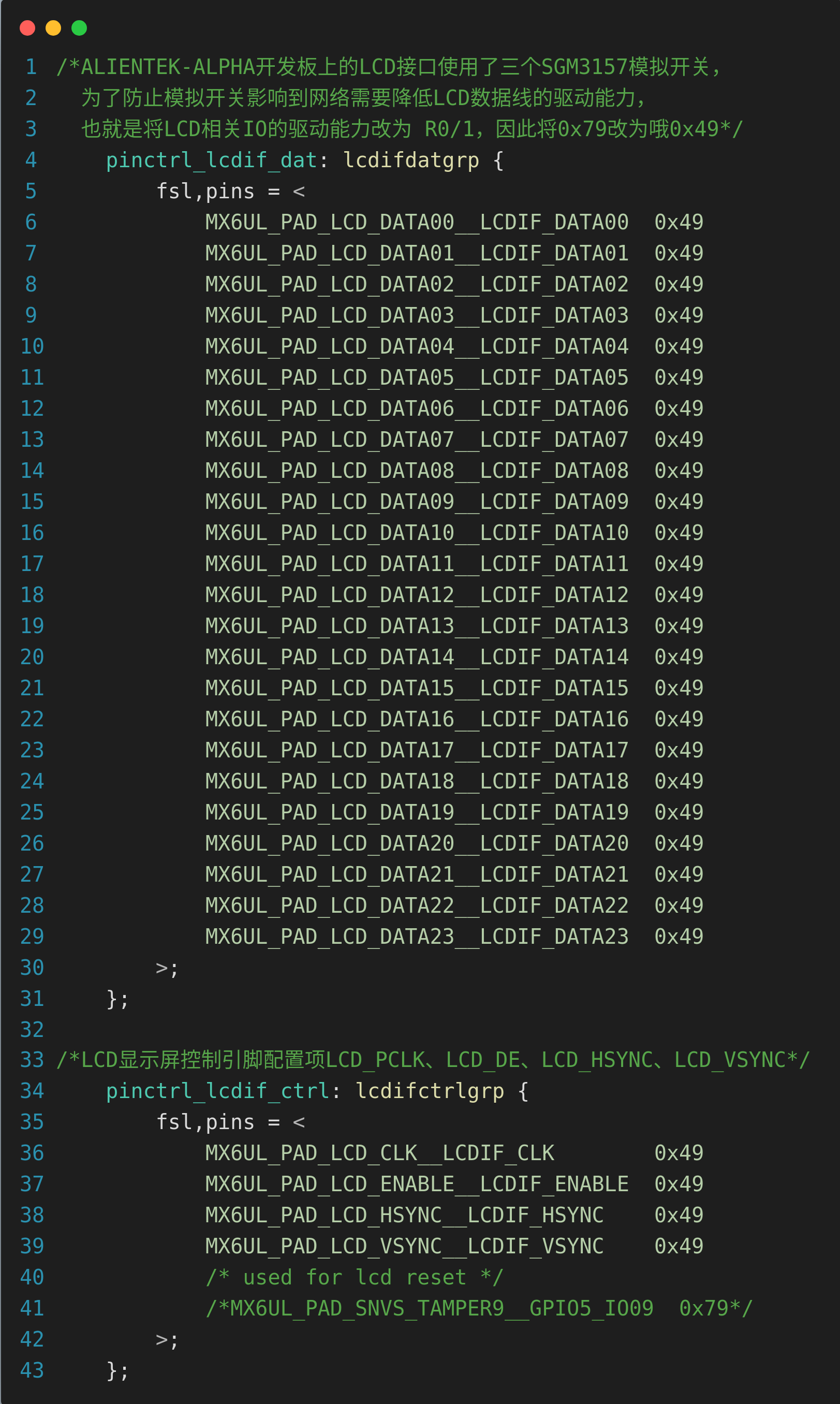

3.进入arch/arm/boot/dts 目录复制imx6ul-14x14-evk.dtsi 并重新命名为imx6ul-alientek.dtsi如下图所示:

4.查看arch/arm/boot/dts目录下查看imx6ul相关的设备树文件如下图所示:、

5.针对ALIENTEK ALPHA EMMC板载LCD和ENET网络修改,imx6ul-alientek.dtsi设备树文件,主要修改LCD驱动描述和ENET网络驱动描述修改。

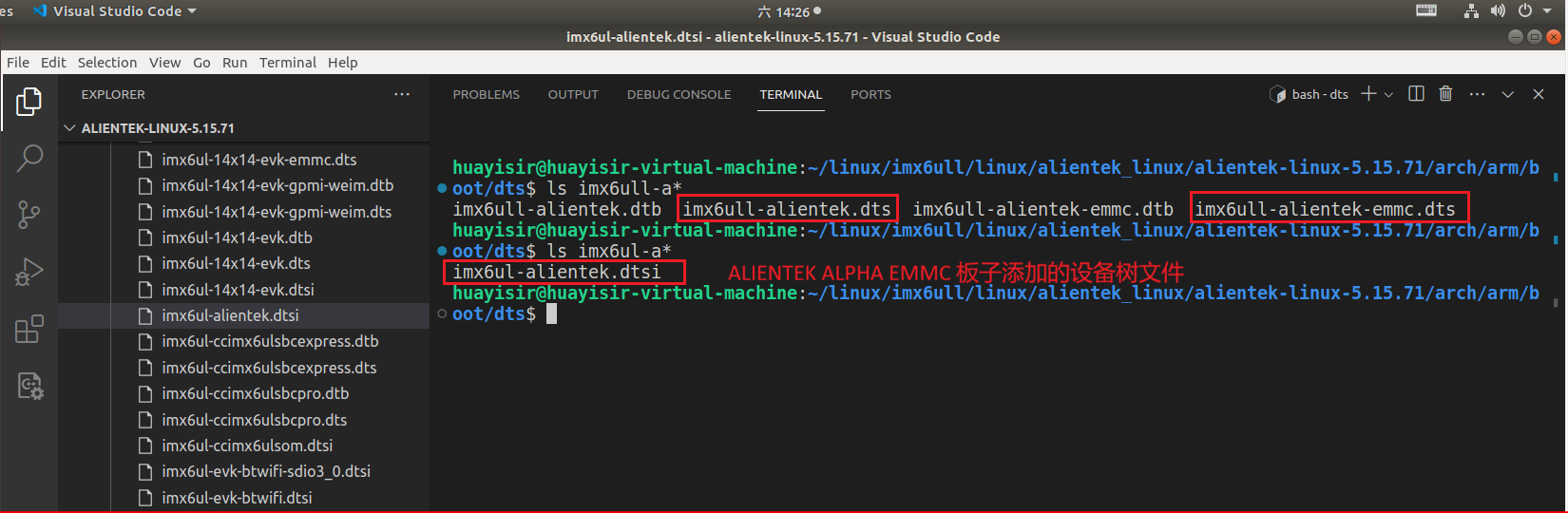

(1)修改LCD设备描述节点信息:

pinctrl-names = "default";

指定默认的引脚控制方案,表示使用默认引脚配置。

pinctrl-0 = <&pinctrl_lcdif_dat &pinctrl_lcdif_ctrl>;

引用了两个引脚控制节点,分别负责 LCD 的数据线和控制线(如 VSYNC、HSYNC)配置。

display = <&display0>;

将显示设备绑定到下面定义的 display0 子节点。

status = "okay";

表示启用该设备节点。

接下来是 display0: display@0 节点,定义了一个 LCD 显示设备的参数,有关LCD显示设备的参数详情请参见笔者另一篇文章:移植NXP官方uboot 4.1.15_2.1.0到ALIENTEK-ALPHA开发板(二) ---LCD驱动修改

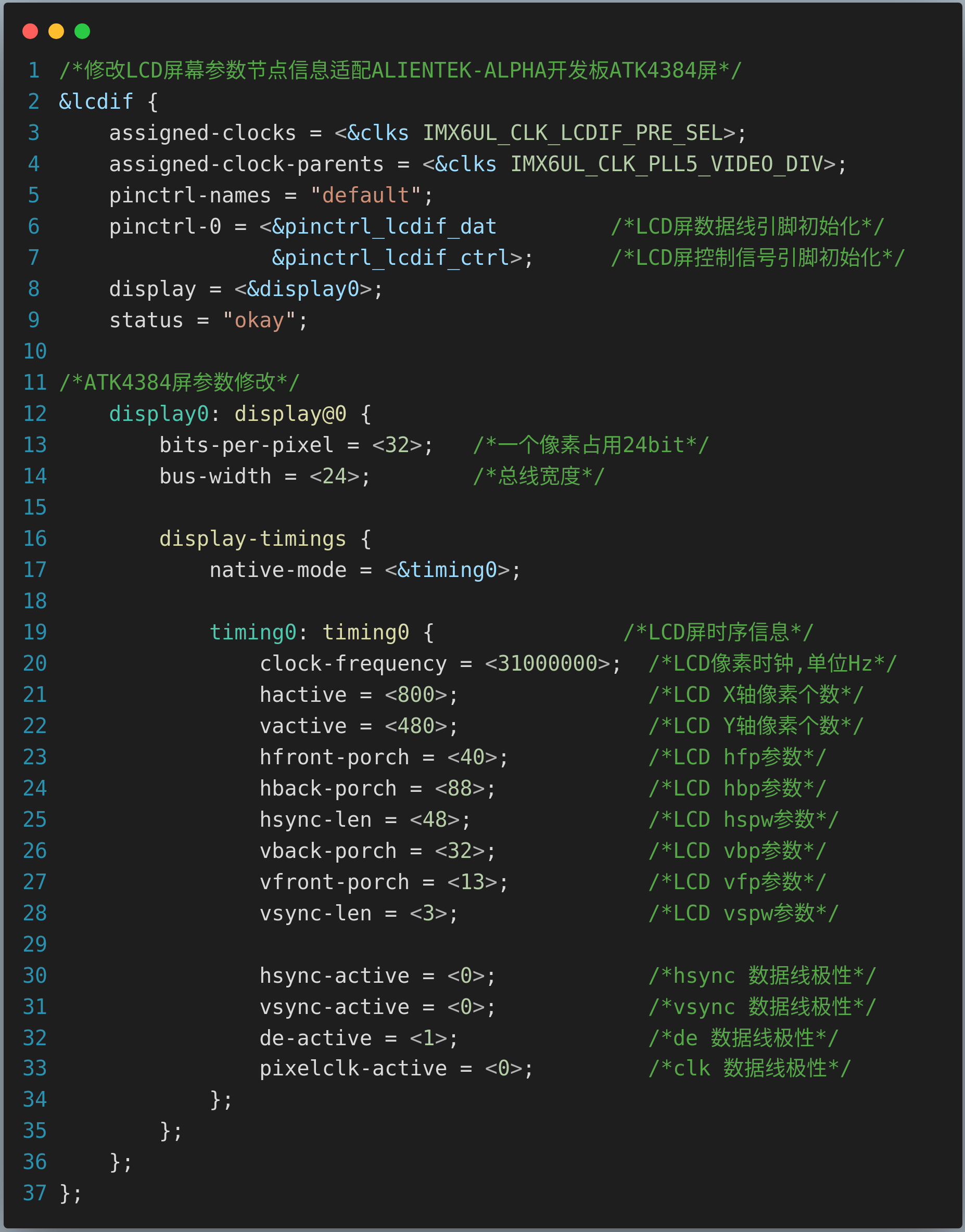

(2)修改LCD显示屏驱动引脚,如下图所示:

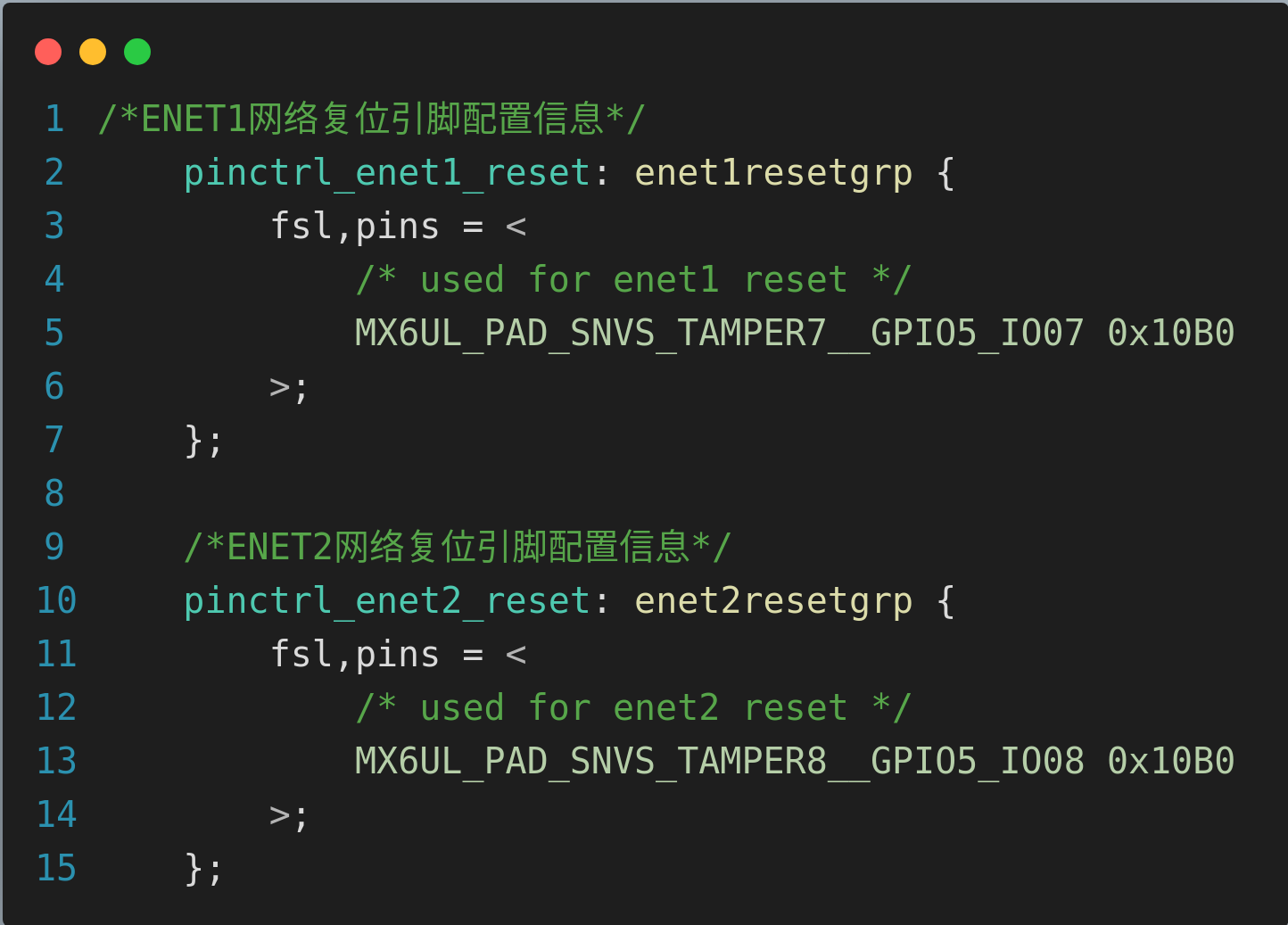

(3)修改ENET网络PHY芯片外设复位引脚的设置,如下图所示:

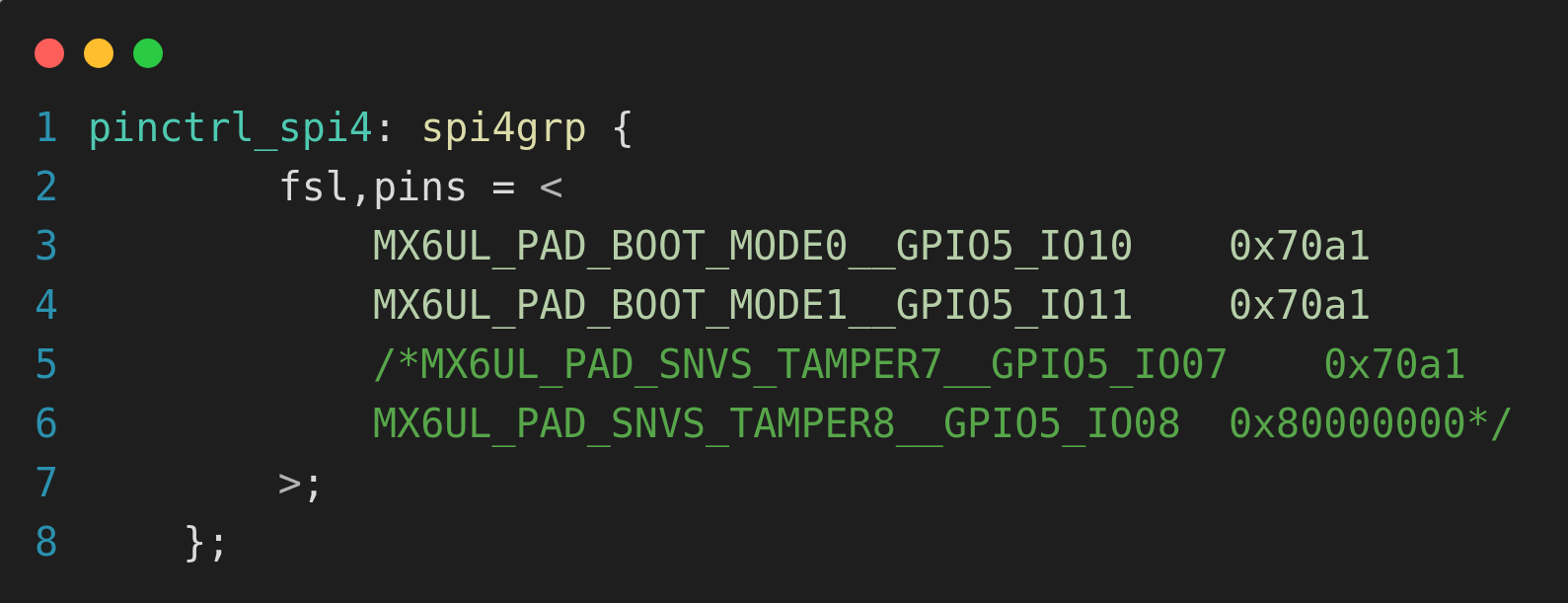

由于ALIENTEK ALPHA EMMC ENET网络PHY芯片的复位引脚为GPIO05_IO07和GPIO05_IO08,I.MX6ULL EVK开发板SPI引脚占用了这两个引脚,因此在SPI4接口描述中屏蔽这两个引脚。

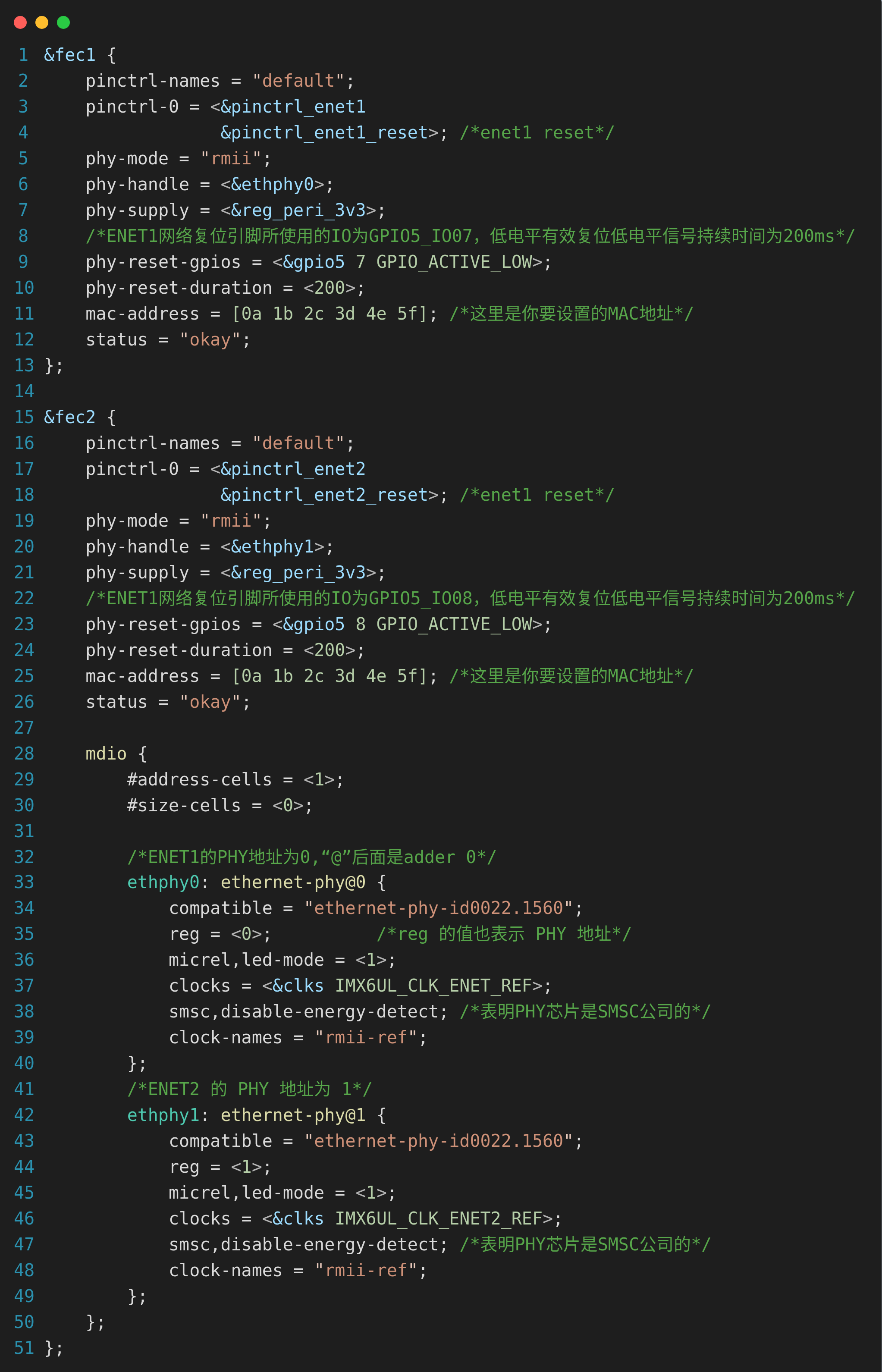

(3)修改ENET网络描述,如下图所示:

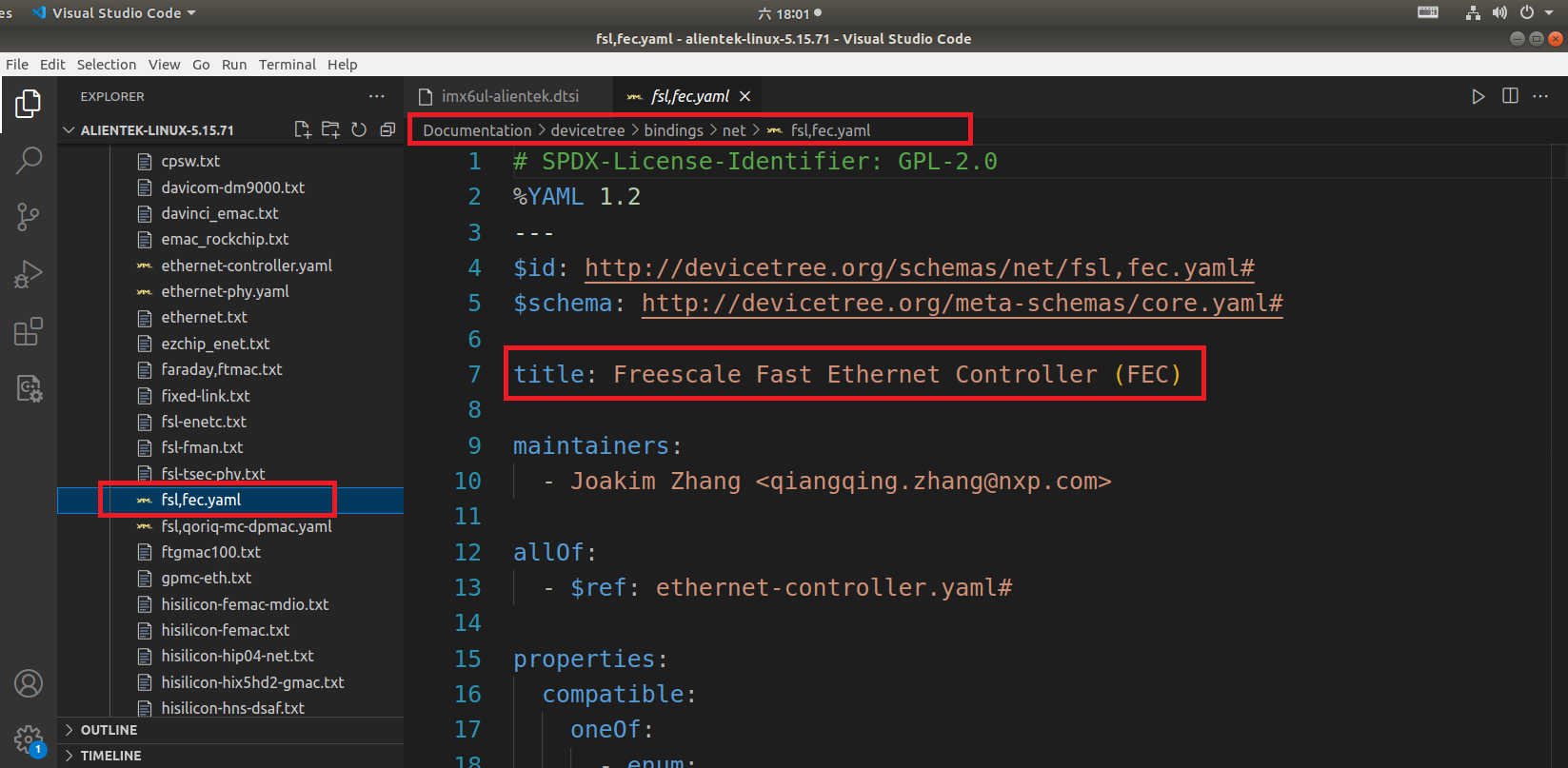

有关ENET网络的描述请参见Linux源码目录下Documentation/devicetree/bindings/net里面fsl,fec.yaml文件,如下图所示:

6.失能spi接口描述,如下图所示:

7.修改后的imx6ul_alientek.dtsi文件,如下:

// SPDX-License-Identifier: GPL-2.0

//

// Copyright (C) 2015 Freescale Semiconductor, Inc.

/ {

chosen {

stdout-path = &uart1;

};

memory@80000000 {

device_type = "memory";

reg = <0x80000000 0x20000000>;

};

reserved-memory {

#address-cells = <1>;

#size-cells = <1>;

ranges;

linux,cma {

compatible = "shared-dma-pool";

reusable;

size = <0xa000000>;

linux,cma-default;

};

};

backlight_display: backlight-display {

compatible = "pwm-backlight";

pwms = <&pwm1 0 5000000>;

brightness-levels = <0 4 8 16 32 64 128 255>;

default-brightness-level = <6>;

status = "okay";

};

pxp_v4l2 {

compatible = "fsl,imx6ul-pxp-v4l2", "fsl,imx6sx-pxp-v4l2", "fsl,imx6sl-pxp-v4l2";

status = "okay";

};

reg_sd1_vmmc: regulator-sd1-vmmc {

compatible = "regulator-fixed";

regulator-name = "VSD_3V3";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

gpio = <&gpio1 9 GPIO_ACTIVE_HIGH>;

off-on-delay-us = <20000>;

enable-active-high;

};

reg_peri_3v3: regulator-peri-3v3 {

compatible = "regulator-fixed";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_peri_3v3>;

regulator-name = "VPERI_3V3";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

gpio = <&gpio5 2 GPIO_ACTIVE_LOW>;

/*

* If you want to want to make this dynamic please

* check schematics and test all affected peripherals:

*

* - sensors

* - ethernet phy

* - can

* - bluetooth

* - wm8960 audio codec

* - ov5640 camera

*/

regulator-always-on;

};

reg_can_3v3: regulator-can-3v3 {

compatible = "regulator-fixed";

regulator-name = "can-3v3";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

gpios = <&gpio_spi 3 GPIO_ACTIVE_LOW>;

};

sound-wm8960 {

compatible = "fsl,imx-audio-wm8960";

model = "wm8960-audio";

audio-cpu = <&sai2>;

audio-codec = <&codec>;

audio-asrc = <&asrc>;

hp-det-gpio = <&gpio5 4 0>;

audio-routing =

"Headphone Jack", "HP_L",

"Headphone Jack", "HP_R",

"Ext Spk", "SPK_LP",

"Ext Spk", "SPK_LN",

"Ext Spk", "SPK_RP",

"Ext Spk", "SPK_RN",

"LINPUT2", "Mic Jack",

"LINPUT3", "Mic Jack",

"RINPUT1", "AMIC",

"RINPUT2", "AMIC",

"Mic Jack", "MICB",

"AMIC", "MICB";

};

spi4 {

compatible = "spi-gpio";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_spi4>;

status = "disable";

gpio-sck = <&gpio5 11 0>;

gpio-mosi = <&gpio5 10 0>;

cs-gpios = <&gpio5 7 GPIO_ACTIVE_LOW>;

num-chipselects = <1>;

#address-cells = <1>;

#size-cells = <0>;

gpio_spi: gpio@0 {

compatible = "fairchild,74hc595";

gpio-controller;

#gpio-cells = <2>;

reg = <0>;

registers-number = <1>;

registers-default = /bits/ 8 <0x57>;

spi-max-frequency = <100000>;

enable-gpios = <&gpio5 8 GPIO_ACTIVE_LOW>;

};

};

};

&clks {

assigned-clocks = <&clks IMX6UL_CLK_PLL4_AUDIO_DIV>;

assigned-clock-rates = <786432000>;

};

&csi {

status = "disabled";

port {

csi1_ep: endpoint {

remote-endpoint = <&ov5640_ep>;

};

};

};

&i2c2 {

clock-frequency = <100000>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_i2c2>;

status = "okay";

codec: wm8960@1a {

#sound-dai-cells = <0>;

compatible = "wlf,wm8960";

reg = <0x1a>;

wlf,shared-lrclk;

wlf,hp-cfg = <3 2 3>;

wlf,gpio-cfg = <1 3>;

clocks = <&clks IMX6UL_CLK_SAI2>;

clock-names = "mclk";

};

ov5640: ov5640@3c {

compatible = "ovti,ov5640";

reg = <0x3c>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_csi1 &pinctrl_camera_clock>;

clocks = <&clks IMX6UL_CLK_CSI>;

clock-names = "csi_mclk";

pwn-gpios = <&gpio_spi 6 1>;

rst-gpios = <&gpio_spi 5 0>;

csi_id = <0>;

mclk = <24000000>;

mclk_source = <0>;

status = "disabled";

port {

ov5640_ep: endpoint {

remote-endpoint = <&csi1_ep>;

};

};

};

};

&fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet1

&pinctrl_enet1_reset>; /*enet1 reset*/

phy-mode = "rmii";

phy-handle = <ðphy0>;

phy-supply = <®_peri_3v3>;

/*ENET1网络复位引脚所使用的IO为GPIO5_IO07,低电平有效复位低电平信号持续时间为200ms*/

phy-reset-gpios = <&gpio5 7 GPIO_ACTIVE_LOW>;

phy-reset-duration = <200>;

mac-address = [0a 1b 2c 3d 4e 5f]; /*这里是你要设置的MAC地址*/

status = "okay";

};

&fec2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet2

&pinctrl_enet2_reset>; /*enet1 reset*/

phy-mode = "rmii";

phy-handle = <ðphy1>;

phy-supply = <®_peri_3v3>;

/*ENET1网络复位引脚所使用的IO为GPIO5_IO08,低电平有效复位低电平信号持续时间为200ms*/

phy-reset-gpios = <&gpio5 8 GPIO_ACTIVE_LOW>;

phy-reset-duration = <200>;

mac-address = [0a 1b 2c 3d 4e 5f]; /*这里是你要设置的MAC地址*/

status = "okay";

mdio {

#address-cells = <1>;

#size-cells = <0>;

/*ENET1的PHY地址为0,"@"后面是adder 0*/

ethphy0: ethernet-phy@0 {

compatible = "ethernet-phy-id0022.1560";

reg = <0>; /*reg 的值也表示 PHY 地址*/

micrel,led-mode = <1>;

clocks = <&clks IMX6UL_CLK_ENET_REF>;

smsc,disable-energy-detect; /*表明PHY芯片是SMSC公司的*/

clock-names = "rmii-ref";

};

/*ENET2 的 PHY 地址为 1*/

ethphy1: ethernet-phy@1 {

compatible = "ethernet-phy-id0022.1560";

reg = <1>;

micrel,led-mode = <1>;

clocks = <&clks IMX6UL_CLK_ENET2_REF>;

smsc,disable-energy-detect; /*表明PHY芯片是SMSC公司的*/

clock-names = "rmii-ref";

};

};

};

&can1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_flexcan1>;

xceiver-supply = <®_can_3v3>;

status = "okay";

};

&can2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_flexcan2>;

xceiver-supply = <®_can_3v3>;

status = "okay";

};

&gpio_spi {

eth0-phy-hog {

gpio-hog;

gpios = <1 GPIO_ACTIVE_HIGH>;

output-high;

line-name = "eth0-phy";

};

eth1-phy-hog {

gpio-hog;

gpios = <2 GPIO_ACTIVE_HIGH>;

output-high;

line-name = "eth1-phy";

};

};

&i2c1 {

clock-frequency = <100000>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_i2c1>;

status = "okay";

magnetometer@e {

compatible = "fsl,mag3110";

reg = <0x0e>;

vdd-supply = <®_peri_3v3>;

vddio-supply = <®_peri_3v3>;

position = <2>;

};

fxls8471@1e {

compatible = "fsl,fxls8471";

reg = <0x1e>;

position = <0>;

interrupt-parent = <&gpio5>;

interrupts = <0 8>;

};

};

/*修改LCD屏幕参数节点信息适配ALIENTEK-ALPHA开发板ATK4384屏*/

&lcdif {

assigned-clocks = <&clks IMX6UL_CLK_LCDIF_PRE_SEL>;

assigned-clock-parents = <&clks IMX6UL_CLK_PLL5_VIDEO_DIV>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_lcdif_dat /*LCD屏数据线引脚初始化*/

&pinctrl_lcdif_ctrl>; /*LCD屏控制信号引脚初始化*/

display = <&display0>;

status = "okay";

/*ATK4384屏参数修改*/

display0: display@0 {

bits-per-pixel = <32>; /*一个像素占用24bit*/

bus-width = <24>; /*总线宽度*/

display-timings {

native-mode = <&timing0>;

timing0: timing0 { /*LCD屏时序信息*/

clock-frequency = <31000000>; /*LCD像素时钟,单位Hz*/

hactive = <800>; /*LCD X轴像素个数*/

vactive = <480>; /*LCD Y轴像素个数*/

hfront-porch = <40>; /*LCD hfp参数*/

hback-porch = <88>; /*LCD hbp参数*/

hsync-len = <48>; /*LCD hspw参数*/

vback-porch = <32>; /*LCD vbp参数*/

vfront-porch = <13>; /*LCD vfp参数*/

vsync-len = <3>; /*LCD vspw参数*/

hsync-active = <0>; /*hsync 数据线极性*/

vsync-active = <0>; /*vsync 数据线极性*/

de-active = <1>; /*de 数据线极性*/

pixelclk-active = <0>; /*clk 数据线极性*/

};

};

};

};

&pwm1 {

#pwm-cells = <2>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_pwm1>;

status = "okay";

};

&pxp {

status = "okay";

};

&qspi {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_qspi>;

status = "okay";

flash0: flash@0 {

#address-cells = <1>;

#size-cells = <1>;

compatible = "micron,n25q256a", "jedec,spi-nor";

spi-max-frequency = <29000000>;

spi-rx-bus-width = <4>;

spi-tx-bus-width = <1>;

reg = <0>;

};

};

&sai2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_sai2>;

assigned-clocks = <&clks IMX6UL_CLK_SAI2_SEL>,

<&clks IMX6UL_CLK_SAI2>;

assigned-clock-parents = <&clks IMX6UL_CLK_PLL4_AUDIO_DIV>;

assigned-clock-rates = <0>, <12288000>;

fsl,sai-mclk-direction-output;

status = "okay";

};

&snvs_poweroff {

status = "okay";

};

&snvs_pwrkey {

status = "okay";

};

&sim2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_sim2>;

assigned-clocks = <&clks IMX6UL_CLK_SIM_SEL>;

assigned-clock-parents = <&clks IMX6UL_CLK_SIM_PODF>;

assigned-clock-rates = <240000000>;

/* GPIO_ACTIVE_HIGH/LOW:sim card voltage control

* NCN8025:Vcc = ACTIVE_HIGH?5V:3V

* TDA8035:Vcc = ACTIVE_HIGH?5V:1.8V

*/

pinctrl-assert-gpios = <&gpio4 23 GPIO_ACTIVE_HIGH>;

port = <1>;

sven_low_active;

status = "okay";

};

&tsc {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_tsc>;

xnur-gpio = <&gpio1 3 GPIO_ACTIVE_LOW>;

measure-delay-time = <0xffff>;

pre-charge-time = <0xfff>;

status = "okay";

};

&uart1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart1>;

status = "okay";

};

&uart2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart2>;

uart-has-rtscts;

/* for DTE mode, add below change */

/* fsl,dte-mode; */

/* pinctrl-0 = <&pinctrl_uart2dte>; */

status = "okay";

};

&usbotg1 {

dr_mode = "otg";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_usb_otg1>;

status = "okay";

};

&usbotg2 {

dr_mode = "host";

disable-over-current;

status = "okay";

};

&usbphy1 {

fsl,tx-d-cal = <106>;

};

&usbphy2 {

fsl,tx-d-cal = <106>;

};

&usdhc1 {

pinctrl-names = "default", "state_100mhz", "state_200mhz";

pinctrl-0 = <&pinctrl_usdhc1>;

pinctrl-1 = <&pinctrl_usdhc1_100mhz>;

pinctrl-2 = <&pinctrl_usdhc1_200mhz>;

cd-gpios = <&gpio1 19 GPIO_ACTIVE_LOW>;

keep-power-in-suspend;

wakeup-source;

vmmc-supply = <®_sd1_vmmc>;

status = "okay";

};

&usdhc2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_usdhc2>;

non-removable;

keep-power-in-suspend;

wakeup-source;

status = "okay";

};

&wdog1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_wdog>;

fsl,ext-reset-output;

};

&iomuxc {

pinctrl-names = "default";

pinctrl_camera_clock: cameraclockgrp {

fsl,pins = <

MX6UL_PAD_CSI_MCLK__CSI_MCLK 0x1b088

>;

};

pinctrl_csi1: csi1grp {

fsl,pins = <

MX6UL_PAD_CSI_PIXCLK__CSI_PIXCLK 0x1b088

MX6UL_PAD_CSI_VSYNC__CSI_VSYNC 0x1b088

MX6UL_PAD_CSI_HSYNC__CSI_HSYNC 0x1b088

MX6UL_PAD_CSI_DATA00__CSI_DATA02 0x1b088

MX6UL_PAD_CSI_DATA01__CSI_DATA03 0x1b088

MX6UL_PAD_CSI_DATA02__CSI_DATA04 0x1b088

MX6UL_PAD_CSI_DATA03__CSI_DATA05 0x1b088

MX6UL_PAD_CSI_DATA04__CSI_DATA06 0x1b088

MX6UL_PAD_CSI_DATA05__CSI_DATA07 0x1b088

MX6UL_PAD_CSI_DATA06__CSI_DATA08 0x1b088

MX6UL_PAD_CSI_DATA07__CSI_DATA09 0x1b088

>;

};

/*ENET1和ENET2的网络时钟引脚配置信息*/

pinctrl_enet1: enet1grp {

fsl,pins = <

MX6UL_PAD_ENET1_RX_EN__ENET1_RX_EN 0x1b0b0

MX6UL_PAD_ENET1_RX_ER__ENET1_RX_ER 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA0__ENET1_RDATA00 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA1__ENET1_RDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_EN__ENET1_TX_EN 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA0__ENET1_TDATA00 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA1__ENET1_TDATA01 0x4001b009

>;

};

pinctrl_enet2: enet2grp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO07__ENET2_MDC 0x1b0b0

MX6UL_PAD_GPIO1_IO06__ENET2_MDIO 0x1b0b0

MX6UL_PAD_ENET2_RX_EN__ENET2_RX_EN 0x1b0b0

MX6UL_PAD_ENET2_RX_ER__ENET2_RX_ER 0x1b0b0

MX6UL_PAD_ENET2_RX_DATA0__ENET2_RDATA00 0x1b0b0

MX6UL_PAD_ENET2_RX_DATA1__ENET2_RDATA01 0x1b0b0

MX6UL_PAD_ENET2_TX_EN__ENET2_TX_EN 0x1b0b0

MX6UL_PAD_ENET2_TX_DATA0__ENET2_TDATA00 0x1b0b0

MX6UL_PAD_ENET2_TX_DATA1__ENET2_TDATA01 0x1b0b0

MX6UL_PAD_ENET2_TX_CLK__ENET2_REF_CLK2 0x4001b009

>;

};

/*ENET1网络复位引脚配置信息*/

pinctrl_enet1_reset: enet1resetgrp {

fsl,pins = <

/* used for enet1 reset */

MX6UL_PAD_SNVS_TAMPER7__GPIO5_IO07 0x10B0

>;

};

/*ENET2网络复位引脚配置信息*/

pinctrl_enet2_reset: enet2resetgrp {

fsl,pins = <

/* used for enet2 reset */

MX6UL_PAD_SNVS_TAMPER8__GPIO5_IO08 0x10B0

>;

};

pinctrl_flexcan1: flexcan1grp{

fsl,pins = <

MX6UL_PAD_UART3_RTS_B__FLEXCAN1_RX 0x1b020

MX6UL_PAD_UART3_CTS_B__FLEXCAN1_TX 0x1b020

>;

};

pinctrl_flexcan2: flexcan2grp{

fsl,pins = <

MX6UL_PAD_UART2_RTS_B__FLEXCAN2_RX 0x1b020

MX6UL_PAD_UART2_CTS_B__FLEXCAN2_TX 0x1b020

>;

};

pinctrl_i2c1: i2c1grp {

fsl,pins = <

MX6UL_PAD_UART4_TX_DATA__I2C1_SCL 0x4001b8b0

MX6UL_PAD_UART4_RX_DATA__I2C1_SDA 0x4001b8b0

>;

};

pinctrl_i2c2: i2c2grp {

fsl,pins = <

MX6UL_PAD_UART5_TX_DATA__I2C2_SCL 0x4001b8b0

MX6UL_PAD_UART5_RX_DATA__I2C2_SDA 0x4001b8b0

>;

};

/*ALIENTEK-ALPHA开发板上的LCD接口使用了三个SGM3157模拟开关,

为了防止模拟开关影响到网络需要降低LCD数据线的驱动能力,

也就是将LCD相关IO的驱动能力改为 R0/1,因此将0x79改为哦0x49*/

pinctrl_lcdif_dat: lcdifdatgrp {

fsl,pins = <

MX6UL_PAD_LCD_DATA00__LCDIF_DATA00 0x49

MX6UL_PAD_LCD_DATA01__LCDIF_DATA01 0x49

MX6UL_PAD_LCD_DATA02__LCDIF_DATA02 0x49

MX6UL_PAD_LCD_DATA03__LCDIF_DATA03 0x49

MX6UL_PAD_LCD_DATA04__LCDIF_DATA04 0x49

MX6UL_PAD_LCD_DATA05__LCDIF_DATA05 0x49

MX6UL_PAD_LCD_DATA06__LCDIF_DATA06 0x49

MX6UL_PAD_LCD_DATA07__LCDIF_DATA07 0x49

MX6UL_PAD_LCD_DATA08__LCDIF_DATA08 0x49

MX6UL_PAD_LCD_DATA09__LCDIF_DATA09 0x49

MX6UL_PAD_LCD_DATA10__LCDIF_DATA10 0x49

MX6UL_PAD_LCD_DATA11__LCDIF_DATA11 0x49

MX6UL_PAD_LCD_DATA12__LCDIF_DATA12 0x49

MX6UL_PAD_LCD_DATA13__LCDIF_DATA13 0x49

MX6UL_PAD_LCD_DATA14__LCDIF_DATA14 0x49

MX6UL_PAD_LCD_DATA15__LCDIF_DATA15 0x49

MX6UL_PAD_LCD_DATA16__LCDIF_DATA16 0x49

MX6UL_PAD_LCD_DATA17__LCDIF_DATA17 0x49

MX6UL_PAD_LCD_DATA18__LCDIF_DATA18 0x49

MX6UL_PAD_LCD_DATA19__LCDIF_DATA19 0x49

MX6UL_PAD_LCD_DATA20__LCDIF_DATA20 0x49

MX6UL_PAD_LCD_DATA21__LCDIF_DATA21 0x49

MX6UL_PAD_LCD_DATA22__LCDIF_DATA22 0x49

MX6UL_PAD_LCD_DATA23__LCDIF_DATA23 0x49

>;

};

/*LCD显示屏控制引脚配置项LCD_PCLK、LCD_DE、LCD_HSYNC、LCD_VSYNC*/

pinctrl_lcdif_ctrl: lcdifctrlgrp {

fsl,pins = <

MX6UL_PAD_LCD_CLK__LCDIF_CLK 0x49

MX6UL_PAD_LCD_ENABLE__LCDIF_ENABLE 0x49

MX6UL_PAD_LCD_HSYNC__LCDIF_HSYNC 0x49

MX6UL_PAD_LCD_VSYNC__LCDIF_VSYNC 0x49

/* used for lcd reset */

/*MX6UL_PAD_SNVS_TAMPER9__GPIO5_IO09 0x79*/

>;

};

pinctrl_qspi: qspigrp {

fsl,pins = <

MX6UL_PAD_NAND_WP_B__QSPI_A_SCLK 0x70a1

MX6UL_PAD_NAND_READY_B__QSPI_A_DATA00 0x70a1

MX6UL_PAD_NAND_CE0_B__QSPI_A_DATA01 0x70a1

MX6UL_PAD_NAND_CE1_B__QSPI_A_DATA02 0x70a1

MX6UL_PAD_NAND_CLE__QSPI_A_DATA03 0x70a1

MX6UL_PAD_NAND_DQS__QSPI_A_SS0_B 0x70a1

>;

};

pinctrl_sai2: sai2grp {

fsl,pins = <

MX6UL_PAD_JTAG_TDI__SAI2_TX_BCLK 0x17088

MX6UL_PAD_JTAG_TDO__SAI2_TX_SYNC 0x17088

MX6UL_PAD_JTAG_TRST_B__SAI2_TX_DATA 0x11088

MX6UL_PAD_JTAG_TCK__SAI2_RX_DATA 0x11088

MX6UL_PAD_JTAG_TMS__SAI2_MCLK 0x17088

MX6UL_PAD_SNVS_TAMPER4__GPIO5_IO04 0x17059

>;

};

pinctrl_peri_3v3: peri3v3grp {

fsl,pins = <

MX6UL_PAD_SNVS_TAMPER2__GPIO5_IO02 0x1b0b0

>;

};

pinctrl_pwm1: pwm1grp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO08__PWM1_OUT 0x110b0

>;

};

pinctrl_sim2: sim2grp {

fsl,pins = <

MX6UL_PAD_CSI_DATA03__SIM2_PORT1_PD 0xb808

MX6UL_PAD_CSI_DATA04__SIM2_PORT1_CLK 0x31

MX6UL_PAD_CSI_DATA05__SIM2_PORT1_RST_B 0xb808

MX6UL_PAD_CSI_DATA06__SIM2_PORT1_SVEN 0xb808

MX6UL_PAD_CSI_DATA07__SIM2_PORT1_TRXD 0xb809

MX6UL_PAD_CSI_DATA02__GPIO4_IO23 0x3008

>;

};

pinctrl_spi4: spi4grp {

fsl,pins = <

MX6UL_PAD_BOOT_MODE0__GPIO5_IO10 0x70a1

MX6UL_PAD_BOOT_MODE1__GPIO5_IO11 0x70a1

/*MX6UL_PAD_SNVS_TAMPER7__GPIO5_IO07 0x70a1

MX6UL_PAD_SNVS_TAMPER8__GPIO5_IO08 0x80000000*/

>;

};

pinctrl_tsc: tscgrp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO01__GPIO1_IO01 0xb0

MX6UL_PAD_GPIO1_IO02__GPIO1_IO02 0xb0

MX6UL_PAD_GPIO1_IO03__GPIO1_IO03 0xb0

MX6UL_PAD_GPIO1_IO04__GPIO1_IO04 0xb0

>;

};

pinctrl_uart1: uart1grp {

fsl,pins = <

MX6UL_PAD_UART1_TX_DATA__UART1_DCE_TX 0x1b0b1

MX6UL_PAD_UART1_RX_DATA__UART1_DCE_RX 0x1b0b1

>;

};

pinctrl_uart2: uart2grp {

fsl,pins = <

MX6UL_PAD_UART2_TX_DATA__UART2_DCE_TX 0x1b0b1

MX6UL_PAD_UART2_RX_DATA__UART2_DCE_RX 0x1b0b1

MX6UL_PAD_UART3_RX_DATA__UART2_DCE_RTS 0x1b0b1

MX6UL_PAD_UART3_TX_DATA__UART2_DCE_CTS 0x1b0b1

>;

};

pinctrl_uart2dte: uart2dtegrp {

fsl,pins = <

MX6UL_PAD_UART2_TX_DATA__UART2_DTE_RX 0x1b0b1

MX6UL_PAD_UART2_RX_DATA__UART2_DTE_TX 0x1b0b1

MX6UL_PAD_UART3_RX_DATA__UART2_DTE_CTS 0x1b0b1

MX6UL_PAD_UART3_TX_DATA__UART2_DTE_RTS 0x1b0b1

>;

};

pinctrl_usb_otg1: usbotg1grp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO00__ANATOP_OTG1_ID 0x17059

>;

};

pinctrl_usdhc1: usdhc1grp {

fsl,pins = <

MX6UL_PAD_SD1_CMD__USDHC1_CMD 0x17059

MX6UL_PAD_SD1_CLK__USDHC1_CLK 0x10071

MX6UL_PAD_SD1_DATA0__USDHC1_DATA0 0x17059

MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x17059

MX6UL_PAD_SD1_DATA2__USDHC1_DATA2 0x17059

MX6UL_PAD_SD1_DATA3__USDHC1_DATA3 0x17059

MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 0x17059 /* SD1 CD */

MX6UL_PAD_GPIO1_IO05__USDHC1_VSELECT 0x17059 /* SD1 VSELECT */

MX6UL_PAD_GPIO1_IO09__GPIO1_IO09 0x17059 /* SD1 RESET */

>;

};

pinctrl_usdhc1_100mhz: usdhc1grp100mhz {

fsl,pins = <

MX6UL_PAD_SD1_CMD__USDHC1_CMD 0x170b9

MX6UL_PAD_SD1_CLK__USDHC1_CLK 0x100b9

MX6UL_PAD_SD1_DATA0__USDHC1_DATA0 0x170b9

MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x170b9

MX6UL_PAD_SD1_DATA2__USDHC1_DATA2 0x170b9

MX6UL_PAD_SD1_DATA3__USDHC1_DATA3 0x170b9

>;

};

pinctrl_usdhc1_200mhz: usdhc1grp200mhz {

fsl,pins = <

MX6UL_PAD_SD1_CMD__USDHC1_CMD 0x170f9

MX6UL_PAD_SD1_CLK__USDHC1_CLK 0x100f9

MX6UL_PAD_SD1_DATA0__USDHC1_DATA0 0x170f9

MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x170f9

MX6UL_PAD_SD1_DATA2__USDHC1_DATA2 0x170f9

MX6UL_PAD_SD1_DATA3__USDHC1_DATA3 0x170f9

>;

};

pinctrl_usdhc2: usdhc2grp {

fsl,pins = <

MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x17059

MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x17059

MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x17059

MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x17059

MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x17059

MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x17059

>;

};

pinctrl_usdhc2_8bit: usdhc2grp_8bit {

fsl,pins = <

MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x10069

MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x17059

MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x17059

MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x17059

MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x17059

MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x17059

MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x17059

MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x17059

MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x17059

MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x17059

>;

};

pinctrl_usdhc2_8bit_100mhz: usdhc2grp_8bit_100mhz {

fsl,pins = <

MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x100b9

MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x170b9

MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x170b9

MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x170b9

MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x170b9

MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x170b9

MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x170b9

MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x170b9

MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x170b9

MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x170b9

>;

};

pinctrl_usdhc2_8bit_200mhz: usdhc2grp_8bit_200mhz {

fsl,pins = <

MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x100f9

MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x170f9

MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x170f9

MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x170f9

MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x170f9

MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x170f9

MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x170f9

MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x170f9

MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x170f9

MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x170f9

>;

};

pinctrl_wdog: wdoggrp {

fsl,pins = <

MX6UL_PAD_LCD_RESET__WDOG1_WDOG_ANY 0x30b0

>;

};

};8.修改arch/arm/boot/dts/Makefile文件,将我们创建的ALIENTEK-ALPHA开发板设备树文件添加进编译选项,如下图所示:

3.编译修改后的Linux源码

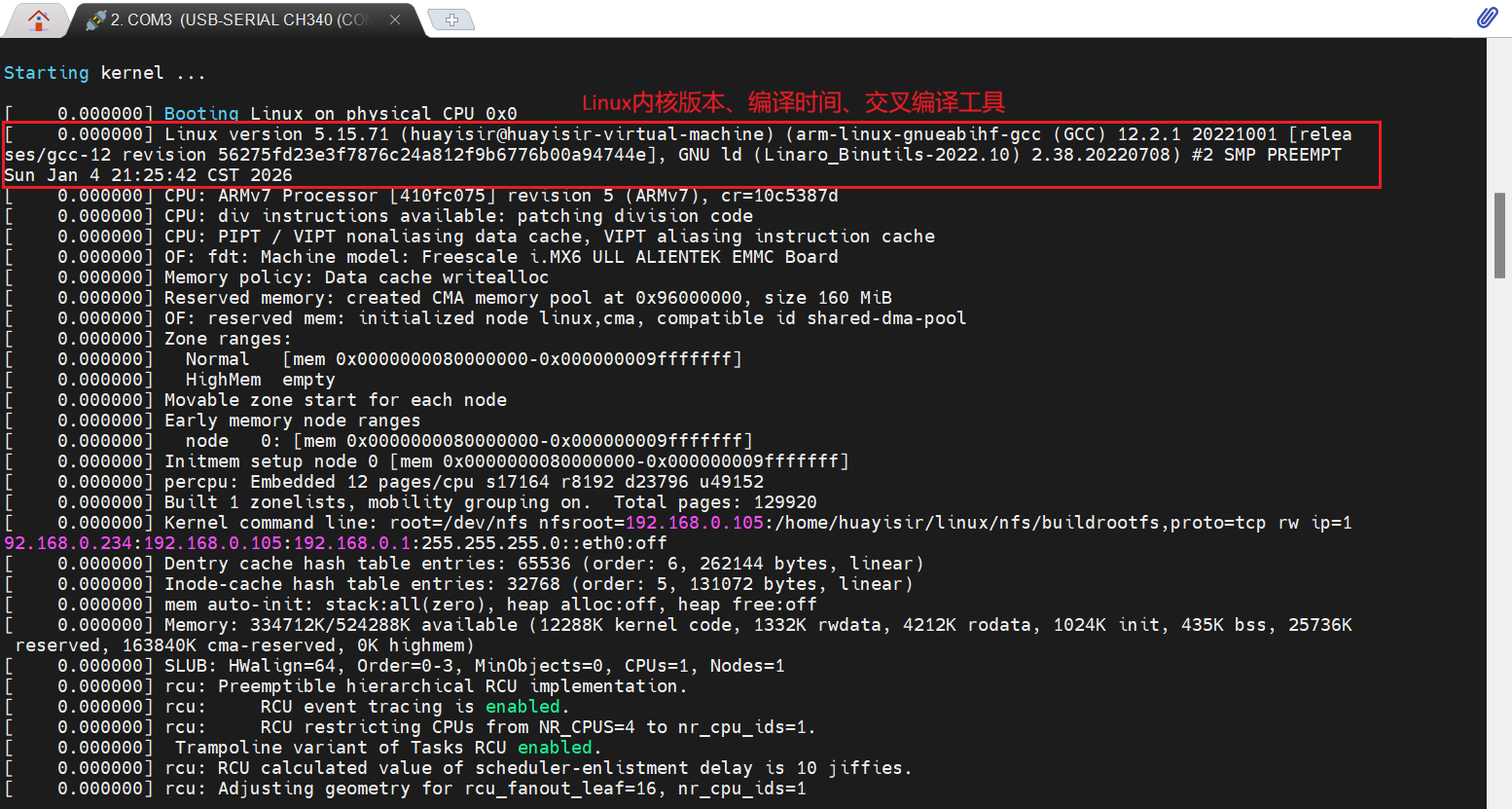

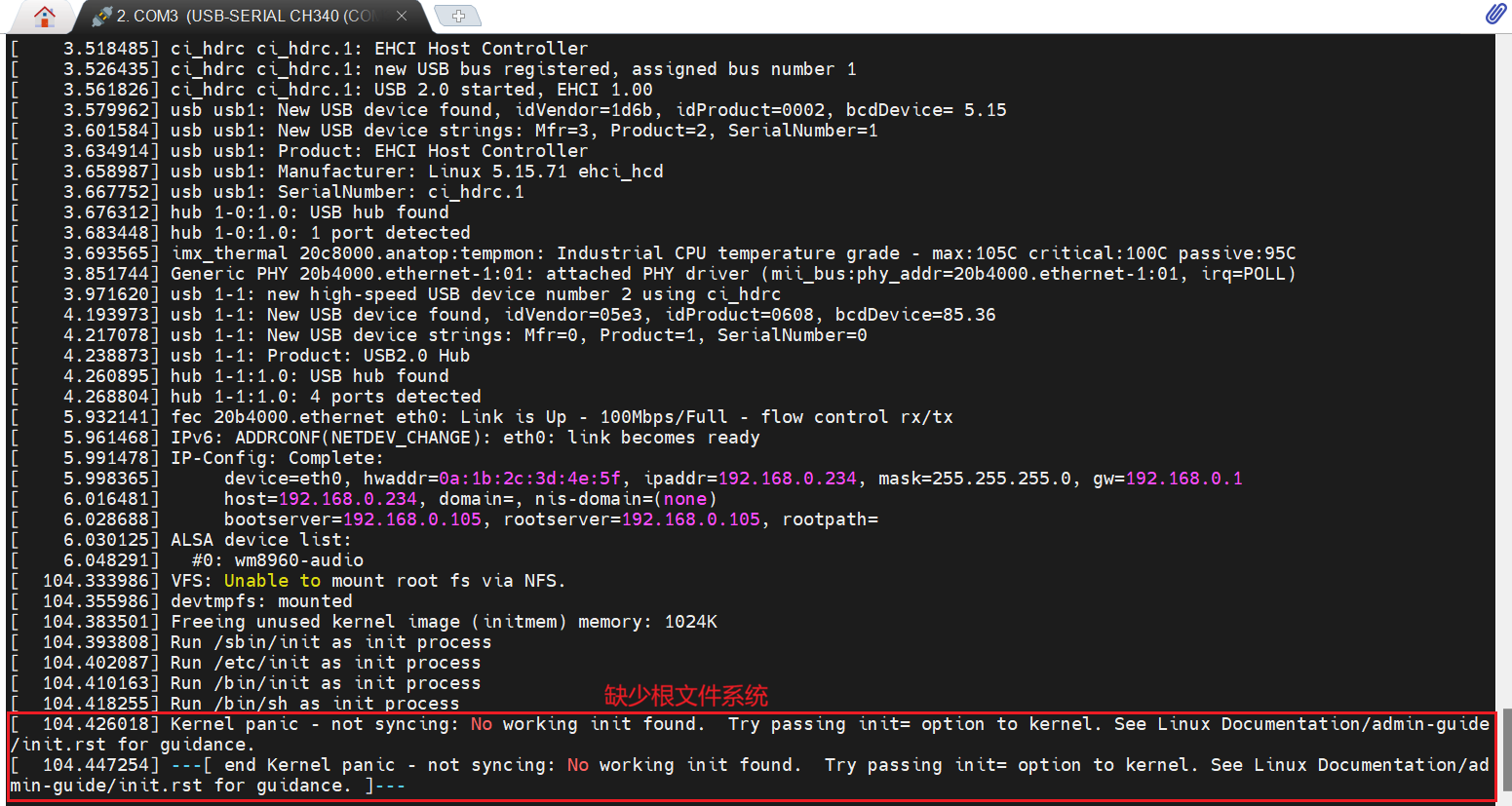

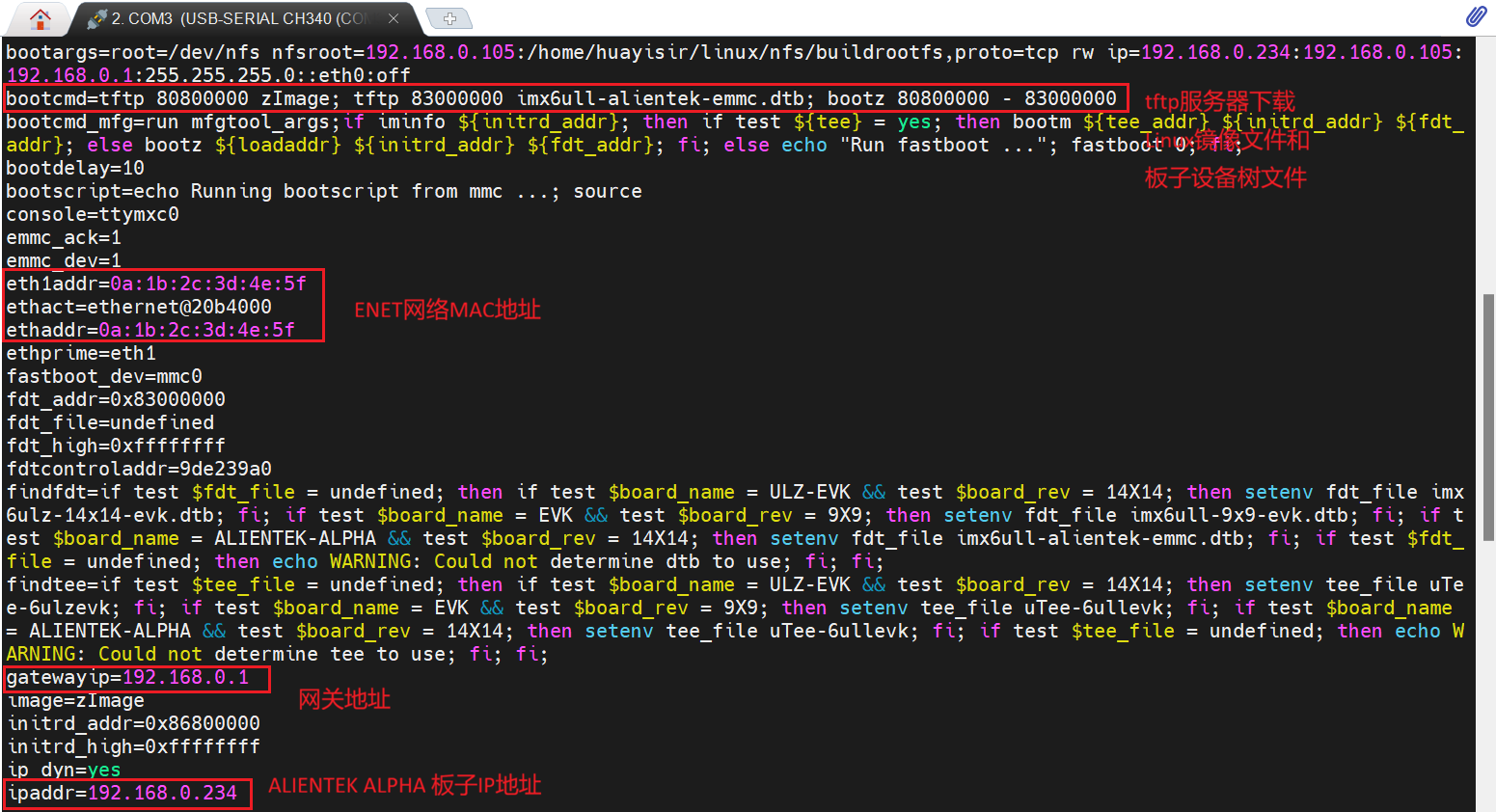

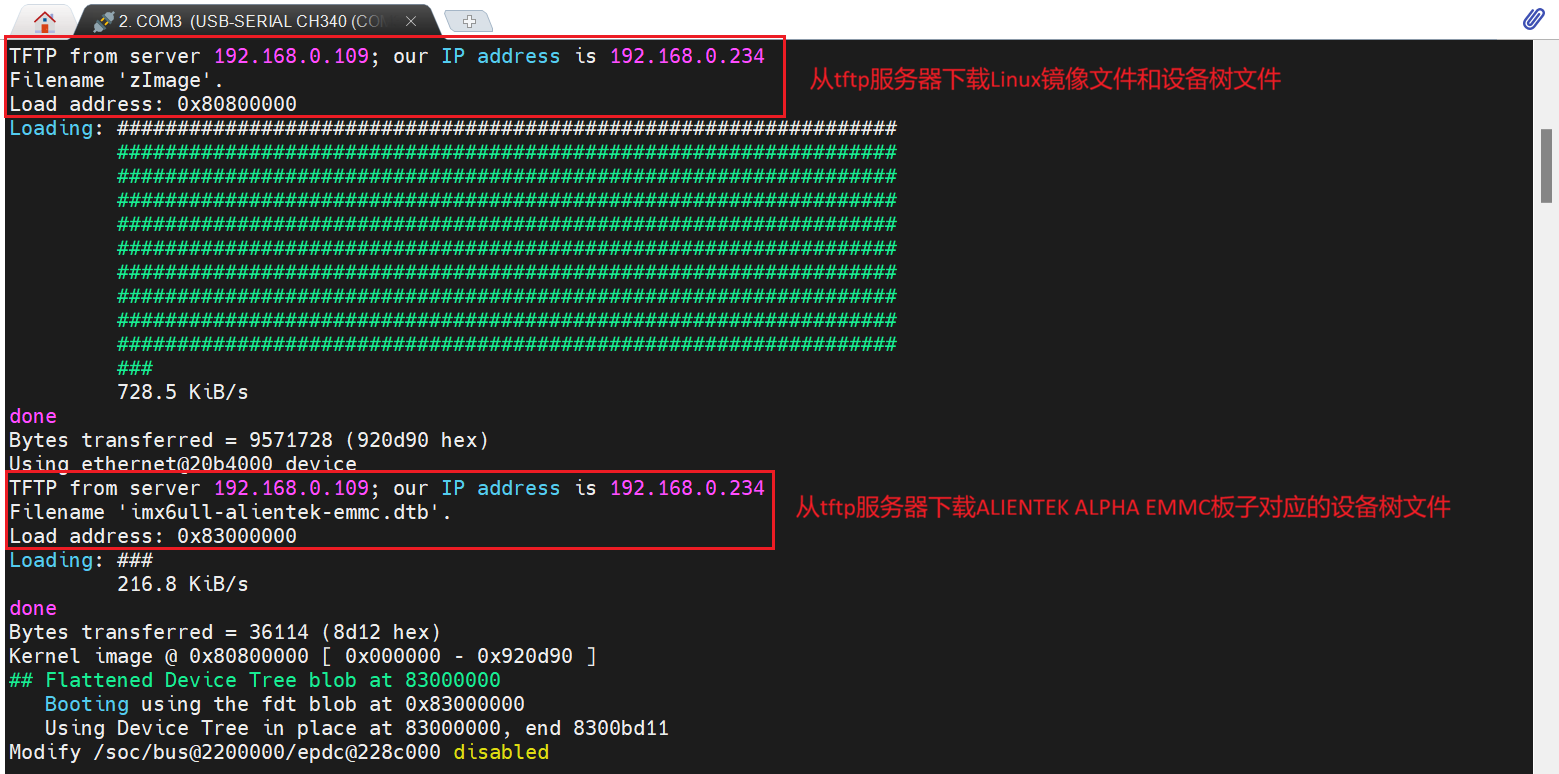

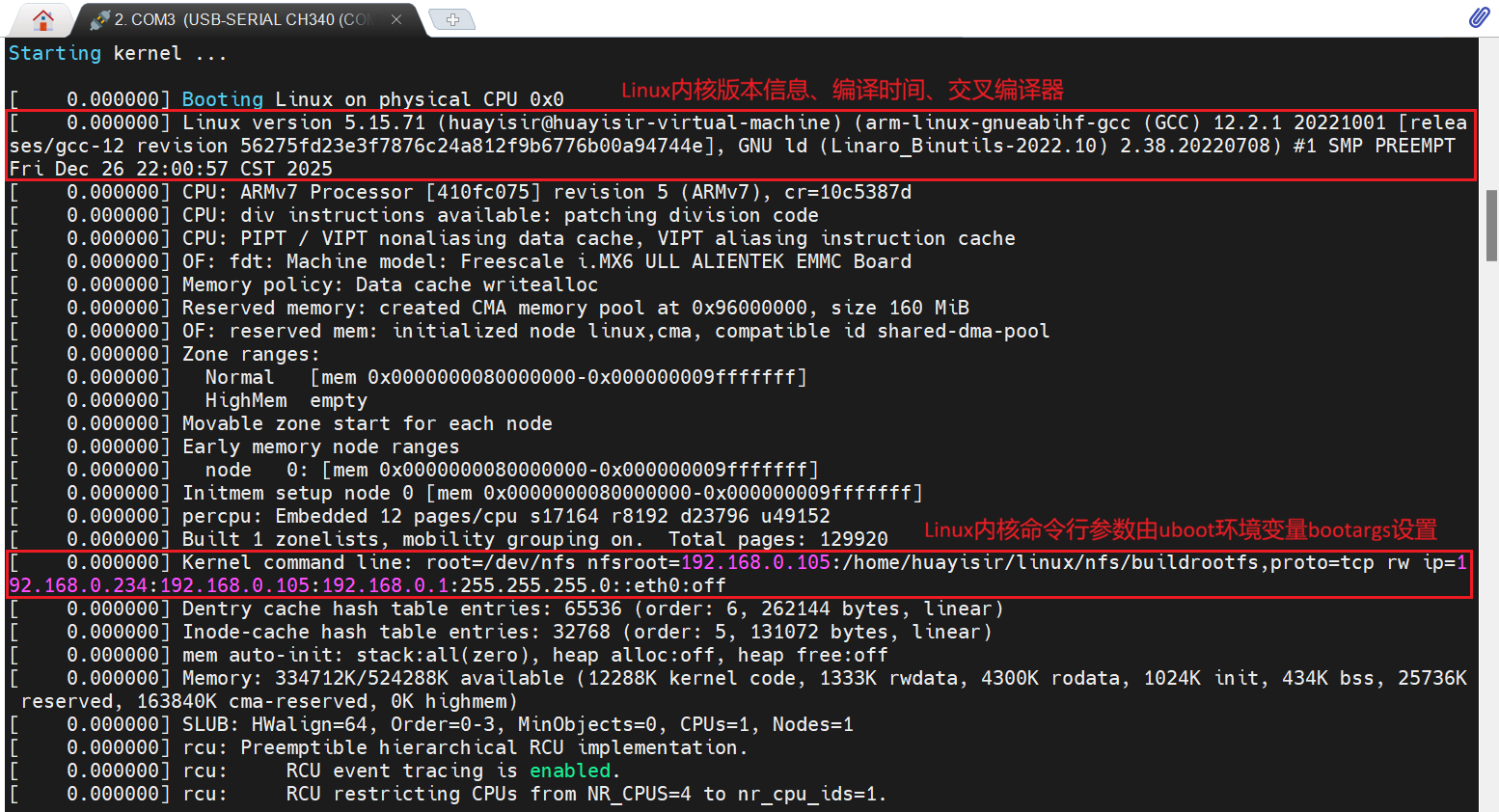

1.编译Linux源码,将编译生成的Linux镜像文件zImage (arch/arm/boot目录下 )和二进制设备树文件imx6ull-alientek-emmc.dtb (arch/arm/boot/dts目录下 )复制到tftp目录下,uboot设置bootcmd命令从tftp服务器下载Linux镜像文件和设备树文件,如下图所示:

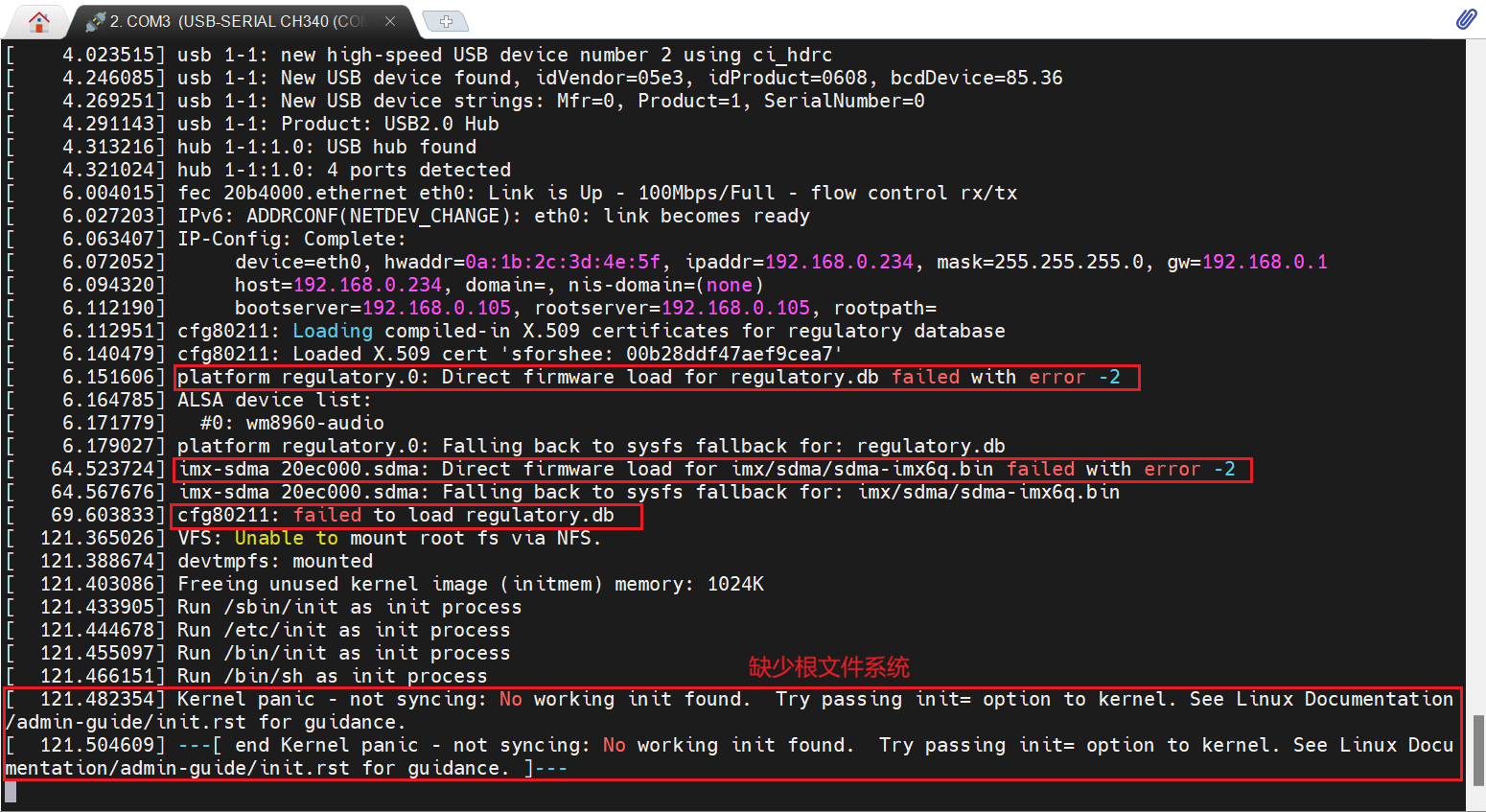

对于Linux启动出现上述两个错误的解决方案请查看本人另外一篇文章,Linux5.15.71编译问题处理,对上述的两个问题进行修复修复后重新下载Linux镜像文件,Linux启动过程如下图所示: