前 言

本文为创龙科技编写的PL端案例开发的指引文档,对PL端开发案例进行简要介绍。

开发环境

Windows开发环境:Windows10 64bit

开发工具:TD_5.9.1_DR1_2025.1_NL、FD_2025.1_SP1

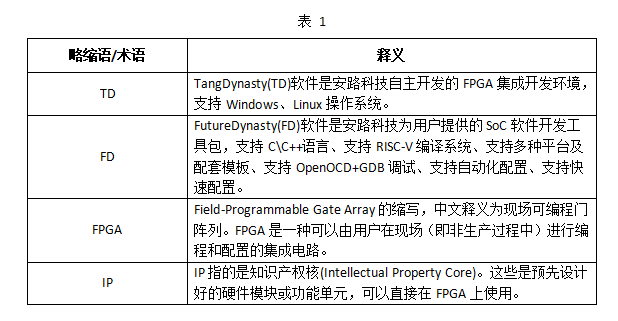

术语表

为便于阅读,下表对文档出现的关键术语进行解释;对于广泛认同释义的术语,在此不做注释。

注意事项

(1)请先按照《开发环境搭建》文档安装TD、FD等软件以及进行JTAG驱动安装,使用下载器(厂家:安路科技,型号:AL-LINK-FT-V1.0)连接评估板JTAG接口至PC端USB接口。

(2)在进行本文操作前,请先参考《TD-FD工程编译与加载》,熟悉工程编译、镜像加载等方法。

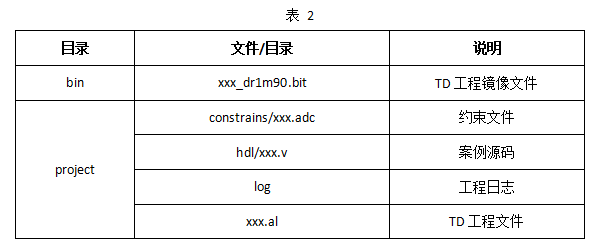

(3)案例位于产品资料"4-软件资料\Demo\FPGA-demos\FPGA-HDL-demos\"目录下。案例包含bin目录和project压缩包,其中bin目录下含有案例可执行镜像文件,project压缩包内包含案例工程文件。案例目录详细说明见下表:

1 led_flash案例

1.1 案例说明

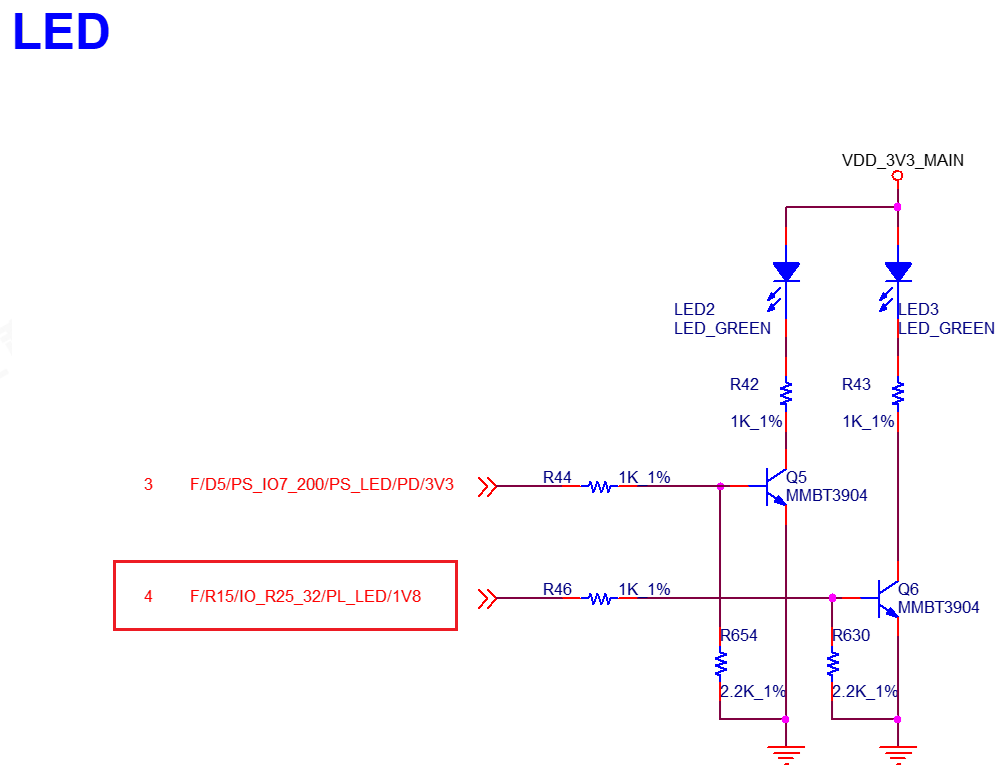

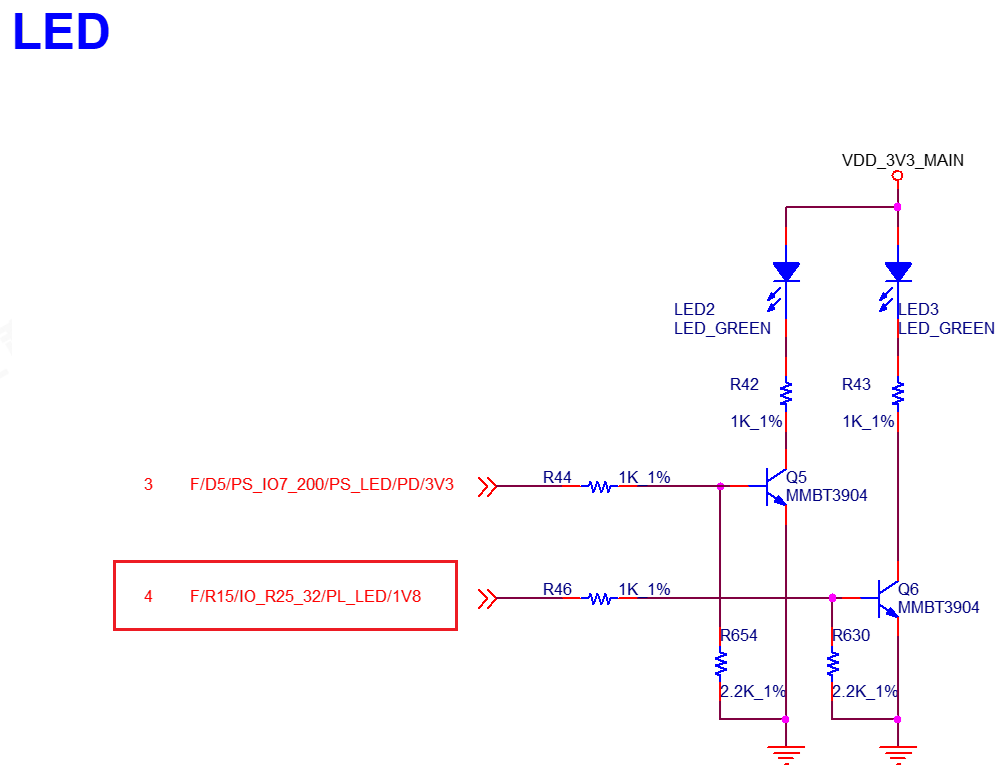

案例功能:控制评估底板LED3每隔0.5s将状态翻转一次。

管脚约束请查看案例工程"project\constraints\"目录下的.adc文件。

图 1

1.2 操作说明

请将工程镜像加载至PL端运行,即可看到评估底板的LED3进行闪烁。

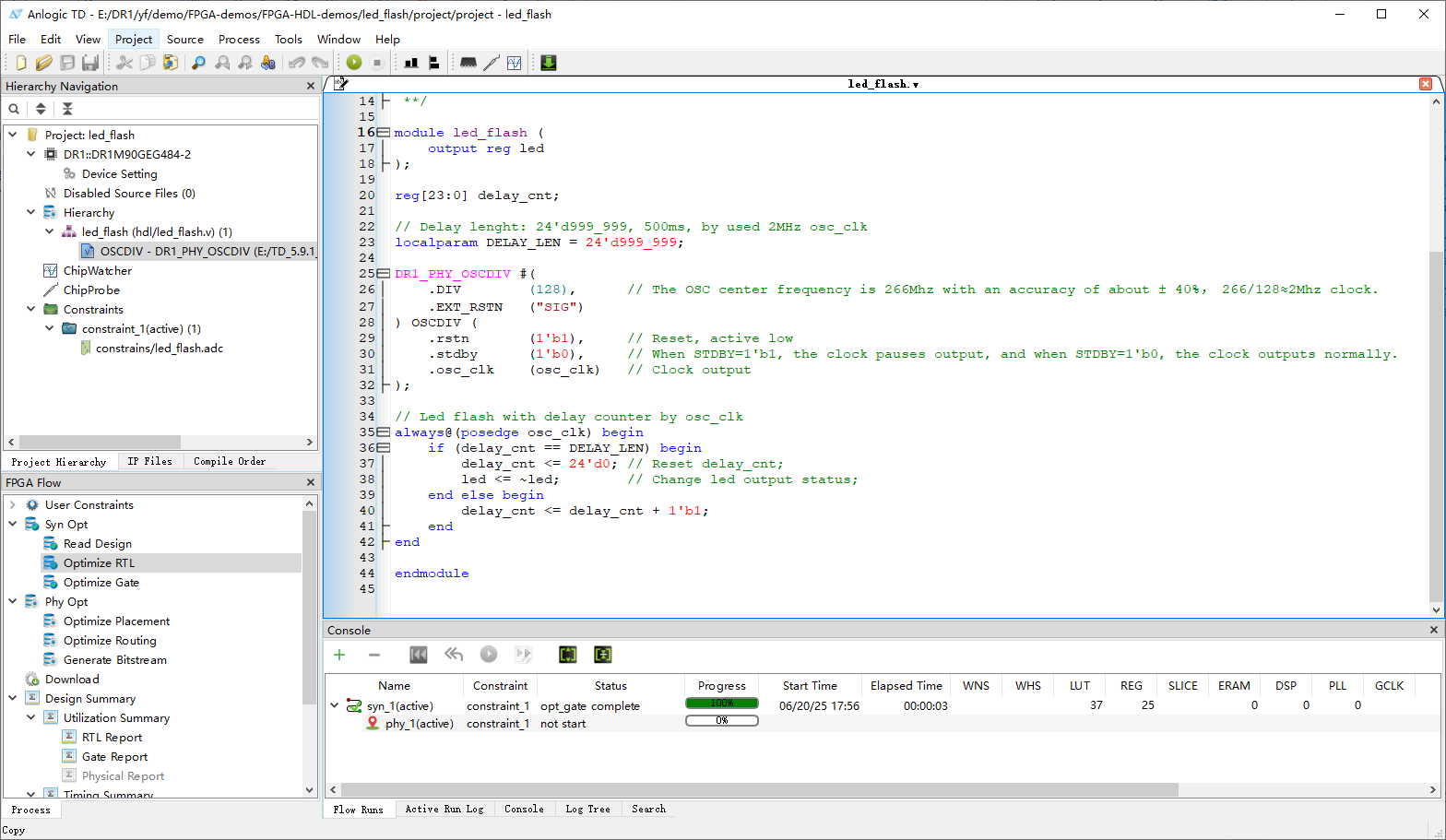

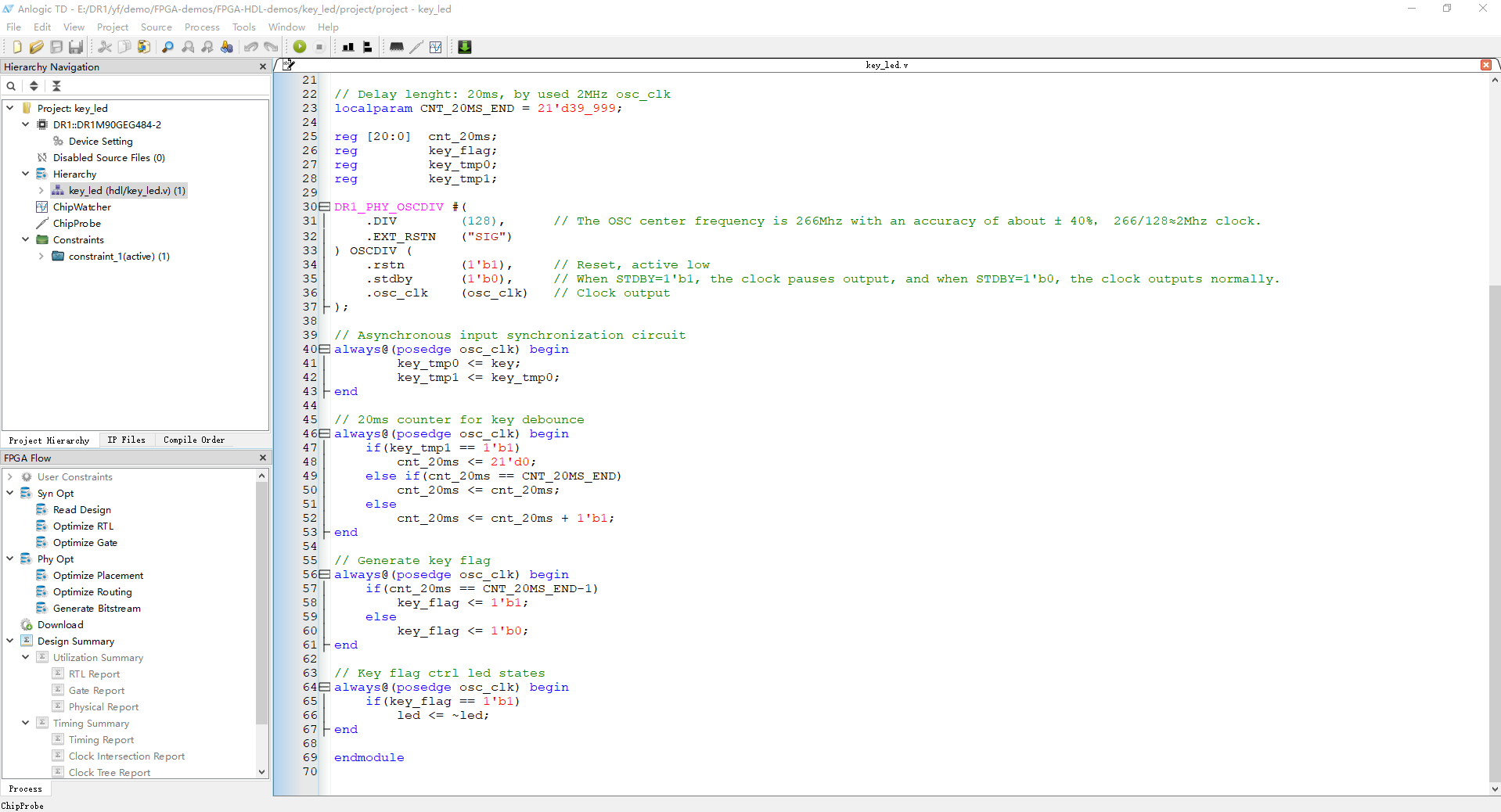

1.3 关键代码

(1)使用DR1_PHY_OSCDIV原语提供的osc_clk(2MHz)作为LED的参考时钟。

(2)利用osc_clk(2MHz)进行计数,使LED实现间隔0.5s进行状态转换。

图 2

2 key_led案例

2.1 案例说明

案例功能:通过按键KEY4(USER2)控制评估底板的LED3状态。

管脚约束请查看案例工程"project\constraints\"目录下的.adc文件。

图 3

图 4

2.2 操作说明

请将工程镜像加载至PL端运行,按下KEY4按键,可看到评估底板的LED3状态翻转。

2.3 关键代码

(1)使用DR1_PHY_OSCDIV原语提供的osc_clk(2MHz)作为系统时钟。

(2)对按键按下时进行消抖处理。

(3)通过按键按下产生对应标志控制LED状态。

图 5

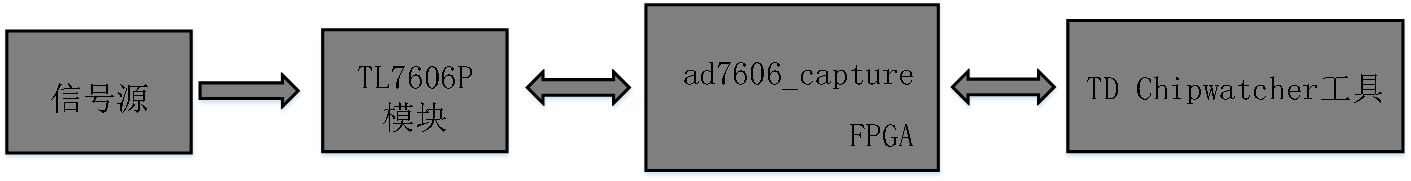

3 ad7606_capture案例

3.1 案例说明

案例功能:通过创龙科技TL7606P模块采集8通道数据(采样率为200KSPS),并使用TD软件的ChipWatcher工具,将采集的数据转换成电压值并保存为.csv文件。程序功能框图如下所示。

本案例使用创龙科技TL7606P-A1模块,硬件配置为并行模式,支持核芯互联CL1606(国产)和ADI AD7606采样芯片。

图 6

管脚约束请查看案例工程"project\constraints\"目录下的.adc文件。

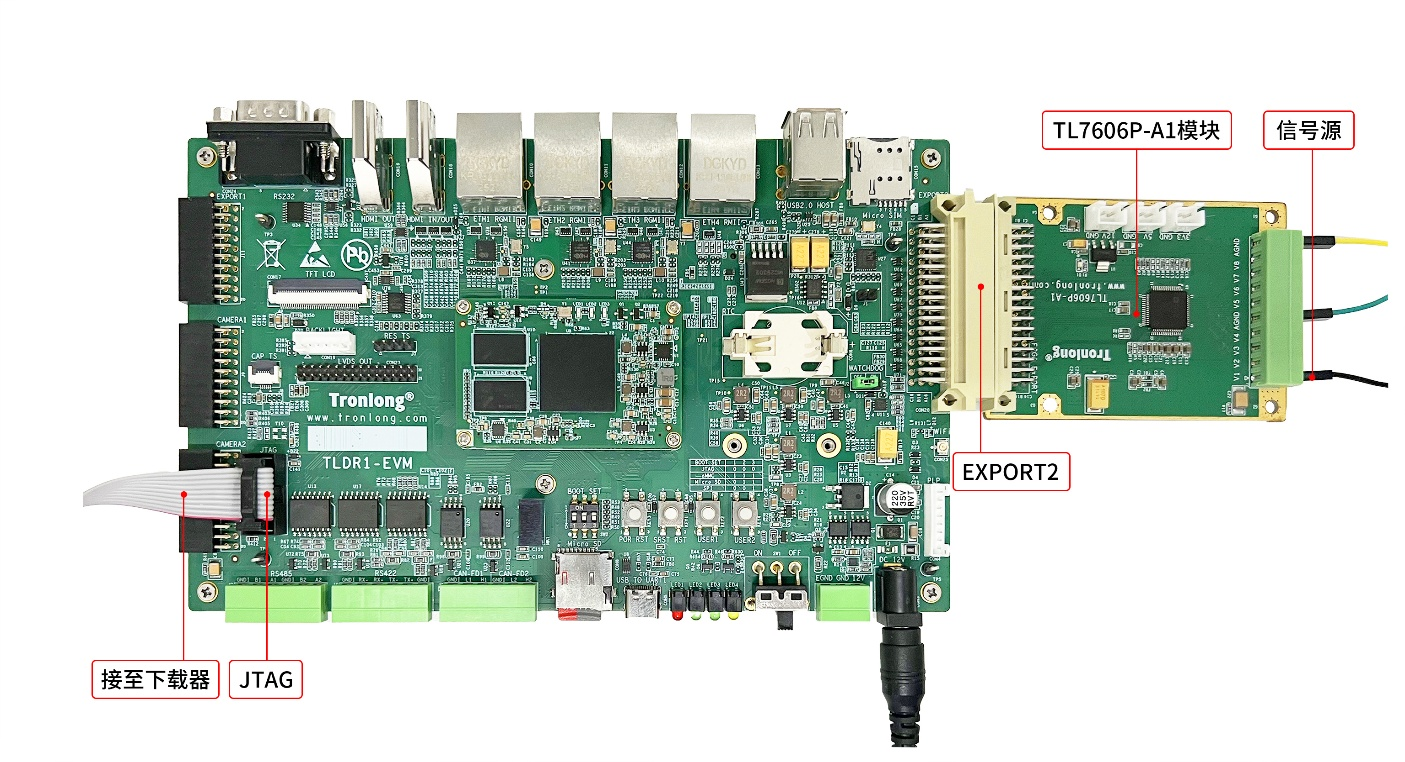

3.2 操作说明

(1)硬件连接

请将TL7606P模块连接至评估板的EXPORT2接口,将TL7606P模块的VX通道正确连接至信号发生器A通道。同时使用下载器连接评估板JTAG接口至PC端USB接口。硬件连接如下图所示。

备注:本次演示通过TL7606P模块的V1通道进行数据采集,其他通道的数据采集方法同理。

图 7

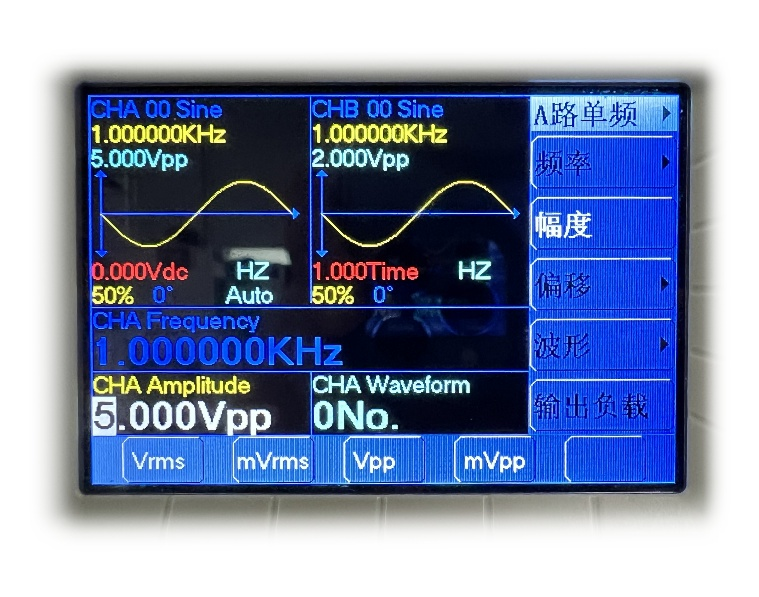

信号发生器设置A通道输出频率为1KHz、峰峰值为5.0Vpp(即幅值为2.5V)的正弦波信号,如下图所示。TL7606P模块默认量程为±5V,待测信号电压请勿超过模块量程,否则可能会导致模块损坏。

图 8

(2)运行测试

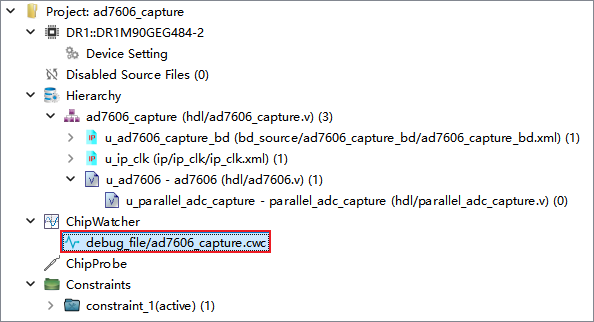

打开案例对应的TD工程,在工程编译成功后,点击"Hierarchy Navigation"栏"ChipWatcher"选项下的.cwc文件。

图 9

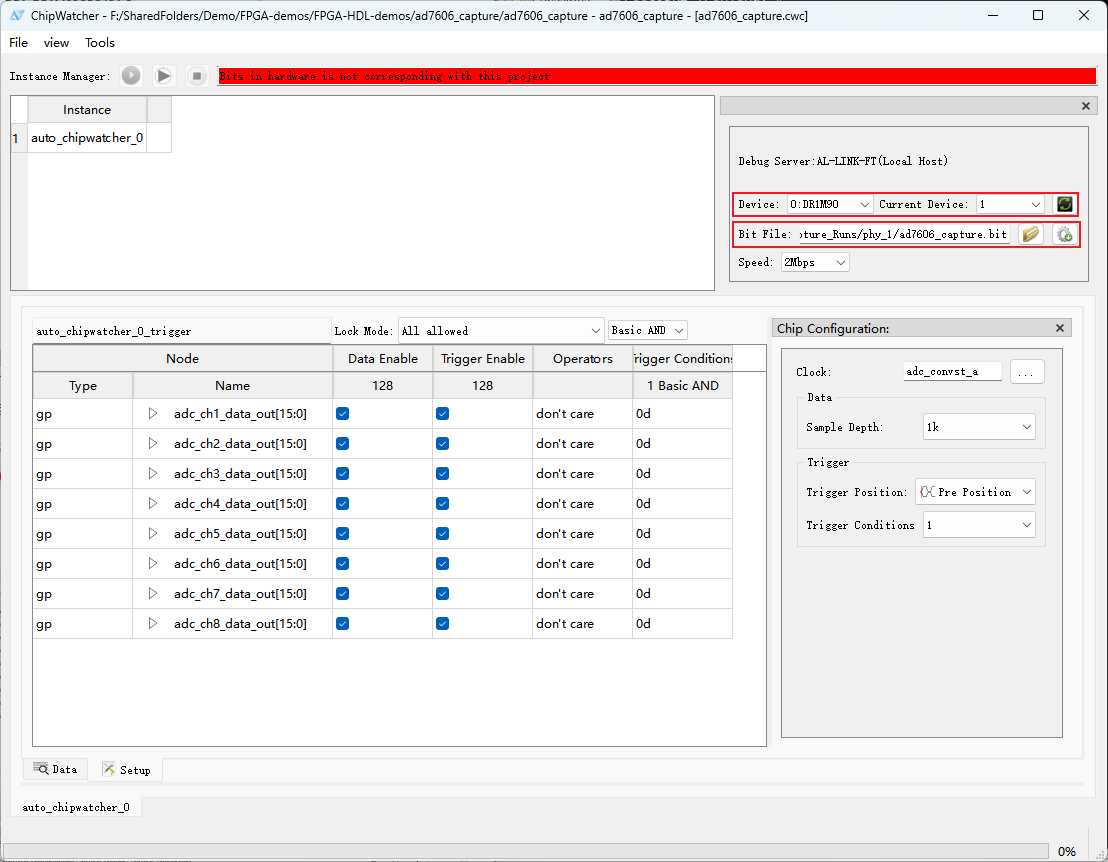

将评估板上电,点击图标,直至"Device"栏出现器件信息。在"Bite File"栏中,选择案例对应的.bit镜像文件。

图 10

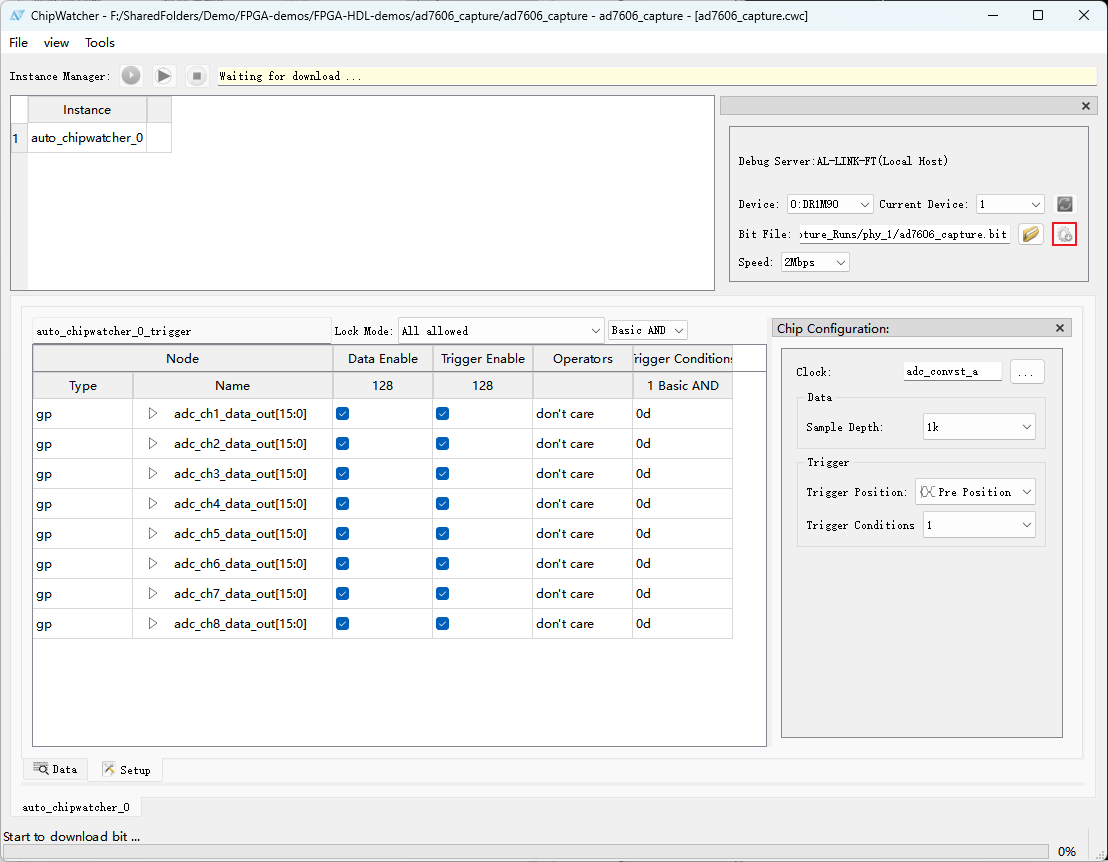

点击图标,加载.bit镜像文件。

图 11

图 12

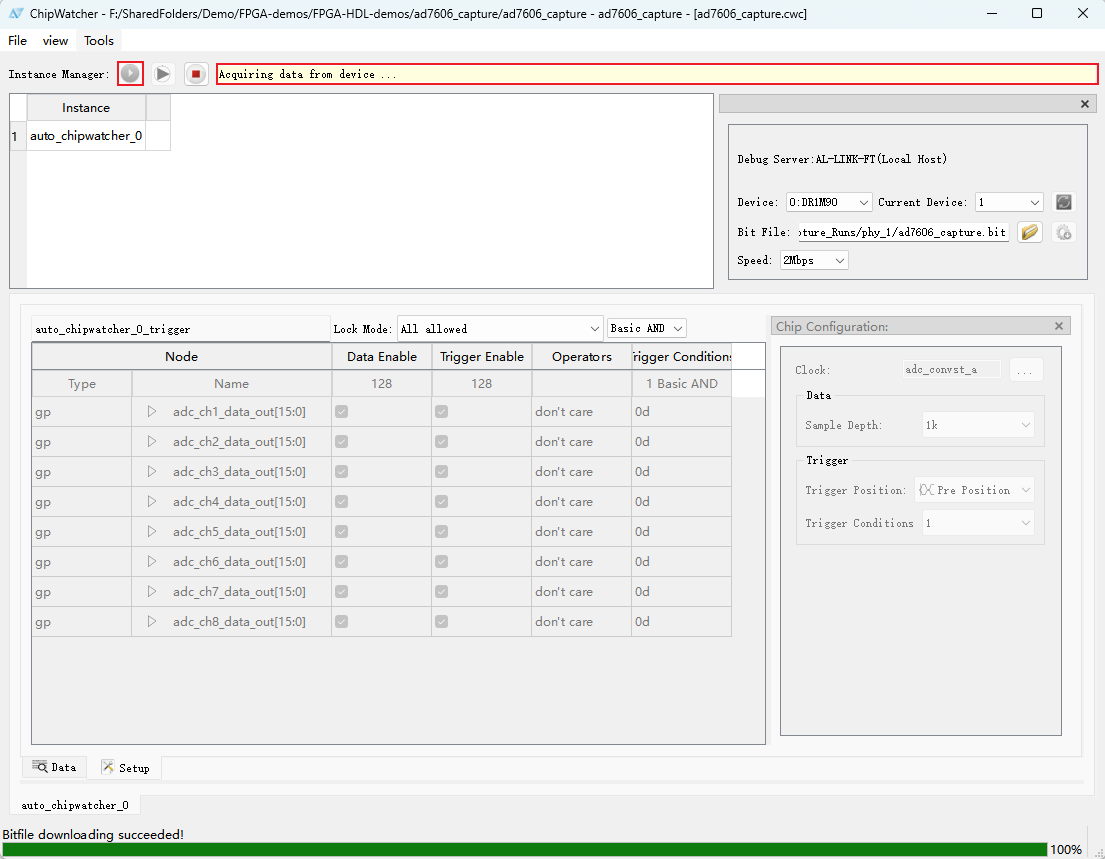

点击图标,进行单次采集,并等待采集完成。

图 13

图 14

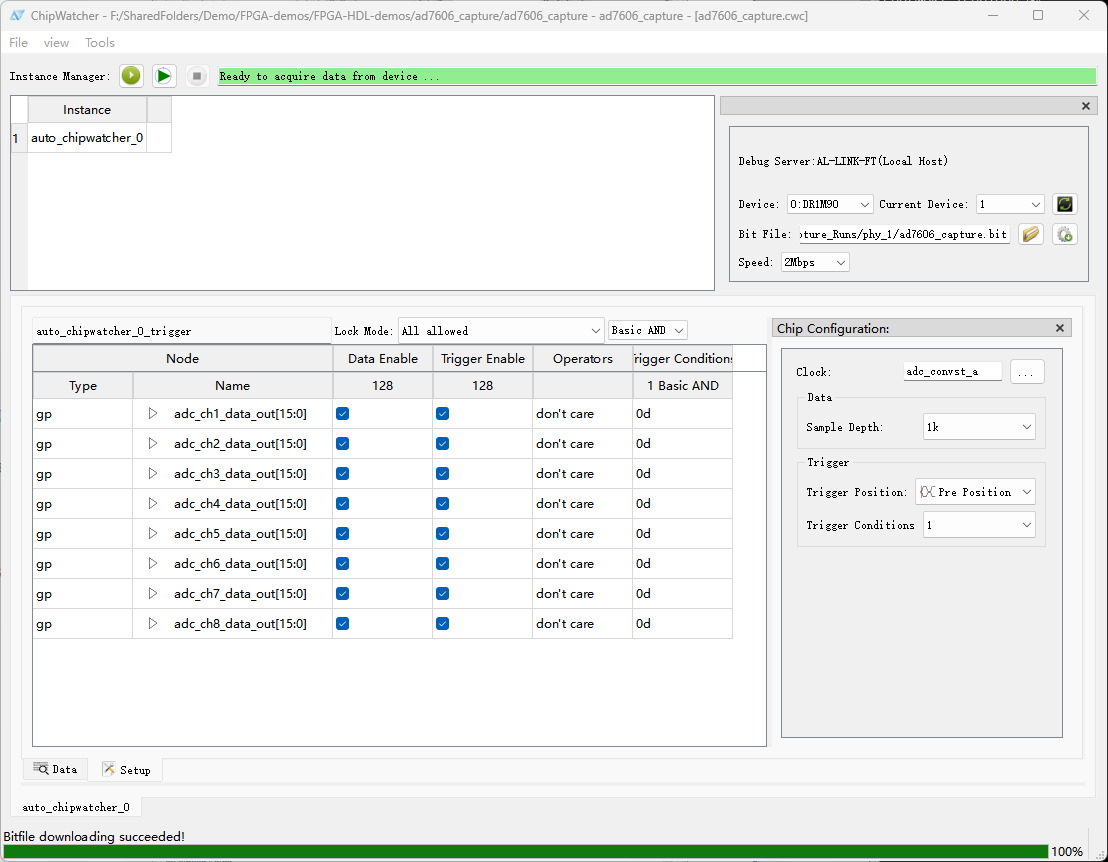

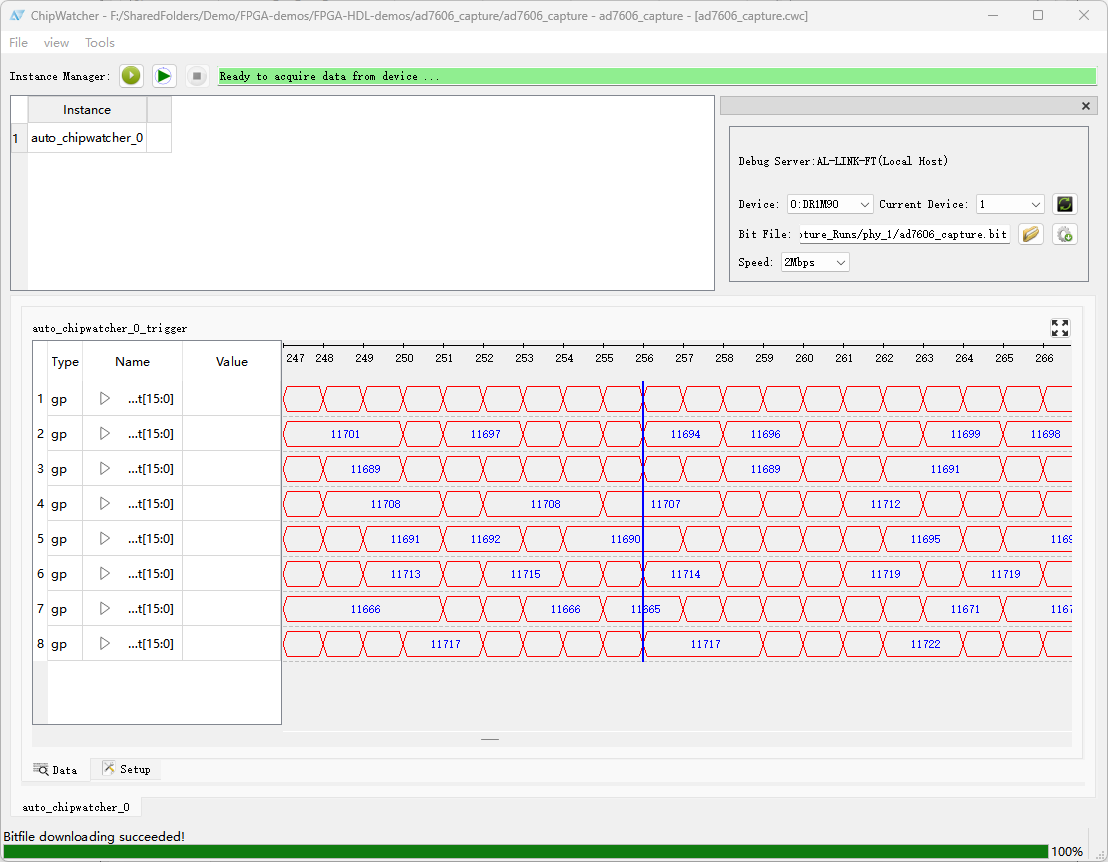

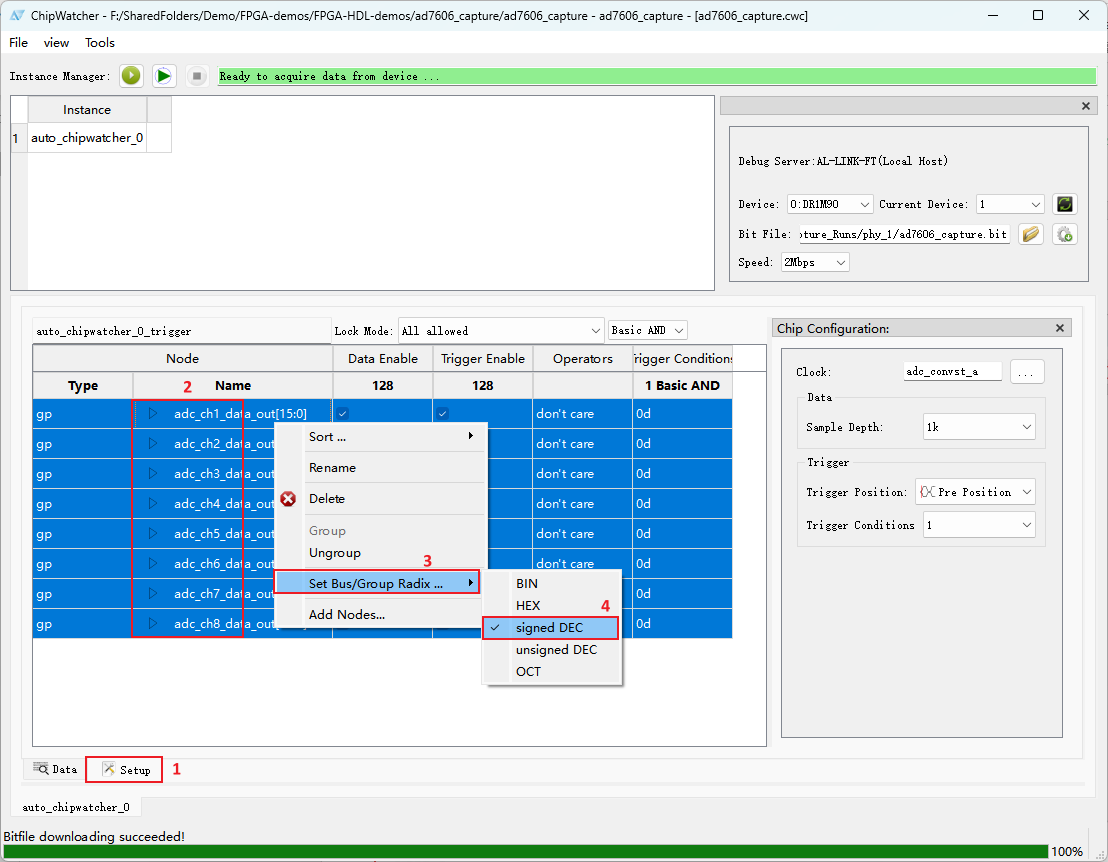

采集完成后,点击"Setup",选中要查看的数据,鼠标右键依次选择"Set Bus/Group Radix... -> signed DEC"设置波形格式为"signed DEC"(有符号十进制)。

图 15

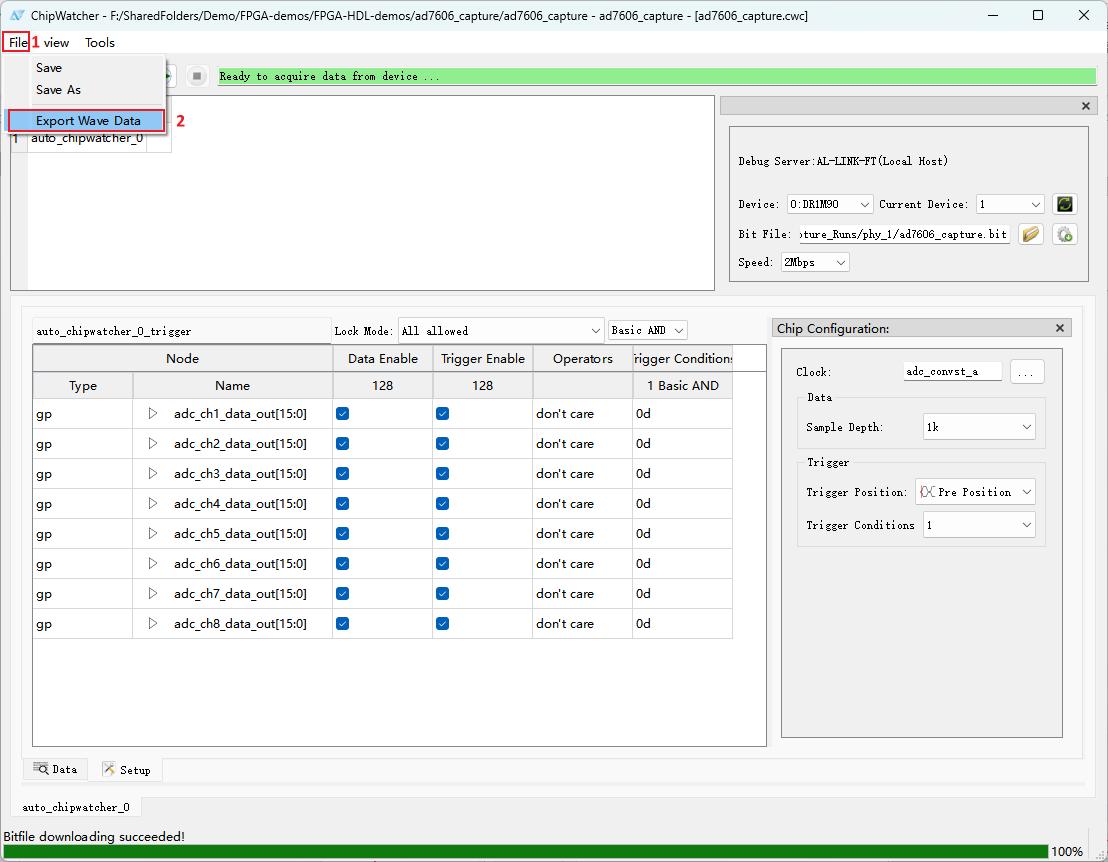

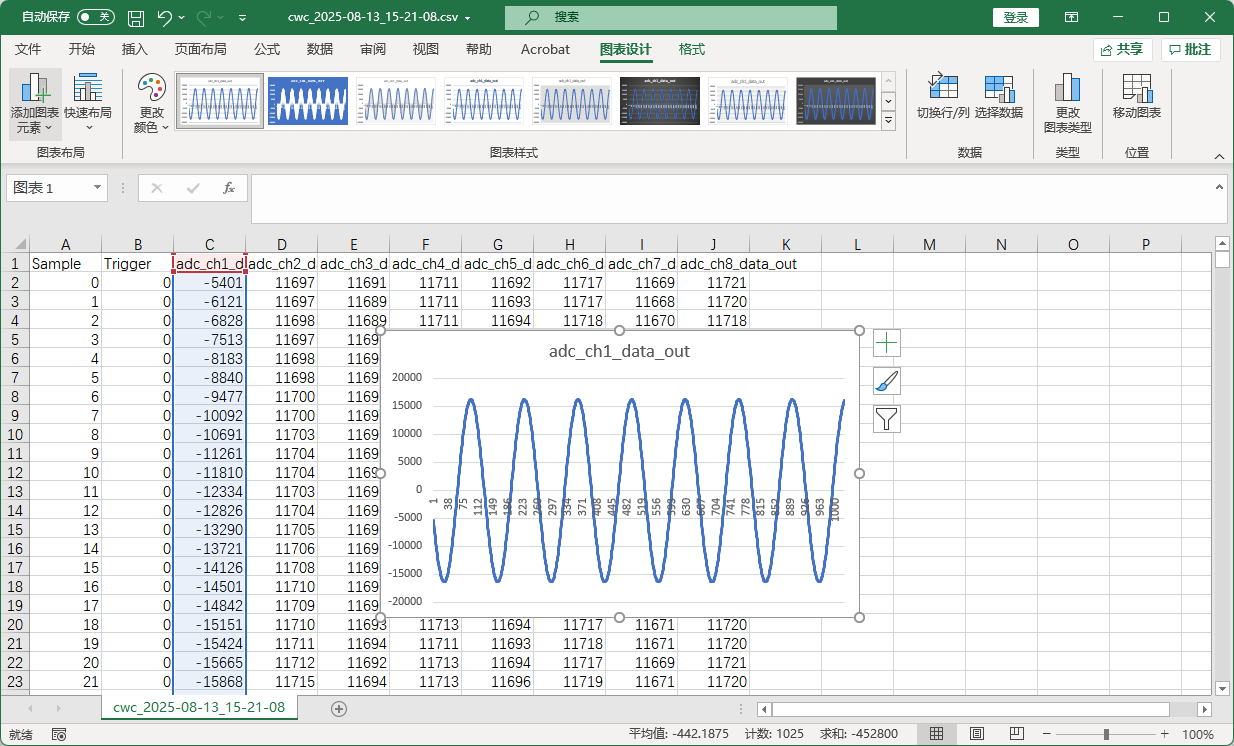

点击当前窗口右上角"File",选择"Export Wave Date",导出波形数据.csv文件。导出完成后,会弹出窗口显示导出文件的路径以及名称。

图 16

图 17

(3)结果验证

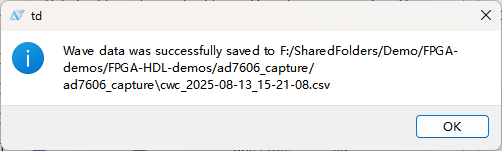

请将生成的.csv文件使用Excel打开,如下图所示。其中,第C列数据为TL7606P-A1模块V1通道的采集数据,第J列数据为TL7606P-A1模块V8通道的采集数据。

图 18

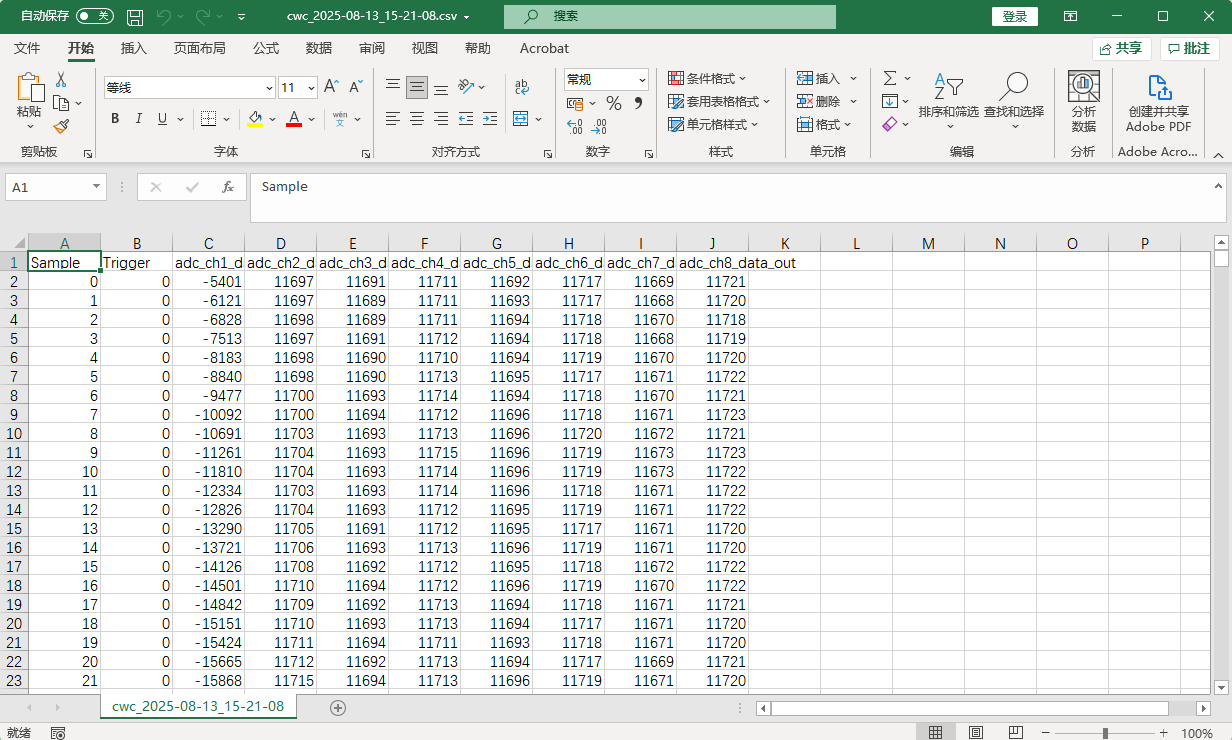

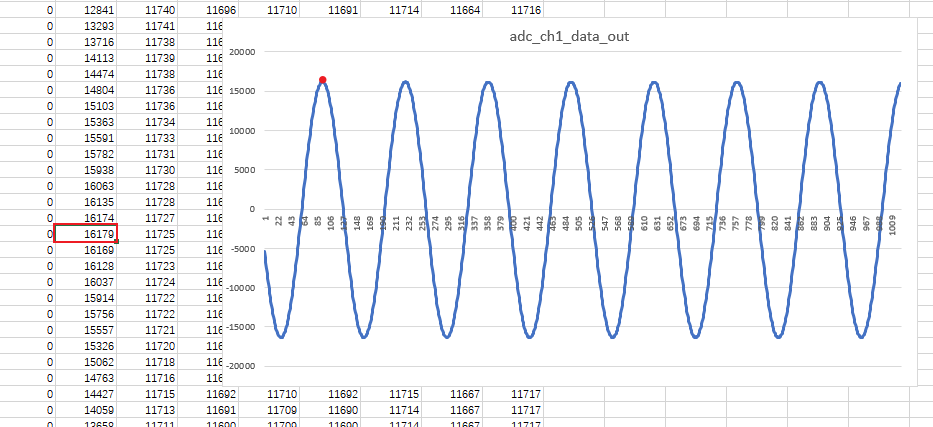

由于本次演示通过TL7606P-A1模块的V1通道进行数据采集,因此请选中表格中的第C列,点击"插入"选项,选择"折线图",将采集数据显示为更加直观的波形图,如下图所示。

图 19

图 20

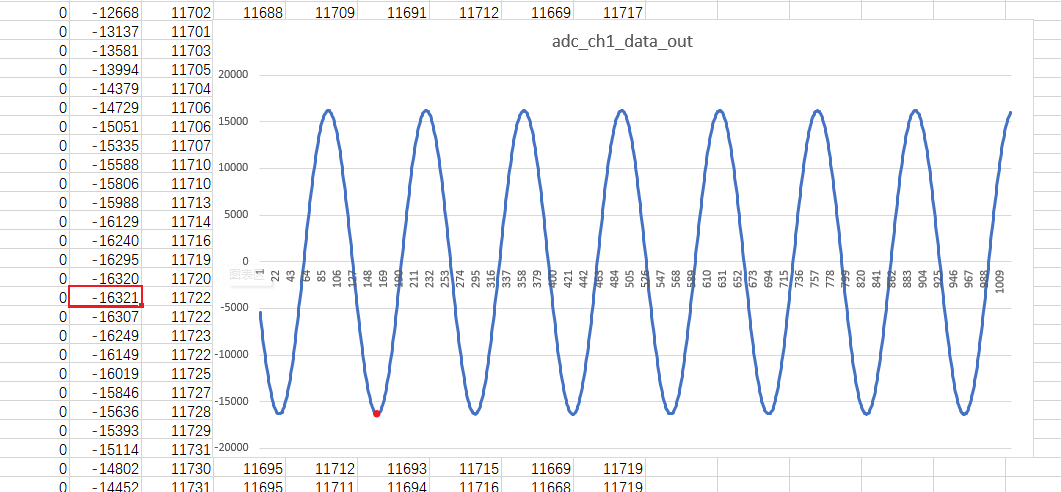

根据折线图确定波峰值为:16179,波谷值为:-16321

图 21 波峰值

图 22 波谷值

根据以上波峰值和波谷值,套用计算公式:CODE = VIN x VREF / 2n,计算可得约为4.95V,与信号发生器设置峰峰值:5.00Vpp接近。

参数解析:

VIN:输入电压,即波峰值和波谷值之和,为16179 + 16321 = 32500;

VREF:量程电压值,即为:+5V - ( -5V ) = 10V;

n:数据有效位,此处为16位。

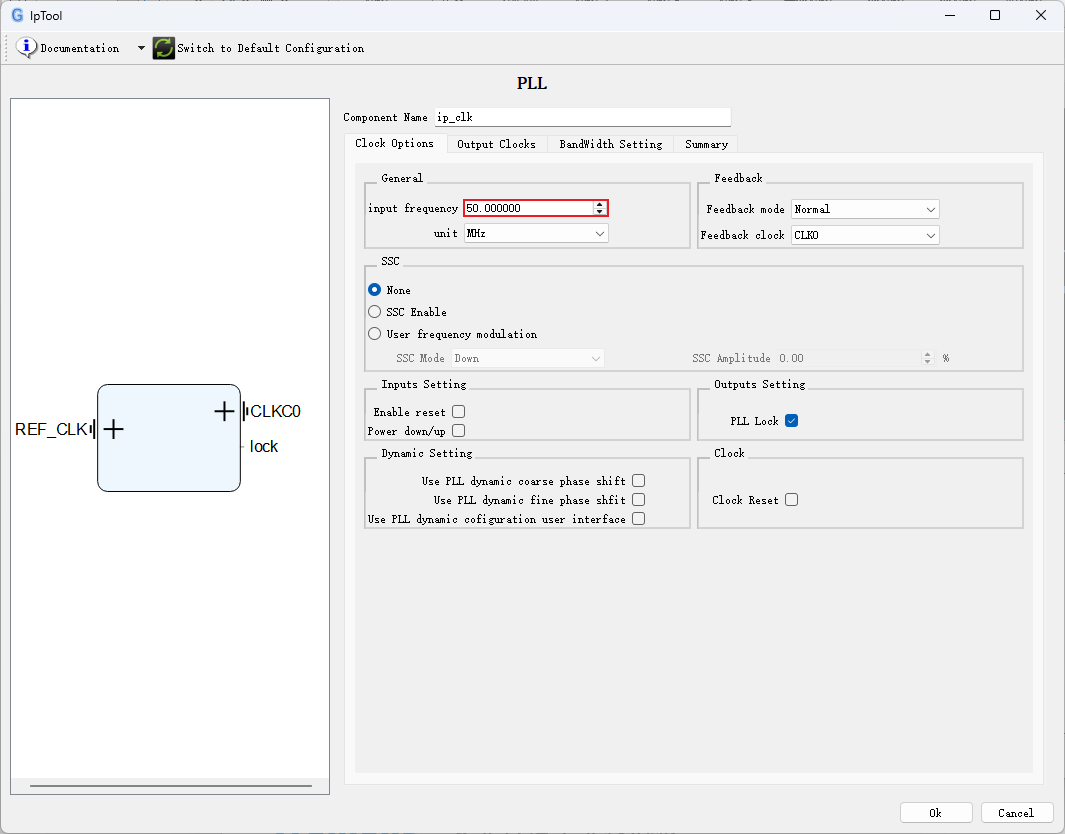

3.3 IP核配置说明

设置输入的时钟频率为50MHz。

图 23 PLL IP核配置

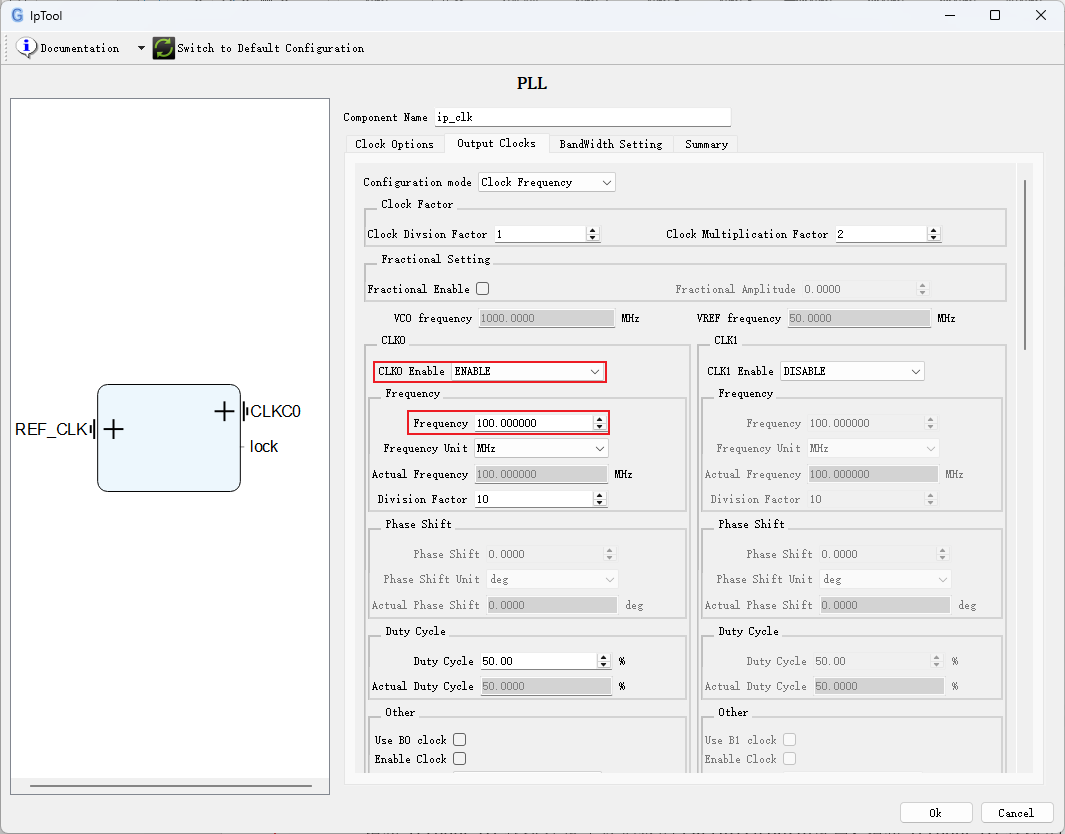

使能CLK0,配置输出频率为100MHz。

图 24 PLL IP核配置

3.4 关键代码

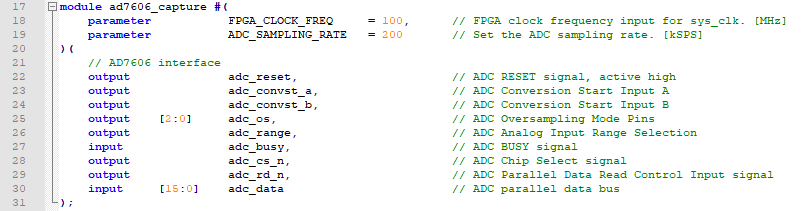

(1)顶层模块

顶层模块的源码位于案例目录"project\hdl\"下的"ad7606_capture.v"。

a)端口定义。

图 25

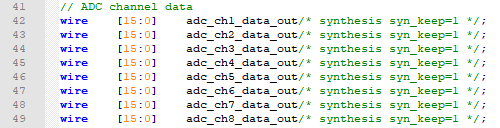

b)仿真调试信号定义。

图 26

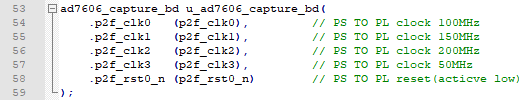

c)实例化ad7606_capture_bd模块,该模块负责从PS端产生时钟,提供给PL端。

图 27

d)使用PLL IP核输出100MHz ADC时钟。

图 28

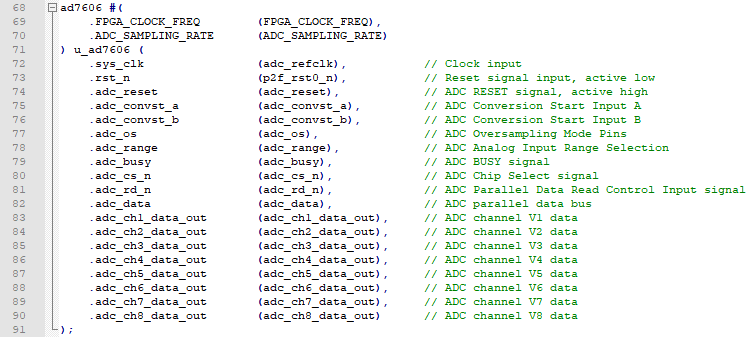

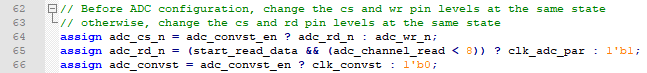

e)实例化AD7606模块。

图 29

(2)AD7606模块

AD7606模块的源码位于案例目录"project\hdl\"下的"ad7606.v"。

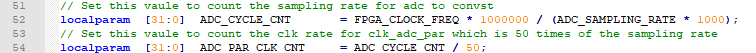

a)配置aAD7606时序信号线。

图 30

b)将采集到的数据分离给各通道。

图 31

(3)parallel_adc_capture模块

parallel_adc_capture模块的源码位于案例目录"project\hdl\"下的"parallel_adc_capture.v"。

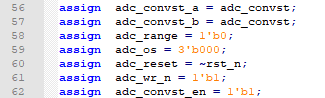

a)生成AD7606的采样时钟和读取数据的时钟,其中采样时钟为200KSPS,读取数据的时钟为采样时钟的50倍。

图 32

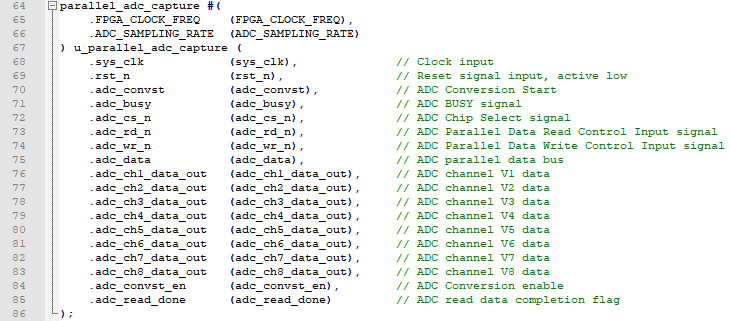

b)控制convst、cs/rd的信号。

图 33

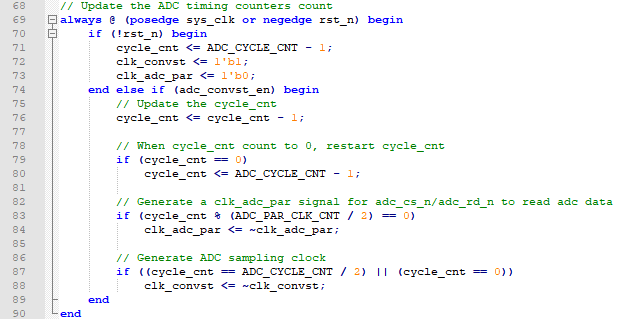

c)以100MHz时钟分频计数生成时序信号。

图 34

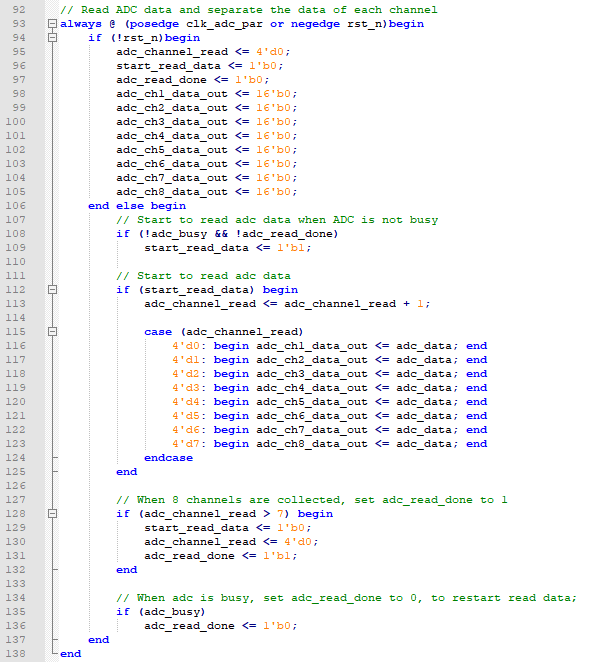

d)TL7606P模块每完成一次采样,则立刻依次读取出各通道AD数据。

图 35