瑞芯微RK3576芯片作为一款中高端的八核Arm架构SoC,引入了新一代完全基于硬件的16M像素ISP(图像信号处理器),可支持多路MIPI CSI-2视频输入。本文将基于RK3576芯片特性,介绍如何确定是否支持MIPI CSI-2的4K@60fps输入与4K输入实现技巧。

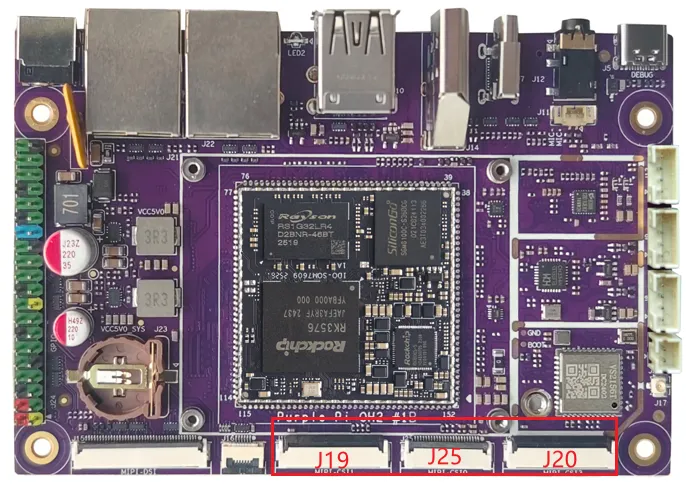

演示设备:触觉智能RK3576开发板Purple Pi OH2

MIPI CSI-2

- MIPI CSI-2协议简介

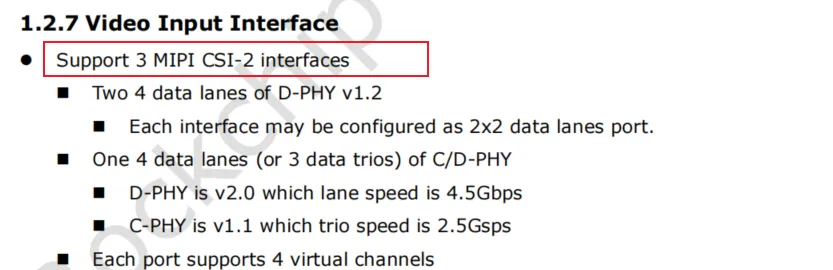

MIPI CSI-2 是 MIPI 联盟制定的嵌入式相机串行接口标准,用于图像传感器与处理器间高速传输图像 / 视频数据。RK3576平台默认支持3路MIPI CSI-2接口。

- 应用场景

触觉智能RK3576核心板&开发板根据MIPI CSI-2接口特性,广泛应用于移动终端/医疗、汽车、AR/VR、工业视觉领域。

4K@60fps输入计算方法

- 硬件参数

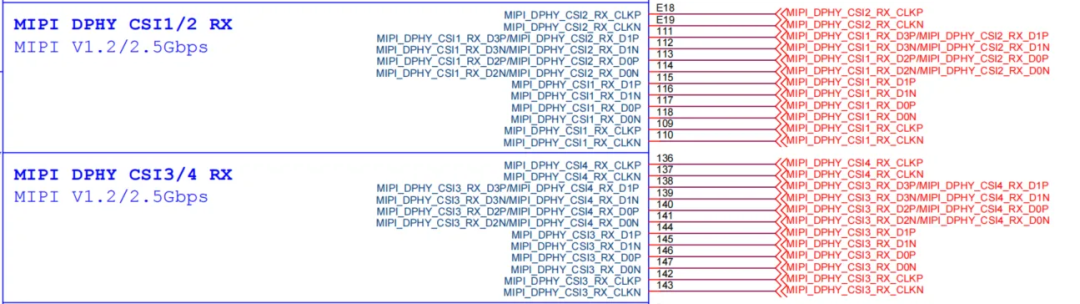

触觉智能RK3576 开发板(Purple Pi OH2),板载3路MIPI CSI-2接口(数据通道均为4lane),其中J19、J20这两路支持配置数据通道 2+2 组合,因此最多可预留5路 MIPI CSI-2 接口。J19、J20为DPHY CSI RX接口,都支持MIPI V1.2版本,每个lane通道最大传输速率为2.5Gbps。

- 裸数据带宽计算

一帧图像需要多少像素?

4K分辨率典型值:3840 x 2160 = 8294400像素一帧的数据量是多少?

8294400 x 24 ≈ 199 Mbit/帧一秒的数据量是多少?

199 x 60 ≈ 11.94 Gbps总结:理论裸数据开销数据量约12Gbps(未算上协议开销,仅像素本身需要的带宽)。

- MIPI CSI-2 数据通道带宽计算

以RK3576的MIPI CSI-2接口为例, 单lane通道标称速率2.5 Gbps,最高支持4lane

理论带宽计算:

2.5Gbps × 4Lane= 10Gbps从计算结果上看无法满足4K@60fps需求,至少需要5lane。

11.94 ÷ 2.5 ≈ 4.78总结:对于MIPI CSI-2标准lane数据通道数据量是1/2/4/8,并不存在5lane的说法。因此4lane的MIPI CSI-2接口无法满足4K@60fps的带宽需求、通常需要8lane或更高速方案。

4K@60FPS实际占用与4Lane实现方法

前面计算的都是裸数据需要的带宽,而实际传输数据还有协议开销,主要包含如下:

a. 包头

b. 包尾

c. ECC校验

d. 空行 / 空帧

业内经验的带宽开销计算:实际链路带宽 = 理论像素带宽 × 1.2~1.3

11.94 Gbps × 1.25 ≈ 14.9 Gbps从计算来看4K@60fps实际开销接近15Gbps。

- 4K@60fps规避&4Lane实现4K输入方法

从前面计算可知当前的4K@60fps无法使用4lane进行实现,若要使用4K分辨率如何在4 lane的基础上满足需求?触觉智能根据实测,提出了2套解决方案:

(1)方案1:降低像素位宽

RGB888 → YUV422/RAW10,使每像素从24 bit → 10~16 bit,对应的带宽直接砍半。参考命令:

8294400 x 10 ≈ 79.1 Mbit/帧

79.1 x 60 ≈ 4.64 Gbps

4.64 x 1.25 ≈ 5.8 Gbps(2)方案2:降帧率

比如60fps → 30fps,这种方式最简单有效,但会影响帧率,对应高帧率要求的项目需要评估风险。参考命令:

199 x 30 ≈ 5.83 Gbps

5.83 x 1.25 ≈ 7.29 Gbps