当你触摸手机屏幕时,是否想过,这个看似简单的动作背后,其实是一场纳米级的静电防御战?静电放电(ESD)------这个在日常生活中表现为微小电击的现象,在半导体世界里却是以千伏计的"微型闪电",足以瞬间击穿价值数百万的芯片。本文将以智能手机为载体,揭开ESD防护从晶圆到用户手中的全链路技术体系。

第一道防线:芯片级的纳米防御艺术

在智能手机主处理器、射频芯片和内存的电路设计中,ESD防护从微观层面展开。每个I/O端口都设有片上ESD保护电路,如同"智能门卫"。

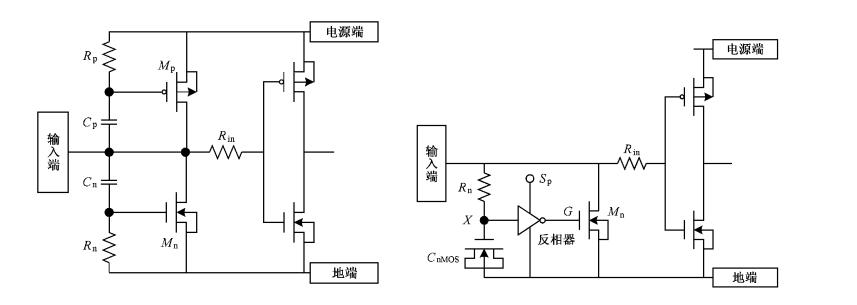

以栅极耦合NMOS(GCNMOS)为例:ESD事件发生时,瞬间高压通过电容耦合抬升栅极电压,使晶体管迅速导通,在皮秒级时间内为静电电流提供低阻抗泄放路径;正常工作时(1.8V/3.3V),则保持高阻抗,几乎不影响信号。

图1 栅耦合型MOS管ESD保护结构 (左)gcMOS,(右)MC-gcMOS

在5nm等先进制程中,氧化层仅数十原子层厚,击穿电压显著下降。工程师采用多级防护策略:第一级选用触发精准的硅控整流器(SCR),第二级搭配尺寸优化的NMOS/PMOS对,形成从"快速响应"到"主力泄放"的梯次防御体系。

第二战场:制造环境中的静电管控

在芯片制造中,即使芯片自带防护,ESD威胁仍无处不在。价值数万美元的12英寸晶圆,一次静电火花就可能导致整批失效。

车间的防护是多维的:空气电离系统持续中和电荷,维持静电电压低于50V;工作台面使用耗散材料,确保电荷缓慢释放;操作人员必须穿戴防静电服、接地手环和专用鞋,将人体电压控制在100V以下。

图2 防控静电车间

封装测试环节同样关键。芯片在切割、键合时,机械接触会产生摩擦静电。先进封装厂会监控各工站的实时静电电压,并采用接触放电小于25V的专用工具。测试中,自动化设备会在接触引脚前先实现电位均衡,避免"带电接触"。

第三重防护:系统级的协同防御

芯片装至主板后,系统级ESD防护随之启动,这是手机抵御用户触摸、插拔等静电的最后屏障。

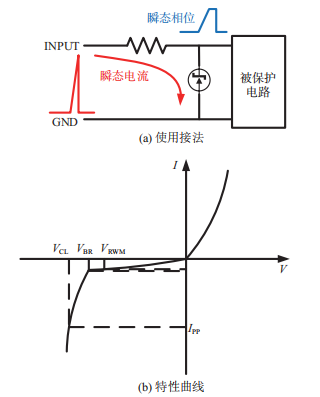

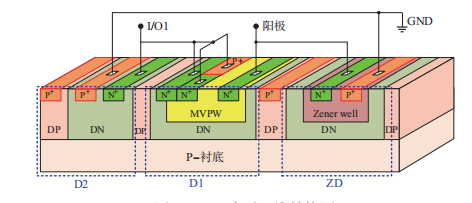

手机接口(如USB-C)会设置瞬态电压抑制器(TVS),其响应达纳秒级,遇过压即从高阻切换为低阻,将电流导向地线。现代手机采用的多通道TVS阵列可同步保护多条数据线,尺寸不足1mm²。

图 3 TVS的使用接法和特性曲线

图4 TVS阵列三维结构图

手机内部布局亦含巧思:敏感电路远离接口,关键信号线以地线"包地"屏蔽。金属屏蔽罩既阻隔电磁干扰,也形成等电位面,防止电荷积聚。

此外,电路板上的"火花隙"可在特定位置(如SIM卡槽旁)设置尖锐导电极,间距经精密计算。当电压达到危险值时,电极间优先产生可控放电,从而保护后方电路。

用户日常操作是ESD的最后一道考验。

冬季干燥时人体静电可超15kV,远超芯片通常2kV-8kV的防护等级,这要求手机必须具备系统级ESD抗扰度。

图5 日常人体静电

当手指触摸屏幕,静电会通过表面涂层分散到ITO导体层,并导至屏幕边缘的接地环。触摸IC内置ESD检测电路,可在放电后自动复位,防止失灵。

充电接口的防护尤为关键。优质手机会在VBUS、数据线和CC引脚均部署TVS二极管,实现全方位保护。部分设计还会在接口处加入微小电感与电阻,用以减缓ESD脉冲的上升速度,为保护器件争取响应时间。

从晶圆厂的超净车间到用户手中的日常设备,ESD防护贯穿了智能手机的全生命周期。这不仅仅是技术细节,更是半导体可靠性的基石。每一次成功的触摸响应、每一次稳定的数据传输,背后都是多层防护体系的精密协作。

在电子产品愈发精密、制程不断微缩的时代,ESD防护已从"必要措施"演变为"设计哲学"。它提醒我们:人类科技的前沿,始终在与最基本的物理现象进行着微观尺度的对话。而这场对话的成果,最终守护着数字世界的每一个比特,让无形威胁永不成形。