HDMI简介

- [1 HDMI引脚](#1 HDMI引脚)

- TMDS传输原理

- [2 传输流程](#2 传输流程)

- [3 传输周期](#3 传输周期)

- [4 Data Island Packet结构](#4 Data Island Packet结构)

- [5 Audio Clock](#5 Audio Clock)

- [6 HotPlug](#6 HotPlug)

- [7 HDMI Sink](#7 HDMI Sink)

- [8 Timing Detect](#8 Timing Detect)

- [9 HDMI版权内容保护HDCP](#9 HDMI版权内容保护HDCP)

- [10 HDMI Sink总流程](#10 HDMI Sink总流程)

- [11 HDMI的时钟与带宽](#11 HDMI的时钟与带宽)

-

- [11.1 像素时钟](#11.1 像素时钟)

- [11.2 理论带宽](#11.2 理论带宽)

- [11.3 TMDS时钟](#11.3 TMDS时钟)

- [12 EDID](#12 EDID)

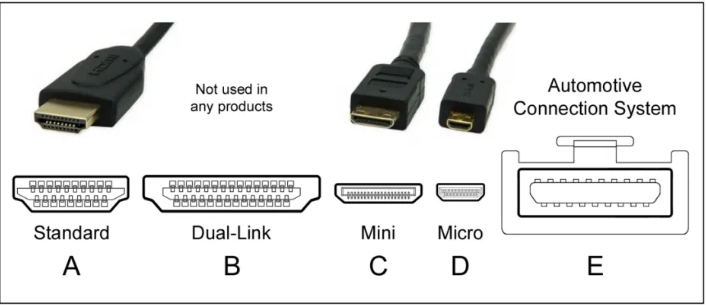

1 HDMI引脚

HDMI有A\B\C\D\E五种引脚类型

目前市面上比较常见的是Type A

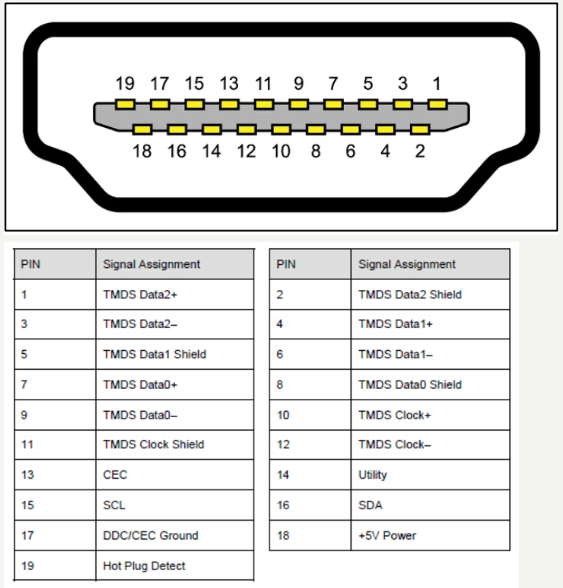

- TMDS Data0/1/2(1-9脚):共3对为数据传输实际上用到的脚,用TMDS编码格式

- TMDS Clock(10-12脚):共1对TMDS时钟线,为TMDS时钟信号

- CEC(13脚):HDMI的CEC通道引脚,可以通过CEC信号控制HDMI接口上所连的设备。(类似一种扩展的HDMI功能,供厂家自己定制HDMI消息,(比如说你有一台sony的DVD与TV,两者用HDMI线接上,如果你用TV的遥控器可以控制DVD,另DVD执行某种功能,那么该功能的命令信号就是通过TV与DVD间的CEC引脚传输的)

- 14脚为保留引脚,未使用(也可以为CEC多提供一个脚)

- IIC(15-16脚):用于DDC(Display Data Channel,主要用于EDID与HDCP的传输)传输。在HDMI流程中,DDC通信几乎是最先做的(此前有Hotplug),因为HDMI的主从设备需要通过DDC来获得对方设备的EDID,从而获得各种信息,并且通过比较timing以确定之后送出的timing为最合适的。

- 17脚为接地引脚

- 18脚为5v的AC引脚

- 19为Hotplug(热插拔)引脚:用于检测HDMI设备有没有存在,如果存在(Hotplug为High)那么可以通过DDC去读EDID),HDMI有规定在HDMI 5vAC断电时source device可以读reciever device的EDID,也就是需要Hotplug为High。其中有两种Hotplug相关的情况会导致HDMI被识别为DVI:

- Hotplug为High,不过EDID并没有准备好,那么信号源设备会由于无法读到EDID而认为接收设备为DVI,这样会导致HDMI有图像无声的问题。

- Hotplug为Low,也会导致信号源无法读到EDID而认为接收设备为DVI,从而导致HDMI有图无声。

- 在TV这种有多个HDMI通道的情况下,有时会在多个HDMI通道进行切换,切换后HDMI通道应当先初始化,即先把Hotplug拉低,通知HDMI source device之前所用的EDID已经改变,需要重新读取,那么source device在Hotplug被拉高的时候会去读取新的EDID,但是拉低这个过程至少需要100ms,否则source device有可能不会去读取新的EDID,从而输出DVI信号。

TMDS传输原理

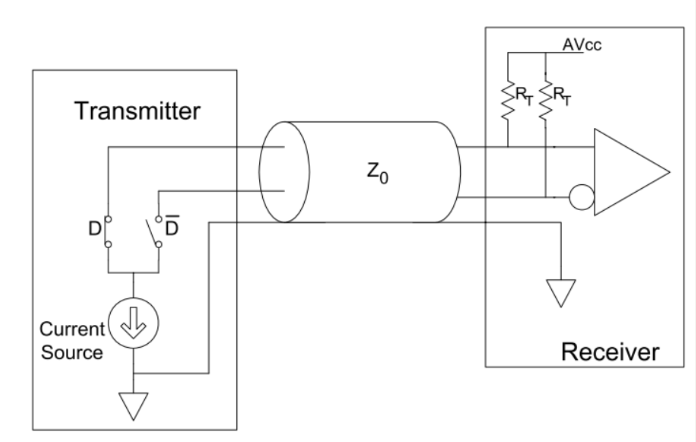

电路结构

TMDS 通过差分信号传输数据,其电路由发射端(Transmitter)和接收端(Receiver)组成,关键设计如下:

- 发射端

- 恒流源:10mA 恒流源驱动差分对(D+和D-)。

- 开关控制:通过导通/断开切换电流路径,改变差分电压极性。

- 接收端

- 上拉电阻:两个 50Ω 电阻(RT)将差分信号上拉到 3.3V(AVcc)。

- 高阻抗输入 :接收端输入阻抗极高,电流几乎全部流经 RT。

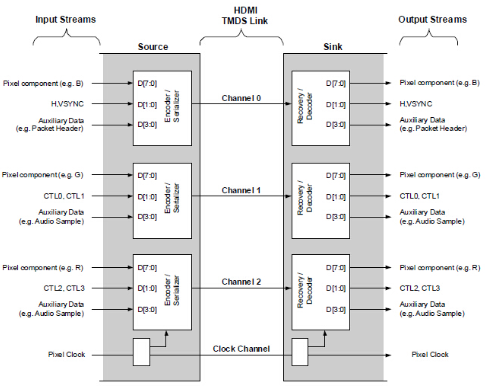

2 传输流程

HDMI TMDS传输的数据类型有三种(加上Hsync与Vsync就算4种):

- Preamble(控制信息),主要用于控制接下来传输的数据是Data Island或者Video Data

- Data Island(数据包),各种类型的包信息,包括音频数据包,图像信息包等

- Video Data (视频信息),视频像素数据,HDMI可以传输RGB与YUV两种格式的像素数据

- 还有Hsync与Vsync

TMDS一个通道由2根差分线来传输信号,信号的"0"和"1"由两根线的电压差来决定:

- TMDS差分线+为高电平 TMDS差分线-为低电平 => 1

- TMDS差分线+为低电平 TMDS差分线-为高电平 => 0

HDMI的数据传输有TMDS0、TMDS1、TMDS2三个通道,每个通道的传输流程都是一样的。

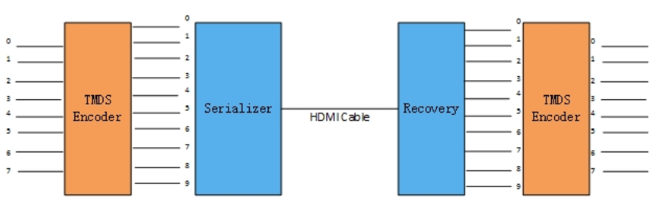

如果是8bit的数据进入TMDS编码器,得到抗干扰性强的10bit TMDS信号,然后再进行串行化输出;在接收端收到串行的HDMI信号后,进行信号复原,得到10bit的TMDS信号,最后用TMDS解码器解码得到原来的8bit数据。

总体传输流程如下:

1、如果传输的是Video Data,并且格式为RGB,那么会占用三个通道的所有24bit输入,Channel0[7:0]用于传输B分量,Channel1[7:0]用于传输G分量,Channel2[7:0]用于传输R分量。

2、如果传输的是Data Island,则占用三个通道共10bit输入,Channel0[3:0]用于传输Data Island Header(包头),Channel1[0:3]与Channel2[0:3]用于传输Data Island Content(包内数据)。

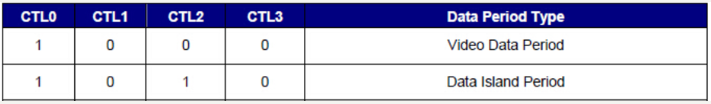

3、如果是Preamble传输,则占用1,2两个通道共4bit输入,Channel1[1:0]与Channel2[1:0]分别为CTL0,CTL1,CTL2,CTL3,用于判断接下来输入的是Video Data或者Data Island

对于Hsync与VSync,会占用Channel0通道的两个bit输入,Channel0[0]为Hsync,Channel0[1]为Vsync

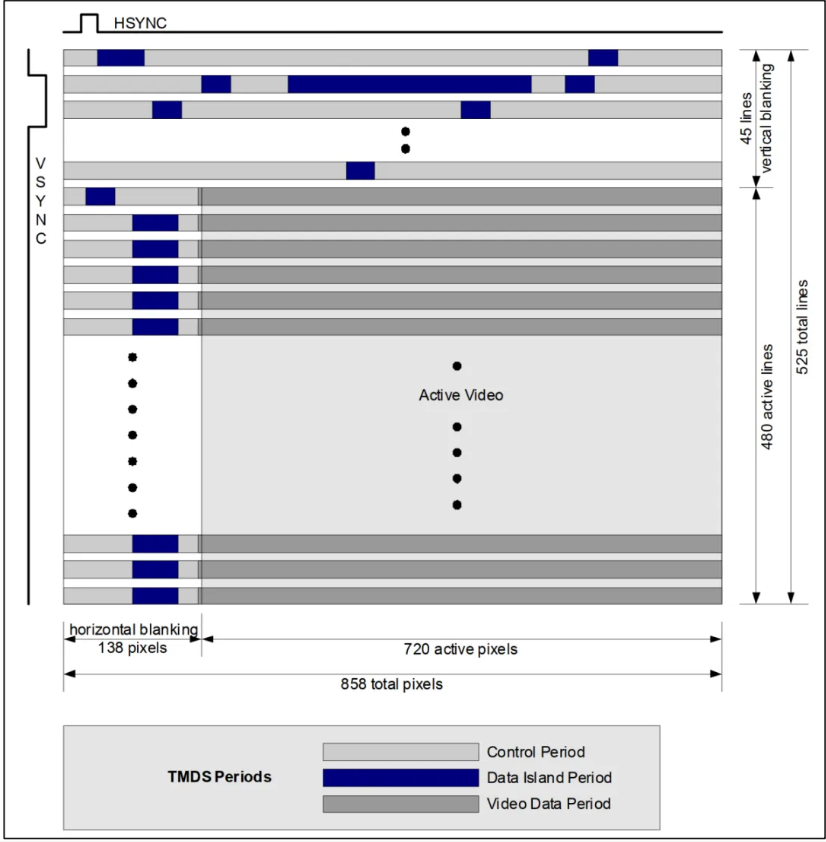

3 传输周期

HDMI的TMDS数据传输可以分为三个传输周期

- Control Period:(控制信号传输阶段)期间会传输Hsync,Vsync,并且在该时期的最后阶段会传输Preamble。

- Data Island Period:(音频和额外数据传输阶段)期间会传输Data Island(数据包),也会有Hsync与Vsync。对应D[3:0]会将4bit的数据串行化为10bit发出。

- Video Data Period:(视频数据传输阶段)期间会传输Video Data(视频像素数据)。此阶段传输实际的图像数据。对应D[7:0],会将8bit的数据编码并串行化为10bit发出

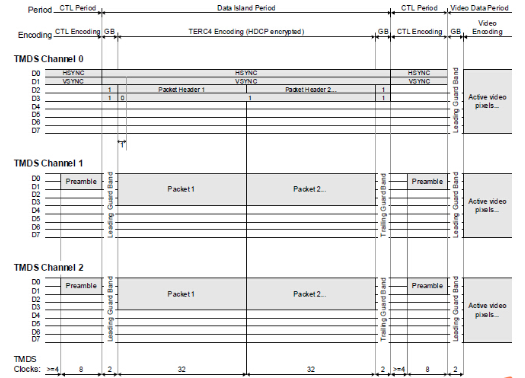

三个传输周期过渡如下:

1、左边是Control Period,传输有Hsync,Vsync与Preamble

2、中间是Data Island Period,传输有Hsync,Vsync,以及两个Packet Header与Packet(每32个clock 一个packet);另外Data Island的两端会用Guard Band保护并隔开Data Island的数据,因为这个阶段传输的数据大多是非常重要的,比如其中就有图像分辨率,决定后面的Video Data数据的显示方式

3、右边是Video Data Island,传输视频像素数据,在该时期的开头也有Guard Band

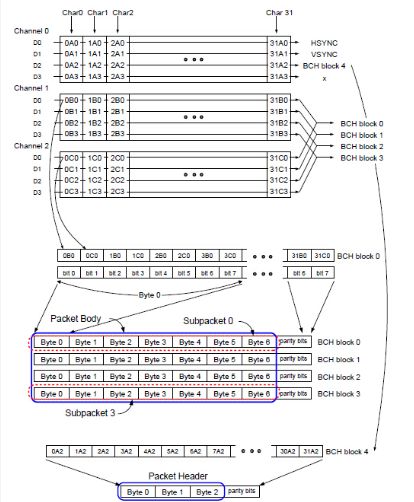

4 Data Island Packet结构

所有Data Island Packet都以32个时钟脉冲为一个周期,也就是说每32 clk传输一个包。

以上图为例,

- 包头部是BCH block 4,由Channel0[2]传输,32clk表示有32bit,则为4byte,前三个byte为包头,最后一byte为校验码

- 包体为BCH block 0,1,2,3,分别由Channel1,Channel2共8根线传输,共有24byte与6byte的校验码

- Parity Bits校验码是用于检验HDMI Cable传输过程中是否发生了错误,如果该Packet在HDMI接收端校验错误,如果只有一个bit的错误,那么可以修正,超过1bit的错误会被判别为无效Packet(由于HDMI是一直在发送数据因此无法重发错误Packet?)

所以说,在接收端,在解完包之后,需要取出各个BCH block的Parity bit,进行Calibration(校验)

Packet类型各种各样,详细请看HDMI Spec

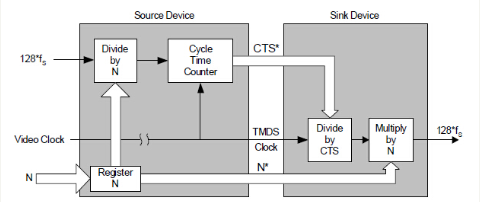

5 Audio Clock

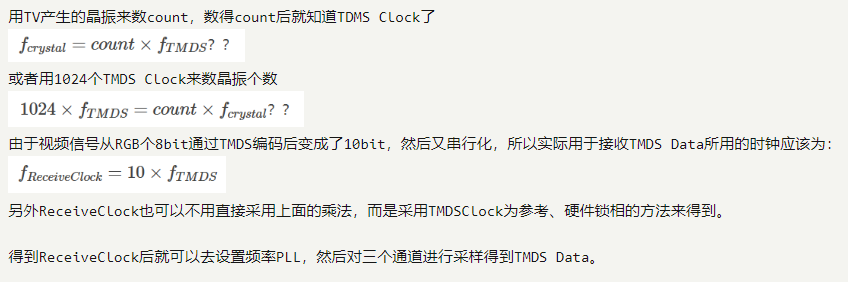

Audio的采样率有44100,48000,192000等,是各种各样,在HDMI传输时,Audio是PCM级(无压缩)传输,把PCM数据打散到各个包内,为了得到每个音频帧的数据,也需要知道Audio的采样率。HDMI中规定Audio的传输方式:

Audio采样率fs重建依靠的主要参数为:

- TMDS Clock

- CTS

- N

在发送设备这端,已知参数有采样率fs,视频时钟Video Clock(TMDS clock),以及预先设定好的参数N,求CTS:

在接收设备这端,TMDS clock通过硬件设备可以得到,N与CTS通过Audio Packet传输过来,求fs:

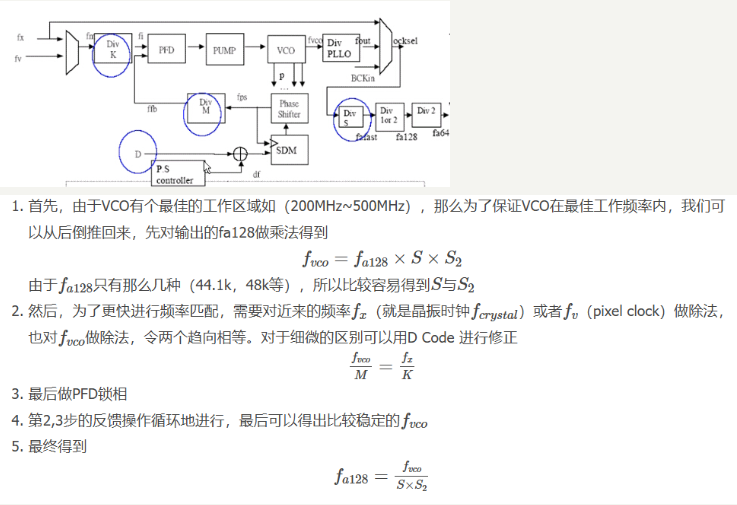

在接收端为了保持fs的稳定与精确,需要进行锁相,即用VCO(Voltage-controlled oscillator压控振荡器,通过电压控制产生的频率)产生合适的频率,然后用PFD(Phase Frequency Detector)来锁频

6 HotPlug

HotPlug即热拔插,当接上接口时就可以判定设备是否存在,以进行后续工作。

HDMI source device(HDMI HPD)会监测sink device的Hotplug端口,如果Hotplug为High,则证明设备可以工作,然后去读取DCC,如果为low,则证明设备已断开。

HDMI sink device应该通过把Hotplug拉低,来通知source device EDID已经被改变,那么source device在Hotplug被拉高后,就会重新来读取新的EDID,拉低这段时间应该多于100ms。

HDMI规定,HDMI 的5v引脚通电时,可以通过DCC去读取EDID,即需要保证Hotplug为high。

7 HDMI Sink

例如像TV这种就是HDMI的接收端,那么HDMI接收端需要做些什么东西。

HDMI可以接收到的有三个通道的TMDS Data,TMDS Clock,可以设置Hotplug,还有DCC传输用的I2C引脚。上面已经讲了TMDS Data,与设置Hotplug,接下来分析TMDS Clock。

TMDS Clock 就是Pixel Clock,即一个像素点所用的时钟频率。TMDS Clock通过clk 引脚传输到接收端,但是接收端并不清楚发送端发过来的TMDS Clock 频率为多少,因此需要通过Phy(PHY是模拟数字转换部分,不同于ADC,PHY是不知道采样频率的,需要自己锁频、锁相,侦测确切的输入频率)来进行锁相得到。但是由于HDMI频宽太宽(480P@60Hz为25.2MHz,1080P@60Hz为162MHz,甚至还有高达340MHz的),一般VCO(压控振荡器,通过电压控制产生的频率)无法覆盖这么大的范围,因此需要分频带来设置Phy:

先侦测输入频率落在哪个频带,然后根据不同频带做不同设置。

8 Timing Detect

在Sink端还有需要进行Timming Detect,因为如果设备可以支持(如chroma),HDMI可以自由更换Timming,而当Timming更换了之后,Sink需要重新设定Phy。因此,通过侦测频率的改变来检测是否更换了Timing是必要的。一般会有一个中断服务(或循环)线程来侦测频率的改变,一旦频率改变后,该进程会通知重新设定Phy,保证HDMI的正确运行

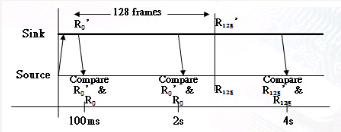

9 HDMI版权内容保护HDCP

HDCP通过DDC传输

HDCP主要用于版权视频的保护,举例来说,如果有一台蓝光DVD播放机可以播放blueray DVD,并且该DVD已经获得HDCP授权,你现在想把该DVD影像输出到某台TV,但是该TV没有获得HDCP授权,那么该TV可能就没法播放影像,或者播放质量下降,如出现雪花,图像从1080p变为480p,或者没有声音,都有可能。

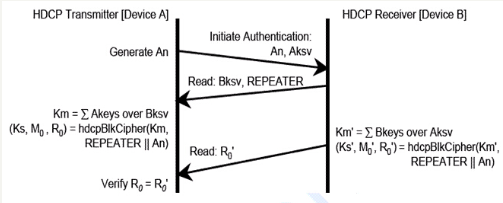

HDCP是靠两个设备的交互进行HDCP授权认证的,认证流程如下

-

Transmitter会发送一个key An(64bit)与Aksv(key selection vector 40bit)给Receiver

-

Receiver接收到An后,也会发送一个Bksv以及REPEATER(表明B设备是否为Repeater设备)给Transmitter

-

Transmitter开始HDCP认证码算法:

要理解算法,首先我们需要知道ksv是用来干嘛的

- 在每个HDMI设备内部,都会保存40组64bit的key,key[40]

- 40bit的kvs,每一个bit都是一个索引,当kvs的某一位n为1时,会把key[n]取出来,

- 把所有的key[n]相加,得到km,

-

Receiver也会做HDCP认证码算法这个步骤得到km'

-

Transmitter与Receiver都会用km\km'去做hdcpBlkCipher,得到一个值R0与R0'

-

100ms后Receiver把R0'发送到Transmitter与R0做比较,相等则认为认证完毕。当然km = km'才能保证R0 = R0'。

-

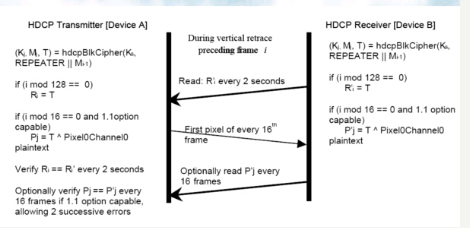

此后的每一帧,Transmitter与Receiver都会运行一次hdcpBlockCipher,不过参数为上次生成的Ks与M,生成的新参数为Ks,M,T

- 在第128帧的时候,另R = T

- 在间隔第一次通信的2s后,再次进行认证

- 后续都采用7,8,9这三个步骤进行迭代认证

此外HDMI自1.1后还支持一个更快速与频繁的认证方式,就是上方设备通信图的下半部分

- 在每第16的倍数帧,用T与当前帧的Channel0的0像素做异或得到Pj

- Channel0的0像素到达Sink后,也与Sink的T`做异或得到P`j

- Sink把P'j发送到Source,与Pj做比较,相同则通过认证

了解HDCP对于处理HDMI的异常现象很有帮助,比如说如果时而出现雪花,有可能是信号不好导致Channel0的0像素出错,从而第二阶段的认证有时会不成功...

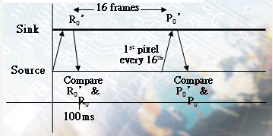

10 HDMI Sink总流程

- 提取与分割10bit的TMDS串行数据

- 10bit的数据,通过不同线路进来的,判断是哪种类型的:DE,Data Island,RGB,Hs,Vs,Ctrl

- TMDS解码

- HDCP解码,同时Hs,Vs,DE做delay

- RGB与DE,Hs,Vs...

- BCH解码得到Packet,错误验证

- Packet含义解析

- 如果是信息,则存到内存

- 如果是Audio Data,生成采样频率

- Audio输出

11 HDMI的时钟与带宽

11.1 像素时钟

我们分别以 RK3568 所支持的 1920x1080p@120Hz 和 4096x2304@60fps 这两个分辨率来算下对应的像素时钟:

1920x1080p@120Hz:1920×1080×120=248832000≈248.832MHz。

4096x2304@60Hz:4096×2304×60=566231040≈566.2MHz。

上面算出来的就是 1S 中要传输的像素数,也就是像素时钟。

11.2 理论带宽

前面我们计算出的是像素时钟,假设像素格式为 RGB888,也就是一个像素 24bit,那么对应的理论带宽就是:

1920x1080p@120Hz:1920 × 1080 × 120 × 24 = 5971968000 ≈ 6.0Gbps

4096x2304@60Hz:4096 × 2304 × 60 x 24 = 13589544960 ≈ 13.6Gbps。

可以看出仅传输视频最少就需要 13.6Gbps 的带宽,而 HDMI 不仅仅要传输视频,还要传输音频等其他信号,所以 HDMI 的实际带宽要大于 13.6Gpbs。

11.3 TMDS时钟

HDMI1.4b协议规定TMDS时钟最高340MHz,HDMI2.0协议将TMDS时钟加到了600MHz。

RK3568 的 HDMI 接口为 2.0 版本,我们就以 600MHz 的 TMDS 时钟计算一下 HDMI 接口实际提供的带宽。一个 TMDS 时钟单个通道传输 10bit 的数据,所以单个通道的带宽就是:

600000000×10 = 6Gpbs

一共有 3 个 TMDS 数据通道,所以总带宽就是:

6Gpbs×3=18Gbps

这个就是大家找 HDMI2.0 资料的时候,说的 18Gbps 带宽的来源。但是前面我们说了,TMDS 在传输的时候会将原始的 8bit 有效数据编码为 10bit,所以真实的有效带宽要再乘一个0.8,因此实际有效带宽为:

18Gpbs×0.8=14.4 Gbps

可以看出,实际有效带宽为 14.4Gbps,大于我们前面算出来的 13.6Gbps 要求。

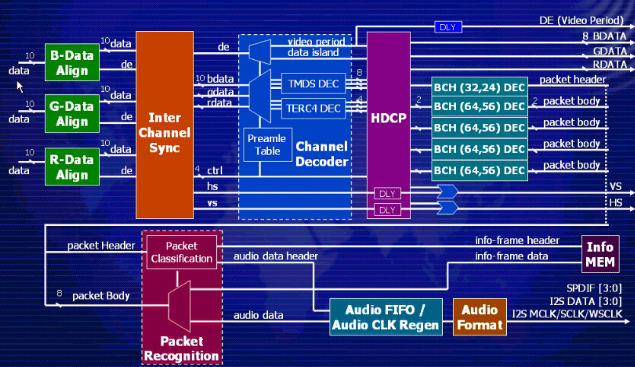

12 EDID

HDMI 屏幕初始化的时候主控会读取屏幕的 EDID 信息,EDID 信息存放在显示器里面,主控通过 DDC 接口,也就是 IIC 接口来读取显示里面的 EDID 信息。EDID 信息包含了显示器特性、特点、分辨率、厂商、序列号、显示器的时序信息等。

现在的显示器发展非常快,显示器种类越来越多,不同尺寸、不同分辨率,甚至有些显示器还支持其他功能,比如 HDR 等。不同的显示器其分辨率和时序都不同,这个时候如果主控输出一个固定的分辨率和时序参数,这样的话会导致无法达到最佳显示效果,更严重的可能会损坏显示器。最好是显示器能主动告诉主控,它所支持的分辨率以及相应的时序参数,主控然后针对不同的显示器设置最佳的驱动参数。而这个就是 EDID 的功能,主动告诉主控显示器的参数信息,主控就可以使用最佳的参数驱动屏幕。

EDID 也发展迭代了很多版本,EDID 1.0~1.3 都是 128 个字节。后面提出了 EDID 1.4 和 E-EDID(增强型 EDID),将长度增加到 256 字节,不管哪个版本的 EDID,其前 128 字节内容是一样的。在 HDMI 显示器热插拔的时候会通过 DDC 通道读取显示器的 EDID 数据,其中前 128个字节必须符合 1.3 版本的 EDID,后 128 个字节必须符合 CEA-861 规定的结构。

EDID 前 128 个字节的含义如表所示:

以下链接是一个可以在线解析EDID的网站。

Web Based EDID Reader