本项目介绍了如何在 Xilinx Spartan-7 FPGA 上 使用 Arm Cortex-M1 软核处理器 构建一个低成本的嵌入式图像处理方案。

项目简介

该项目的目标是利用 Xilinx Spartan 7 SP701 开发板 以及一只 MIPI 摄像头实现图像采集、处理并输出到 HDMI 显示器。系统采用 Arm Cortex-M1 作为控制核,用于配置和控制图像处理链路,而真正的数据流图像处理则由 FPGA 内部通过一系列图像处理模块完成。

使用 FPGA 进行图像处理的好处之一是能够实现图像处理流水线,从而提供高帧率、低延迟和确定性路径。

这种流水线可以很容易地在像 Spartan 7 这样的小型 FPGA 中实现,更令人兴奋的是,Spartan IO 结构可以支持 HMDI、MIPI CSI-2 和 DSI 接口。

当然,要配置和控制图像处理流程,我们需要定制的IP模块或小型处理器。这时,Arm Cortex-M1处理器就能派上用场了。

Arm Cortext-M1 占用空间非常小,可以在 Spartan 7 FPGA 中实现,并且可以控制图像处理链。

图像处理链路构成

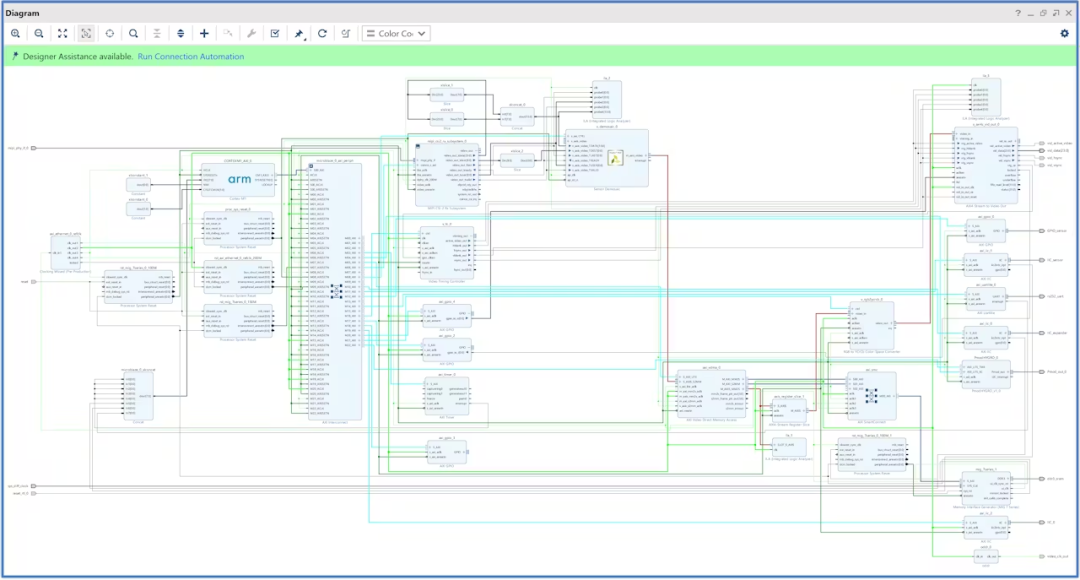

设计中使用了多个 IP 核,每个模块各司其职:

- MIPI CSI-2 RX 子系统

接收来自 MIPI 摄像头的数据,并转换成 AXI Stream 格式。

- DeMosaic 模块

将 RAW 数据转换成 RGB 像素格式。

- VDMA

用于将图像帧缓冲到外部 DDR 内存。

- MIG(内存接口生成器)

实现 FPGA 与 DDR3 外部存储的物理接口。

- VTC视频时序控制器

生成输出 HDMI 所需的同步信号。

- RGB2YCRCB

将 RGB 颜色空间转换为适合 HDMI 输出的 YUV 信号。

- AXI IIC & AXI GPIO & AXI UART

分别用于摄像头配置、模块控制(如使能摄像头)和串口输出调试信息。

- ILA(Integrated Logic Analyzer)

用于现场调试与信号观察。

- Arm Cortex-M1 软核处理器

配置为没有调试功能,但带有 128KB 指令和数据内存。

M1下载地址:

或

通过网盘分享的文件:Cortex-Mx系列资源 链接: https://pan.baidu.com/s/1idn-HyHl9ghd9lcb8s1-vA?pwd=6dv3 提取码: 6dv3

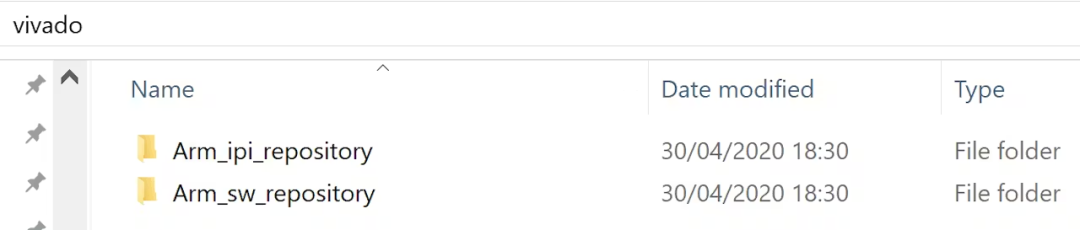

然后可以添加下载的 M1 示例中的 Vivado 目录下提供的处理器。

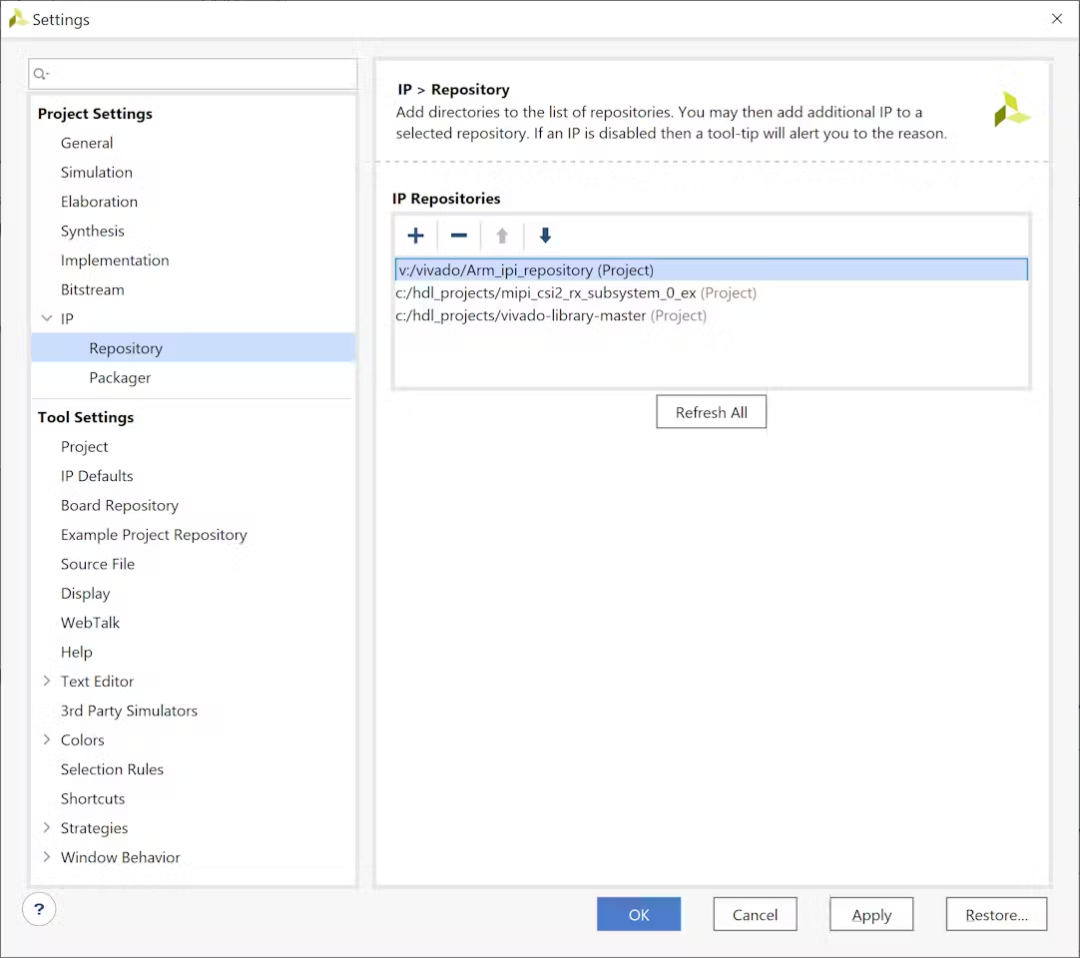

可以使用项目设置将 IPI 存储库添加到项目中,添加完成后,就可以在设计中使用该处理器了。

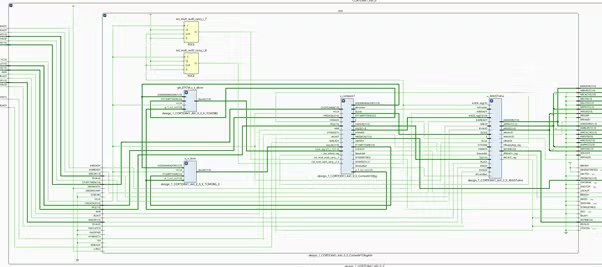

完成后整体框图如下:

以上模块集成在一个 Vivado 工程中,通过约束文件设置引脚与时序条件,然后生成整个系统的 bitstream。

将用于 Arm Cortex-M1 编程的流程是更新比特流。

因此,从 Arm DesignStart FPGA 网站下载的示例项目中,还需要以下文件和批处理程序。

-

make_mmi_file.tcl - 此命令将生成一个 MMI 文件,其中显示指令存储器块 RAM 的位置。

-

执行

make _prog_files.tcl命令------这将把生成的 ELF 文件与比特流合并,生成一个包含我们创建的程序的新比特流。 -

make_prog_files.bat - 用于使用上述 tcl 文件创建更新后的位的批处理文件

-

make_hex_s7.bat - 将 elf 文件转换为必要的格式。

设计方案实施后,我们需要对这些文件进行一些修改。

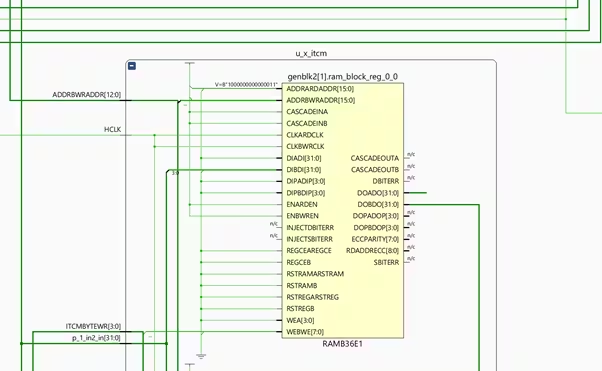

第一个是 make_mmi_file.tcl,在这里我们需要将设备目标部分更新为我们选择的部分,还要确保我们搜索正确的 BRAM 输出,它可以是 DOADO 或 DOBDO。

这可以通过打开详细视图来确定,一旦知道使用了哪个视图,就可以相应地更新 MMI 文件。

设置部件名称

go

# Set MMI output file name

set mmi_file "m1.mmi"

set part "xc7s100fgga676-2" # SET PART HERE更新 BRAM 输出端口

go

# puts $itcm_ram_reordered

# For each entry display the location

foreach ram $new_list {

# Get the RAM location

set loc_val [get_property LOC [get_cells $ram]]

regexp -- {(RAMB36_)([0-9XY]+)} $loc_val full ram_name loc_xy

# Get the nets driven by the D0 pins

set data_bus [get_nets -of_objects [get_pins -filter {REF_PIN_NAME =~ DOBDO*} -of [get_cells $ram]]]

# Check number of bits is the same as that expected

if { [llength $data_bus] != $mem_bits } {

puts "Error - Number of data pins read, [llength $data_bus], does not equal expected memory bits, $mem_bits"

return -1

}

# Number of pins connected to the memory sets the memory depth.

set memory_depth [expr {(32768/[llength $data_bus])-1}]

set idx_list [list]

foreach entry $data_bus {

# Filter the data_bus down to just the two index numbers

set index [regexp -inline -- {[0-9]+} [regexp -inline -- {\[.*} [lindex $entry 0]]]

lappend idx_list $index

}

# Sort the index list from highest to lowest

set idx_list [lsort -decreasing -integer $idx_list]

# Assign the highest and lowest bits for the range variables

set index_low [lindex $idx_list end]

set index_high [lindex $idx_list 0]

# Debug

# puts $data_bus

# puts $idx_list

# puts "$index_high downto $index_low pos $loc_val"

array set mem_array [list $index_high $loc_xy]

}; # foreach

}; # for完成此操作后,我们可以打开已实现的设计并运行 make_mmi_file.tcl 来创建新的 MMI 文件。

在 Vivado TCL 窗口中使用以下命令运行脚本。

go

source make_mmi_file.tcl接下来开发我们的软件。

软件部分设计流程

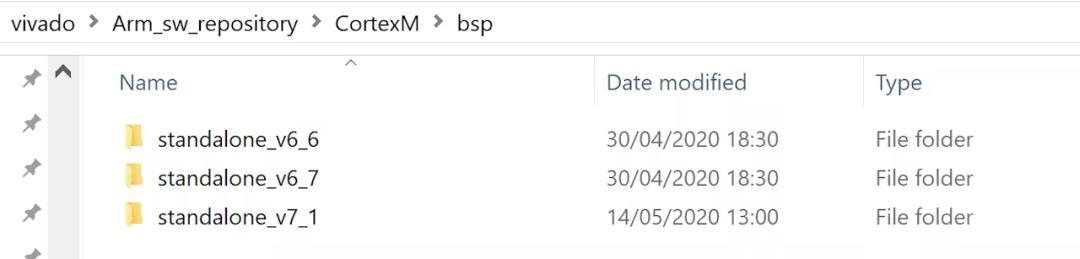

在 Vivado 设计完成后,工程导出 XSA 文件并在 Vitis 中创建基于该平台的 BSP(板级支持包)。由于 Arm DesignStart 的 Cortex-M1 BSP 只支持旧版 Xilinx BSP(6.6/6.7),因此需要复制该版本并重命名为 Vitis 当前版本(如 7.1),并在相关配置文件中更新版本号以兼容。

完成平台构建后,就可以使用该 BSP 为 Arm Cortex-M1 编写控制应用程序。

Keil 开发与应用实现

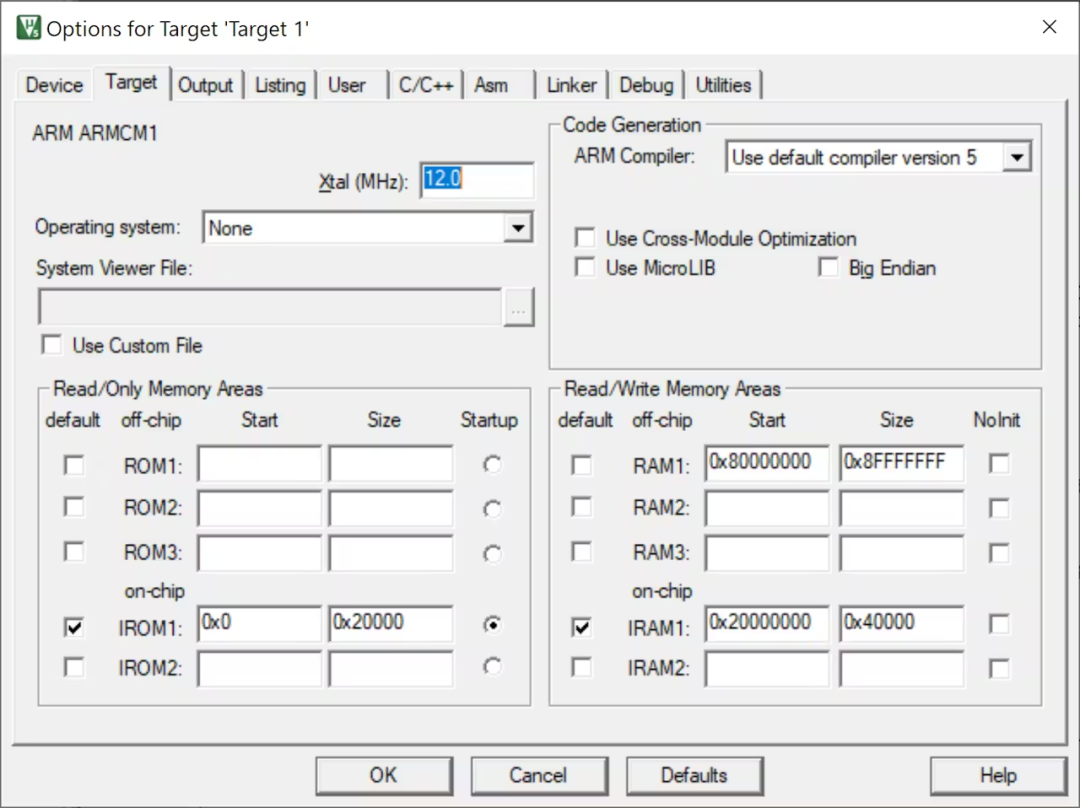

在 Keil MDK 中创建一个针对 Cortex-M1 的项目,对项目进行如下设置:

-

配置内部及外部 DDR 内存基址与大小

-

设置编译后自动执行脚本合并 bitstream

-

添加 Vitis 生成的 BSP include 路径与源文件

应用程序将实现以下动作流程:

-

使能并检测 MIPI 摄像头

-

配置摄像头参数

-

配置 HDMI 输出模块

-

设置视频时序控制器

-

配置 DeMosaic 与 RGB2YCRCB 模块

-

启动 VDMA 进行图像读写

编程目标板与测试

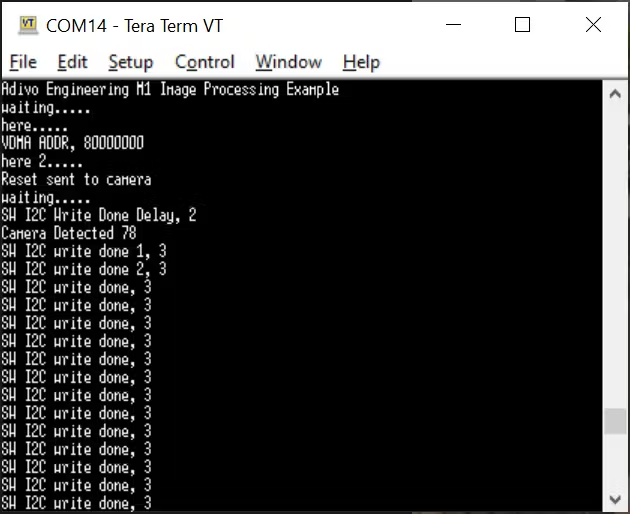

在完成 bitstream 与应用程序合并后,通过 Vivado Hardware Manager 下载到 Spartan-7 FPGA。下载成功并运行后,可以在串口终端看到:

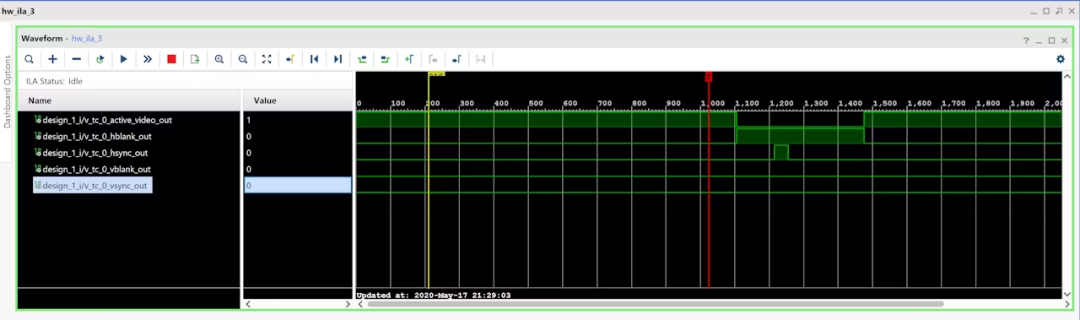

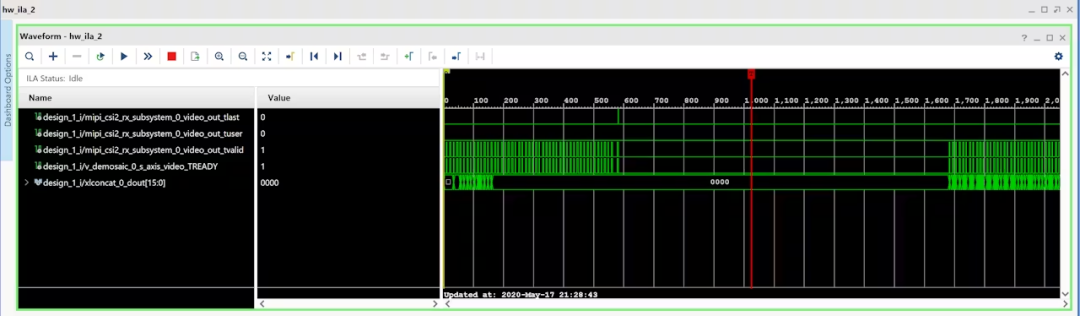

同时利用 FPGA 内部的 ILA 可以观察时序控制器与 CSI-2 接收器的实际信号行为。

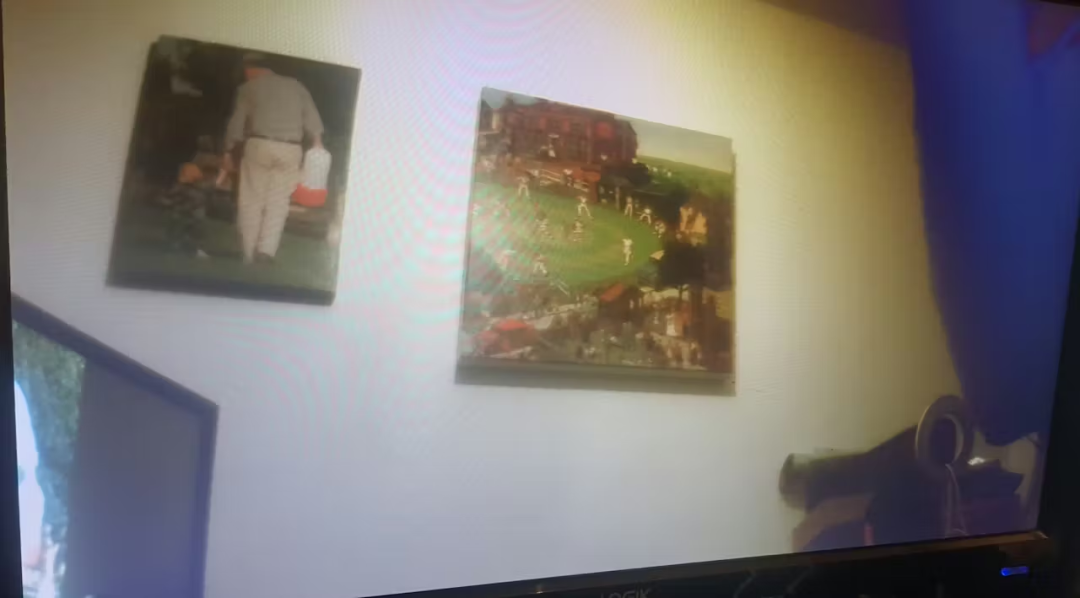

最后在 HDMI 显示器上可以见到摄像头采集的实时图像。

可用链接

https://www.hackster.io/adam-taylor/image-processing-with-arm-cortex-m1-2f2b8c

通过网盘分享的文件:Cortex-Mx系列资源 链接: https://pan.baidu.com/s/1idn-HyHl9ghd9lcb8s1-vA?pwd=6dv3 提取码: 6dv3

总结

这个项目展示了两大核心内容:

-

如何在 Vivado 和 Vitis 中集成 Arm Cortex-M1 内核用作软处理器控制 FPGA 图像处理管线。

-

如何使用 Cortex-M1 控制一条完整的实时图像处理链,包括摄像头、图像转换、帧存储和 HDMI 显示。

项目还表明,使用 Cortex-M1 这样的轻量级核心能够有效地管理高性能图像处理数据流,而不必使用更大的软处理器或复杂架构。在未来,可将 Cortex-M1 替换为 Cortex-M3 或结合 TinyML 推理来扩展功能。