目录

[一、嵌入式系统与 ARM 架构的关联](#一、嵌入式系统与 ARM 架构的关联)

[2.1 硬件系统基本组成](#2.1 硬件系统基本组成)

[2.2 嵌入式领域处理器分类](#2.2 嵌入式领域处理器分类)

[2.3 片上系统(SOC)](#2.3 片上系统(SOC))

[三、指令集架构:CISC 与 RISC 的技术差异](#三、指令集架构:CISC 与 RISC 的技术差异)

[四、ARM 核心硬件架构解析](#四、ARM 核心硬件架构解析)

[4.1 处理器工作模式](#4.1 处理器工作模式)

[4.2 寄存器体系](#4.2 寄存器体系)

[4.2.1 寄存器数量](#4.2.1 寄存器数量)

[4.2.2 寄存器组织与模式关联](#4.2.2 寄存器组织与模式关联)

[4.3 总线系统](#4.3 总线系统)

[4.4 三级流水线机制](#4.4 三级流水线机制)

[4.5 异常处理机制](#4.5 异常处理机制)

[4.5.1 异常触发时的硬件动作](#4.5.1 异常触发时的硬件动作)

[4.5.2 异常返回时的软件动作](#4.5.2 异常返回时的软件动作)

[4.5.3 异常向量表](#4.5.3 异常向量表)

[5.1 内存分类与特性](#5.1 内存分类与特性)

[5.2 虚拟内存与 MMU](#5.2 虚拟内存与 MMU)

[5.3 程序内存布局](#5.3 程序内存布局)

[5.4 栈帧与函数调用](#5.4 栈帧与函数调用)

一、嵌入式系统与 ARM 架构的关联

嵌入式系统的定义为:以应用为中心,以计算机技术为基础,软硬件可剪裁的专用计算机系统,其核心特征是根据需求优化功耗、体积、稳定性与可靠性。ARM 架构凭借低功耗、高可扩展性与高性能的技术优势,成为嵌入式领域的主流选择。以正点原子 iMX6ULL 开发板为例,其核心为 NXP 公司的 Cortex-A7 内核,属于典型的 ARM 架构片上系统(SOC)。

嵌入式系统采用三层分层架构:

- 应用层(APP):实现业务逻辑的上层代码

- 操作系统层(OS):完成资源调度与任务管理,如 Linux、FreeRTOS

- 硬件层:以 SOC 为核心的物理硬件平台,是系统功能的基础载体

二、计算机系统底层硬件逻辑

2.1 硬件系统基本组成

计算机硬件由运算器、控制器、存储器、输入设备、输出设备五大核心模块构成:

- 运算器与控制器集成形成中央处理器(CPU),负责指令执行与系统控制

- 存储器分为内存(RAM,易失性存储)与外存(Flash、硬盘等,非易失性存储)

- 输入输出设备通过外设接口与核心硬件交互,实现数据的输入与输出

2.2 嵌入式领域处理器分类

| 处理器类型 | 全称 | 核心定位 | 典型应用场景 |

|---|---|---|---|

| CPU | Central Processing Unit | 通用计算核心 | 全场景系统计算 |

| GPU | Graphics Processing Unit | 并行图形计算 | 图像渲染、AI 加速 |

| FPU | Float Processing Unit | 浮点运算加速 | 高精度数值计算 |

| MPU | Micro Processing Unit | 通用微处理器 | 复杂计算类嵌入式设备 |

| MCU | Micro Control Unit | 微控制器 | 低功耗控制类设备(如 STM32) |

| DSP | Digital Signal Processor | 数字信号处理 | 音频 / 图像实时处理 |

2.3 片上系统(SOC)

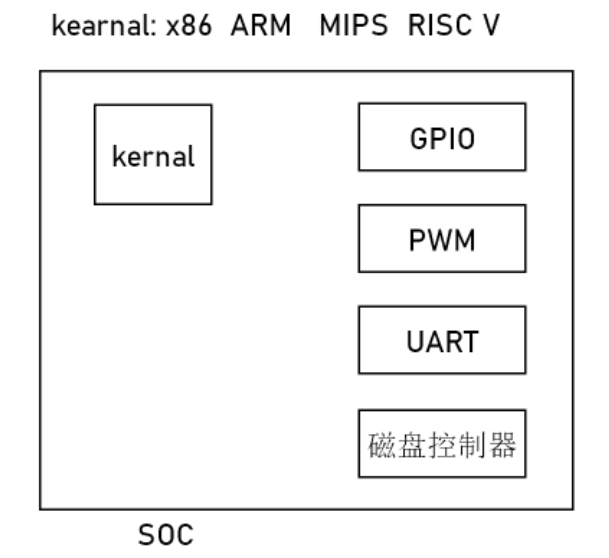

SOC(System On Chip)通过将处理器内核、外设控制器、存储接口等功能模块集成在单一芯片上,实现了嵌入式系统的高集成度与低功耗特性。以 iMX6ULL 为例,其内部集成 Cortex-A7 内核、GPIO/UART/PWM 外设控制器及内存管理单元,单芯片即可支撑完整的嵌入式系统功能。

SOC 像一个蓝图,将市政府(MPU)警察局(MCU)、研究所(DSP)机场(调制解调器)放在同一片土地上(芯片),形成一个功能完善的城市。

片上系统

片上系统

三、指令集架构:CISC 与 RISC 的技术差异

指令集是 CPU 的底层执行语言,决定了硬件设计复杂度与执行效率:

- CISC(复杂指令集):以 X86 架构为代表,指令集包含复杂操作,硬件设计复杂度高,功耗较高,适用于桌面计算场景

- RISC(精简指令集):以 ARM 架构为代表,指令集精简且单周期执行,硬件设计简单,功耗较低,是嵌入式场景的最优选择

ARM 架构经历多代迭代,从早期 ARM1-ARM11 系列发展至当前 Cortex 系列,指令集已更新至 V9 版本。Cortex 系列分为三大分支:

- Cortex-A:应用级处理器,如 Cortex-A7(32 位,4 字长),适用于开发板、智能终端等复杂计算场景

- Cortex-R:实时处理器,适用于工业控制、汽车电子等低延迟场景

- Cortex-M:微控制器内核,适用于低功耗、简单控制场景

四、ARM 核心硬件架构解析

4.1 处理器工作模式

ARM 处理器通过多工作模式实现特权分级与异常处理,包含 7 个基本工作模式与 Cortex-A 架构特有的扩展模式:

- User(用户模式):非特权模式,大部分应用任务在该模式下执行,无法直接访问系统资源,需通过异常进入特权模式。

- FIQ(快速中断模式):高优先级中断触发时进入,用于处理低延迟的实时事件(如高速数据采集),该模式拥有独立的 r8-r12 寄存器以减少上下文切换开销。

- IRQ(普通中断模式):低优先级中断触发时进入,用于处理通用中断事件(如外设中断)。

- Supervisor(管理模式):系统复位或执行软中断指令(SWI)时进入,是操作系统内核的默认运行模式,拥有最高特权。

- Abort(终止模式):内存存取异常(如地址错误、权限不足)时进入,用于处理内存访问错误。

- Undef(未定义模式):执行未定义指令时进入,用于处理指令集扩展或仿真。

- System(系统模式):特权模式,使用与 User 模式完全相同的寄存器集,供操作系统特权任务使用,避免频繁切换模式。

- Monitor(监控模式,Cortex-A 特有):为安全扩展设计的特权模式,用于执行安全监控代码,实现安全世界与非安全世界的隔离,是 TrustZone 技术的核心载体。

- Hyp(调试 模式,Cortex-A 特有):为虚拟化扩展设计的特权模式,用于运行虚拟机监控器(VMM),实现多操作系统的隔离与调度,特权级别高于 Monitor 模式,是 ARM 虚拟化技术的核心载体。

不同工作模式的切换由硬件自动触发(如中断、异常)或软件指令触发(如软中断),模式切换时硬件会自动保存 / 恢复部分上下文,以保障系统稳定性。

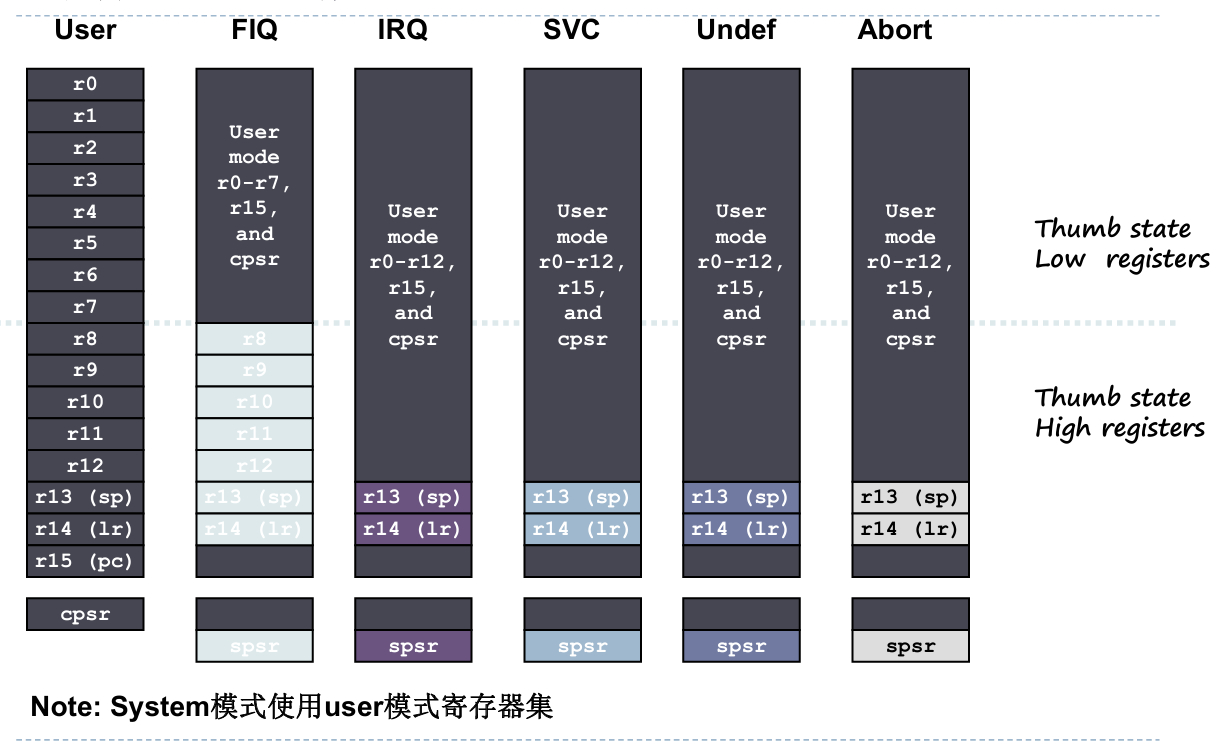

寄存器组织概要

寄存器组织概要

4.2 寄存器体系

ARM 寄存器的可访问性由当前处理器工作模式决定,核心特征如下:

4.2.1 寄存器数量

- **传统 ARM 架构:**包含 37 个 32 位寄存器,其中 30 个为通用寄存器,1 个为程序计数器(PC,R15),1 个为当前程序状态寄存器(CPSR),5 个为备份程序状态寄存器(SPSR,仅特权模式可访问)。

- **Cortex-A 架构:**扩展为 40 个 32 位寄存器,新增 Monitor 模式专用的r13_mon(栈指针)、r14_mon(链接寄存器)、spsr_mon(备份状态寄存器),以支持安全扩展功能。

4.2.2 寄存器组织与模式关联

不同工作模式共享部分寄存器,同时拥有专用寄存器以实现上下文隔离:

- 通用寄存器(R0-R12):User、System 模式共享完整的 R0-R12;FIQ 模式拥有独立的 R8-R12,减少中断响应时的上下文切换;IRQ、Supervisor、Abort、Undef 模式仅共享 R0-R12,专用 R13、R14。

- 栈指针(R13,SP):每个特权模式(除 System)拥有独立的 R13,用于保存当前模式的栈顶地址,避免不同模式的栈冲突。

- 链接寄存器(R14,LR):每个特权模式(除 System)拥有独立的 R14,用于保存函数返回地址或异常返回地址。

- 程序计数器(R15,PC):所有模式共享,指向下一条要执行的指令地址。

- 状态寄存器(CPSR/SPSR):CPSR 为所有模式共享,记录当前 CPU 状态(中断标志、工作模式、条件码等);SPSR 仅特权模式(除 System)可访问,用于保存异常发生前的CPSR 状态,异常返回时恢复上下文。

这种寄存器组织设计既保障了模式切换的效率,又实现了不同特权级别的资源隔离。

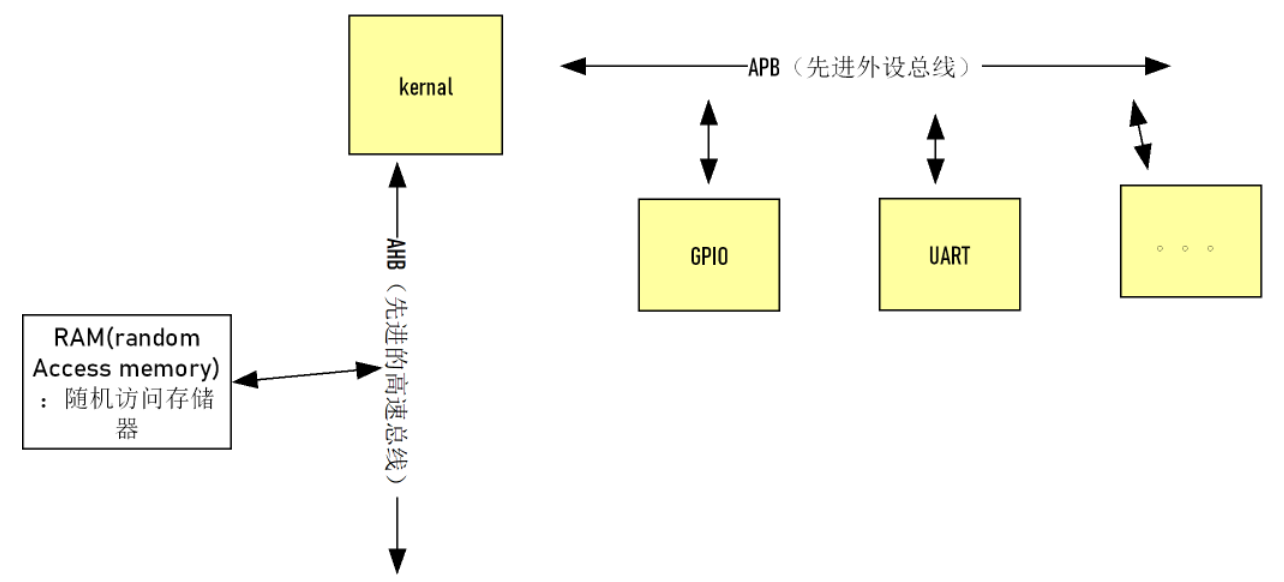

4.3 总线系统

CPU 与外设、内存通过三类总线完成数据交互:

- 地址总线:传输数据存储地址,32 位地址总线支持最大 4GB 寻址空间

- 数据总线:传输实际数据,宽度决定单次传输的比特数

- 控制总线:传递读写控制、中断请求等信号

ARM 架构中,外设通过 APB(先进外设总线) 连接,用于 GPIO、UART 等低速外设的数据传输;内存则通过 **AHB(先进高性能总线)**连接,保障高速数据交互。

多总线结构

多总线结构

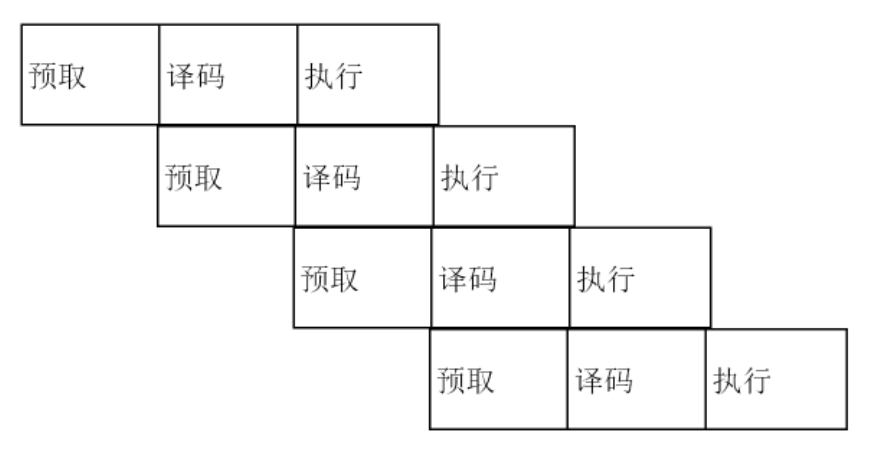

4.4 三级流水线机制

ARM 采用预取 - 译码 - 执行三级流水线架构,通过指令的并行处理提升执行效率:当一条指令处于执行阶段时,下一条指令完成译码,第三条指令进入预取阶段,实现单周期指令的高效执行。高级 ARM 内核进一步扩展为五级、八级流水线,以优化指令吞吐量。

三级流水线

三级流水线

4.5 异常处理机制

异常是 ARM 处理器处理外部事件或内部错误的核心机制,其执行流程与向量表设计如下:

4.5.1 异常触发时的硬件动作

当异常产生时,ARM 核心自动执行以下步骤:

- 保存状态:将当前 CPSR 的内容拷贝到对应异常模式的 SPSR_<mode> 中,用于异常返回时恢复上下文。

- 设置 CPSR :

- 切换处理器状态为 ARM 态(若当前为 Thumb 态),确保异常处理代码在 ARM 态执行。

- 切换处理器模式至对应异常模式(如 FIQ 异常进入 FIQ 模式,复位进入 Supervisor 模式)。

- 设置中断禁止位:例如 FIQ 异常会禁止 FIQ 中断,IRQ 异常会禁止 IRQ 中断,避免嵌套异常干扰处理流程。

- 保存返回地址:将异常发生时的下一条指令地址保存到对应异常模式的 LR_<mode> 中,供返回时恢复 PC 使用。

- 跳转至异常向量 :将

PC设置为异常向量表中对应异常的偏移地址,执行异常处理入口代码。

4.5.2 异常返回时的软件动作

异常处理完成后,需通过软件指令恢复上下文:

- 恢复 CPSR:从对应异常模式的 SPSR_<mode> 中读取数据,恢复到 CPSR,以恢复异常发生前的处理器状态与模式。

- 恢复 PC:从对应异常模式的 LR_<mode> 中读取返回地址,恢复到 PC,使处理器回到异常发生前的执行流程。

**注:**异常处理的所有硬件动作与软件恢复操作仅能在 ARM 态执行。

4.5.3 异常向量表

异常向量表是一段固定地址的内存区域,存储各异常的处理入口地址,不同异常对应固定的偏移量:

| 异常类型 | 偏移量 | 触发场景 |

|---|---|---|

| Reset(复位) | 0x00 | 系统上电或复位时触发 |

| Undefined Instruction(未定义指令) | 0x04 | 执行未定义指令时触发 |

| Software Interrupt(软中断) | 0x08 | 执行 SWI 指令时触发(如系统调用) |

| Prefetch Abort(预取中止) | 0x0C | 指令预取时内存访问异常触发 |

| Data Abort(数据中止) | 0x10 | 数据访问时内存异常触发 |

| Reserved(保留) | 0x14 | 预留未使用 |

| IRQ(普通中断) | 0x18 | 低优先级外设中断触发 |

| FIQ(快速中断) | 0x1C | 高优先级外设中断触发 |

在 ARM720T、ARM9/10 系列处理器中,异常向量表的固定基地址为 0xFFFF0000,各异常入口为基地址加上对应偏移量。

五、内存管理与程序执行机制

5.1 内存分类与特性

- RAM(随机访问存储器):易失性存储,读写速度快,支持直接寻址,如 DDR 内存

- ROM(只读存储器):非易失性存储,读写速度较慢,通常不可直接寻址,如 Nor Flash

5.2 虚拟内存与 MMU

内存管理单元(MMU)实现虚拟地址到物理地址的映射,为每个进程分配独立的虚拟地址空间,避免地址冲突。例如虚拟地址 0x1000 可映射至物理地址 0x1200,提升系统安全性与内存利用率。

5.3 程序内存布局

程序运行时,内存划分为多个功能区域:

- **代码段(Text):**存储编译后的机器指令,如 main、fun1 等函数

- **数据段(Data):**存储已初始化的全局变量

- **BSS 段:**存储未初始化的全局变量(自动初始化为 0)

- **栈(Stack):**存储函数局部变量与调用栈帧,由高地址向低地址增长

- **堆(Heap):**用于动态内存分配(如 malloc),由低地址向高地址增长

5.4 栈帧与函数调用

函数调用时,CPU 在栈上创建栈帧,保存局部变量、返回地址等上下文信息。以 main 调用 fun1 为例:

- main 函数的栈帧被压入栈底

- 调用 fun1 时,LR 寄存器保存返回地址(如0x1204)

- fun1 的栈帧压入栈顶,执行完成后通过 LR 寄存器返回 main

栈帧分析是调试程序崩溃、定位内存问题的核心技术手段。