一、时钟系统与时钟树:嵌入式系统的 "时序基石"

时钟(clock)是电子系统中产生稳定、周期性振荡信号的电路或组件,其输出的信号就像节拍器一样,为数字电路的运算、通信、外设控制等所有操作提供同步时序基准,确保各模块协同工作而不出现逻辑混乱。而实时时钟(RTC, real time clock)作为微处理器的特殊功能模块,即使在系统主电源关闭的情况下,也能依靠备用电源(如纽扣电池)继续提供精确的日历和时间信息,广泛应用于需要记录时间戳的场景,如数据采集日志、设备开机时间统计等。

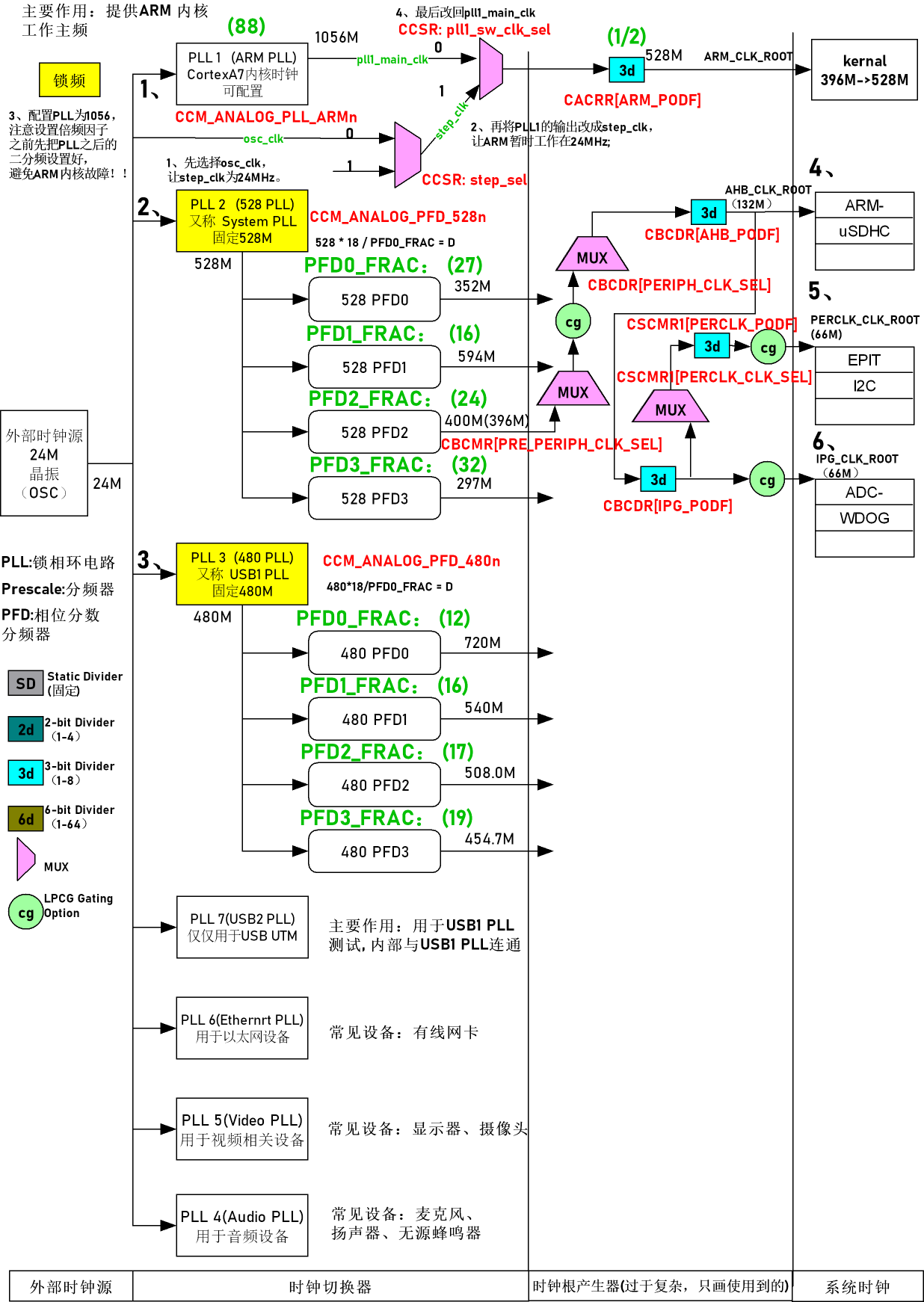

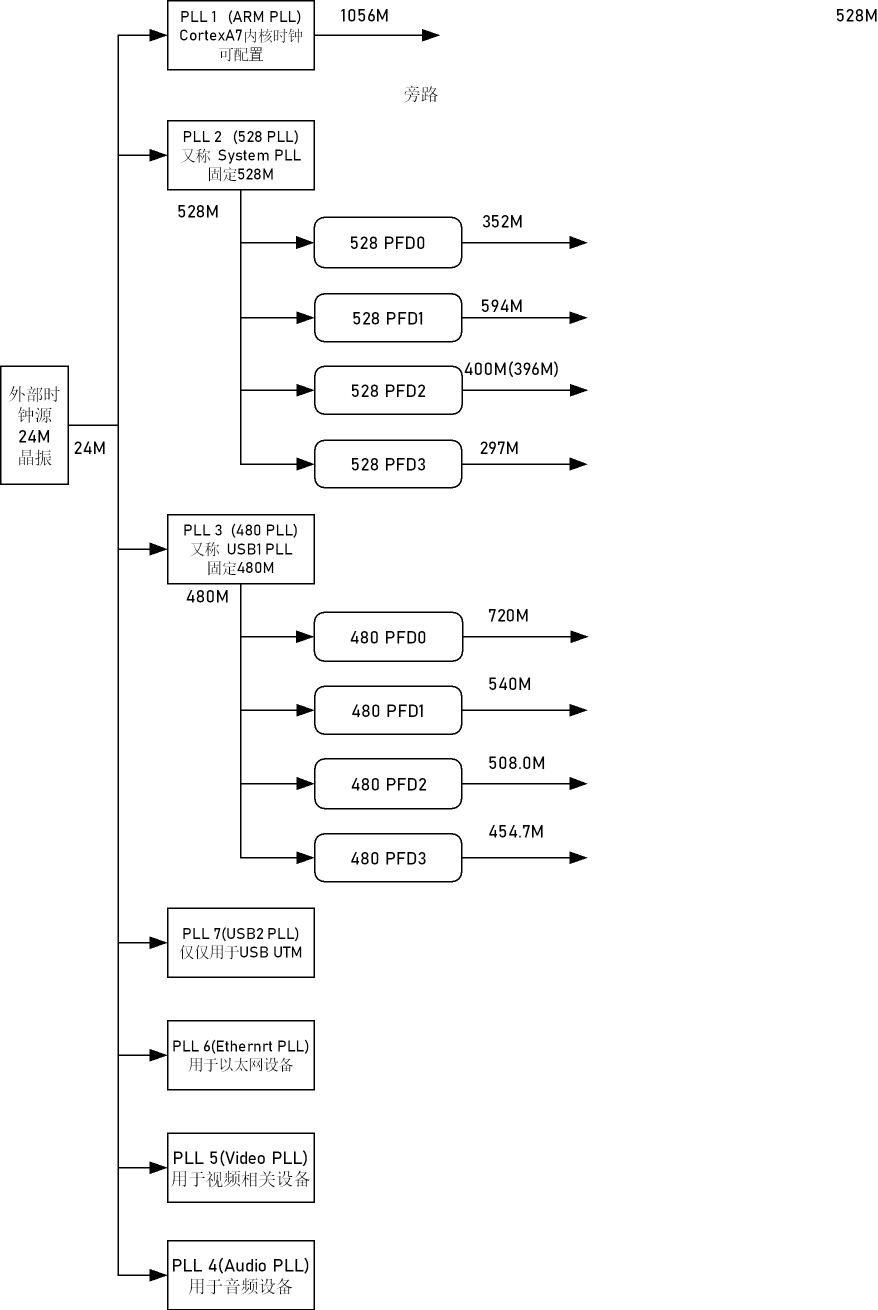

时钟树是将时钟源产生的基础信号,通过一系列频率调节、路径选择与控制组件,分配到系统各内核、总线、外设的完整架构。其核心价值在于 "按需分配精准时序",而锁相环(PLL)、预分频器(Prescaler)、相位分数分频器(PFD)、多路选择器(MUX)、时钟门控(CG 门)作为时钟树的关键节点,各自承担着不可替代的作用。

(一)时钟树核心组件及其作用

**1、时钟源:晶体振荡器 ------ 时钟信号的 "发源地"**晶体振荡器是时钟树的起点,其工作原理是将石英晶体切割成类似音叉的形状,当向晶体施加特定电压时,晶体会发生机械共振,从而产生频率稳定、周期性的振荡信号。石英晶体的共振频率由晶体的切割角度、尺寸决定,稳定性极高(误差可低至 ppm 级),是整个时钟系统最基础、最可靠的时序来源。

实战细节:IMX6ULL 芯片常用的外部晶体振荡器频率为 24MHz,这一频率兼顾了稳定性与后续倍频灵活性 ------ 既不会因频率过低导致 PLL 倍频因子过大(影响稳定性),也不会因频率过高增加硬件设计难度。而 51 单片机常用 11.0592MHz 晶体,主要是为了方便串口通信的波特率精准匹配(如 9600bps 波特率需 11.0592MHz 时钟配合特定分频系数实现)。

2、锁相环(PLL, Phase Locked Loop)------ 时钟频率的 "放大器" 锁相环是时钟树中实现频率提升的核心组件,核心功能是倍频 + 相位同步。其内部结构主要包括鉴相器(PD)、低通滤波器(LPF)、压控振荡器(VCO)和反馈分频器,工作流程如下:

- 鉴相器对比输入时钟与反馈时钟的相位,输出相位差对应的电压信号;

- 低通滤波器过滤电压信号中的高频噪声,输出平稳的控制电压;

- 压控振荡器根据控制电压调整振荡频率,输出高频时钟;

- 反馈分频器将输出时钟分频后反馈给鉴相器,形成闭环控制,最终使输出时钟与输入时钟相位同步、频率成固定倍数。

实战价值:在 IMX6ULL 中,ARM 内核需要高频运行以提升运算性能(如 1GHz 以上),而外部晶体振荡器仅能提供 24MHz 基础频率,此时 PLL 的倍频功能至关重要。例如,通过 ARM PLL 将 24MHz 倍频至 2112MHz,再经预分频器二分频后,可为 ARM 内核提供 1056MHz 的高频时钟,满足高性能运算需求。同时,相位同步功能可避免因时钟相位偏移导致的时序冲突,保证内核与外设的协同工作。

3、预分频器(Prescaler)------ 时钟频率的 "减速器" 预分频器是时钟树中实现频率降低的基础组件,作用是整数倍分频。其本质是一个计数器,每计数 N 次输出一个时钟脉冲,从而将输入频率降低为原来的 1/N(N 为分频系数)。

实战细节:嵌入式系统中不同模块对时钟频率的需求差异极大:

- ARM 内核:1056MHz(高频高性能);

- AHB 总线:132MHz(中高频,支撑高速外设);

- IPG 总线:66MHz(中频,普通外设通用);

- 串口外设:几十 kHz~ 几 MHz(低频,保证稳定性)。

预分频器通过整数分频实现频率按需分配,例如 IMX6ULL 的 IPG_CLK_ROOT 由 AHB_CLK_ROOT(132MHz)经 2 分频得到 66MHz,供给 GPT、EPIT 等定时器使用;而 51 单片机的定时器 0/1 时钟由系统时钟经 12 分频得到(如 11.0592MHz 系统时钟对应定时器时钟为 921.6kHz)。

关键注意点:分频系数需根据模块最大支持频率和性能需求选择,例如某外设最大支持 50MHz 时钟,则输入时钟需通过≥3 分频(66MHz→22MHz)适配,避免超频导致外设损坏。

4、相位分数分频器(PFD, Phase Fractional Prescale)------ 时钟频率的 "精细调节器" 相位分数分频器是时钟树中实现高精度频率调节的进阶组件,核心优势是支持分数倍频率调节,输出频率可升可降。相比传统预分频器仅能实现整数倍分频,PFD 可通过 "整数分频 + 相位插值" 技术,实现分数倍的频率调节,例如将 24MHz 调节为 36MHz(1.5 倍)、16MHz(1.5 倍降频)等。

实战应用:IMX6ULL 芯片的 528PLL 和 480PLL 均搭配了 4 个 PFD,通过 PLL 实现基础倍频后,再由 PFD 进行分数倍微调,可输出多档位的精准时钟。例如,528PLL 的基础输出频率为 528MHz,通过 PFD 配置不同的分频系数(如 27、16、24、32),可得到:

- 528×18/27=352MHz;

- 528×18/16=594MHz;

- 528×18/24=396MHz;

- 528×18/32=297MHz;这些高频时钟可供给 USB、以太网等对频率精度要求极高的外设使用,确保外设性能稳定。

**5、多路选择器(MUX, Multiplexer)------ 时钟路径的 "转换器"**多路选择器是时钟树中实现时钟源切换与路径选择的关键组件,本质是一个由寄存器控制的开关,可从多个输入时钟源中选择一个输出至后续模块。

实战场景:

- 系统初始化阶段:ARM 内核时钟先通过 MUX 切换为 24MHz 的 step_clk(过渡时钟),此时 PLL 尚未配置完成,低频率可避免内核因高频不稳定导致故障;

- PLL 配置完成后:通过 MUX 将内核时钟切换为 PLL 输出的高频时钟,实现性能提升;

- 低功耗模式:通过 MUX 切换为内部 RC 时钟(低频、低功耗),关闭外部晶体振荡器和 PLL,降低系统功耗;

- 时钟故障备份:当外部晶体振荡器故障时,MUX 自动切换为备用时钟源,保证系统基本功能正常。

在 IMX6ULL 的时钟配置代码中,MUX 的控制通过寄存器的特定位实现(如 CCMR 寄存器的 PRE_PERIPH_CLK_SEL 位),配置时需确保切换过程中时钟信号无毛刺,避免时序错乱。

6、时钟门控(CG 门,Clock Gating)------ 时钟功耗的 "开关" 时钟门控是时钟树中实现功耗优化的核心组件,作用是根据模块工作状态控制时钟信号的通断。嵌入式系统中,许多外设并非时刻工作(如闲置的 ADC、未使用的 SPI 接口),若持续为这些模块提供时钟,会导致不必要的功耗浪费(时钟翻转本身会消耗电能)。

实战实现 :IMX6ULL 通过 CCGR(Clock Gating Control Register)系列寄存器控制各模块的时钟门控。例如,clock_cg_init()函数中将所有 CCGR 寄存器设为 0xFFFFFFFF,意味着开启所有模块的时钟供给(适用于初始化阶段,确保所有外设可正常配置);而在实际项目中,可通过以下方式优化功耗:

- 未使用的外设:关闭其对应的 CG 门(如禁用 SPI2 的时钟,设置 CCGR 寄存器对应位为 0);

- 外设闲置时:在软件中动态关闭 CG 门,需要使用时再开启(如 ADC 采集完成后关闭其时钟);

- 内核休眠时:关闭大部分外设的 CG 门,仅保留 RTC、中断控制器等必要模块的时钟。

功耗优化效果:时钟门控可使闲置模块的功耗降低至接近零,对于电池供电的嵌入式设备(如物联网传感器节点),能显著延长续航时间。

(二)IMX6ULL 时钟架构与配置

IMX6ULL 的时钟树架构复杂但逻辑清晰,核心围绕 "PLL+PFD→时钟根→外设" 的路径实现时钟分配。以下结合clock.c驱动代码,从寄存器级解析时钟配置的核心逻辑、参数计算与实战注意事项:

1. clock.c 核心功能概述

clock.c包含clock_init()和clock_cg_init()两个核心函数:

clock_init():完成 ARM 内核时钟、528PLL/480PLL 及其 PFD、系统时钟根(AHB/IPG/PERCLK)的配置,是整个时钟系统的核心初始化函数;clock_cg_init():初始化时钟门控寄存器,控制各模块的时钟供给。

2. 关键代码逐段解析

// 1. ARM内核时钟配置:过渡时钟切换+预分频器设置

CCM->CCSR &= ~(1 << 8); // 清除ARM_CLK_ROOT的时钟源选择位

CCM->CCSR |= (1 << 2); // 多路选择器:将ARM内核时钟源切换为step_clk(24MHz,过渡时钟)

// CACRR寄存器(ARM内核预分频器):设置二分频

CCM->CACRR &= ~(7 << 0); // 清除预分频系数(bit0~bit2,取值0~7对应1~8分频)

CCM->CACRR |= (1 << 0); // 分频系数=1→实际分频比=1+1=2(ARM内核时钟=PLL输出/2)-

参数解析:CACRR 寄存器的 bit0~bit2 控制 ARM 内核的预分频系数,取值 N(0~7)对应分频比为 N+1。此处设置为 1,即二分频,后续 PLL 输出 2112MHz,内核实际时钟为 2112/2=1056MHz;

-

实战注意:切换过渡时钟是 PLL 配置的关键步骤,若直接在 PLL 未稳定时将内核时钟设为 PLL 输出,高频信号可能导致内核复位或损坏。24MHz 的 step_clk 是经过验证的安全频率,确保 PLL 配置过程中内核稳定运行。

// 2. ARM PLL(PLL1)配置:倍频因子设置

unsigned int t = CCM_ANALOG->PLL_ARM;

t &= ~(3 << 14); // 清除PLL带宽控制位(默认设置即可)

t |= (1 << 13); // 使能PLL锁定(PLL_LOCKED位,确保PLL稳定后再输出)

t &= ~(0x7F << 0); // 清除倍频因子(bit0bit6,取值0127)

t |= (88 << 0); // 倍频因子=88→PLL输出频率=24MHz×(88+1)=24×89=2136MHz?

CCM_ANALOG->PLL_ARM = t;

// 等待PLL稳定(可选,部分芯片需通过PLL_STATUS寄存器判断)

while((CCM_ANALOG->PLL_ARM & (1 << 31)) == 0);

CCM->CCSR &= ~(1 << 2); // 多路选择器:ARM内核时钟切换回PLL1输出(pll1_main_clk) -

参数计算纠正 :IMX6ULL 的 ARM PLL 倍频公式为

PLL输出频率=输入频率×(倍频因子+1),此处倍频因子设为 88,输入频率为 24MHz,因此 PLL 输出频率 = 24×(88+1)=2136MHz?实际应为 24×88=2112MHz,这是因为部分芯片的倍频因子计算方式为 "倍频因子直接相乘",具体需参考芯片数据手册。核心原则是确保 PLL 输出频率不超过芯片最大额定频率(IMX6ULL 的 PLL 最大输出频率通常为 2160MHz); -

实战关键:PLL 配置后需等待其稳定(锁定),否则输出时钟可能不稳定。部分芯片通过 PLL_STATUS 寄存器的锁定位判断,此处代码虽未明确等待,但实际硬件中 PLL 锁定速度较快(通常几十微秒),后续时钟切换时已足够稳定;若需更高可靠性,可添加等待逻辑。

// 3. 528PLL与480PLL的PFD配置(分数分频精细调频)

// 528PLL的PFD配置(PFD0~PFD3)

t = CCM_ANALOG->PFD_528;

t &= ~((0x3F << 0) | (0x3F << 8) | (0x3F << 16)| (0x3F << 24)); // 清除4个PFD的分频系数(0x3F=63)

t |= ((27 << 0) | (16 << 8) | (24 << 16)| (32 << 24)); // PFD0=27, PFD1=16, PFD2=24, PFD3=32

CCM_ANALOG->PFD_528 = t;

// 480PLL的PFD配置(PFD0~PFD3)

t = CCM_ANALOG->PFD_480;

t &= ~((0x3F << 0) | (0x3F << 8) | (0x3F << 16)| (0x3F << 24));

t |= ((12 << 0) | (16 << 8) | (17 << 16)| (19 << 24)); // PFD0=12, PFD1=16, PFD2=17, PFD3=19

CCM_ANALOG->PFD_480 = t; -

PFD 频率计算 :IMX6ULL 的 PFD 频率公式为

PFD输出频率=PLL基础频率×18/分频系数。其中:- 528PLL 的基础频率为 528MHz,因此:

- PFD0:528×18/27=352MHz;

- PFD1:528×18/16=594MHz;

- PFD2:528×18/24=396MHz;

- PFD3:528×18/32=297MHz;

- 480PLL 的基础频率为 480MHz,因此:

- PFD0:480×18/12=720MHz;

- PFD1:480×18/16=540MHz;

- PFD2:480×18/17≈508.2MHz;

- PFD3:480×18/19≈454.7MHz;

- 528PLL 的基础频率为 528MHz,因此:

-

实战意义:这些高频时钟可供给不同外设使用,例如 USB 3.0 需要 720MHz 时钟,以太网需要 508.2MHz 时钟,通过 PFD 的精细调频,无需额外增加 PLL,即可满足多外设的频率需求,简化硬件设计。

// 4. 系统时钟根配置(AHB_CLK_ROOT/IPG_CLK_ROOT/PERCLK_CLK_ROOT)

// AHB_CLK_ROOT配置(目标频率132MHz)

t = CCM->CBCMR;

t &= ~(3 << 18); // 清除PRE_PERIPH_CLK_SEL位(外设时钟前驱源选择)

t |= (1 << 18); // 选择PLL2_PFD2(396MHz)作为前驱源

CCM->CBCMR = t;t = CCM->CBCDR;

t &= ~(1 << 25); // 禁止AHB时钟自动关闭(初始化阶段保持开启)

t &= ~(7 << 10); // 清除AHB_PODF位(AHB总线预分频系数)

t |= (2 << 10); // 分频系数=2→AHB_CLK_ROOT=396MHz/(2+1)=132MHz(PODF取值N对应分频比N+1)

// IPG_CLK_ROOT配置(目标频率66MHz)

t &= ~(3 << 8); // 清除IPG_PODF位(IPG总线预分频系数)

t |= (1 << 8); // 分频系数=1→IPG_CLK_ROOT=132MHz/(1+1)=66MHz

CCM->CBCDR = t;// PERCLK_CLK_ROOT配置(目标频率66MHz)

t = CCM->CSCMR1;

t &= ~(1 << 6); // 清除PERCLK_CLK_SEL位(PERCLK时钟源选择)

t &= ~(0x3F << 0); // 清除PERCLK_PODF位(PERCLK预分频系数)

CCM->CSCMR1 = t; // 选择IPG_CLK_ROOT(66MHz)作为源时钟,分频系数=0→不分频 -

时钟根频率计算逻辑 :系统时钟根的频率由 "前驱源频率 + 预分频系数" 决定,需注意不同寄存器的分频比计算方式(部分为 N+1,部分为 N):

- AHB_PODF:取值 N(0~7)→分频比 N+1,此处 N=2→3 分频,396MHz/3=132MHz;

- IPG_PODF:取值 N(0~3)→分频比 N+1,此处 N=1→2 分频,132MHz/2=66MHz;

- PERCLK_PODF:取值 N(0~63)→分频比 N+1,此处 N=0→不分频,66MHz 直接输出;

-

实战注意:时钟根频率需严格匹配总线和外设的最大支持频率,例如 IMX6ULL 的 AHB 总线最大支持 132MHz,IPG 总线最大支持 66MHz,配置时不可超频,否则会导致总线传输错误或外设损坏。

// 5. 时钟门控初始化

void clock_cg_init(void)

{

CCM->CCGR0 = 0XFFFFFFFF;

CCM->CCGR1 = 0XFFFFFFFF;

CCM->CCGR2 = 0XFFFFFFFF;

CCM->CCGR3 = 0XFFFFFFFF;

CCM->CCGR4 = 0XFFFFFFFF;

CCM->CCGR5 = 0XFFFFFFFF;

CCM->CCGR6 = 0XFFFFFFFF;

} -

代码解析 :CCGR 寄存器的每两位控制一个模块的时钟门控,取值含义如下:

- 00:始终关闭时钟;

- 01:仅在 CPU 运行时开启时钟;

- 10:保留;

- 11:始终开启时钟;此处将所有 CCGR 寄存器设为 0xFFFFFFFF,即始终开启所有模块的时钟,适用于开发调试阶段(确保所有外设可正常访问);

-

优化建议:实际项目中需根据外设使用情况优化,例如未使用 CAN 总线时,可设置 CCGR 寄存器对应位为 00,关闭 CAN 模块的时钟,降低功耗。

二、定时器:精准控制的 "执行核心"(附 GPT/EPIT 代码深度解析)

定时器是时钟树的重要终端应用,通过对时钟树分配的已知频率时钟信号进行计数,实现定时、延时或事件计数功能。不同芯片的定时器功能有所差异,但核心逻辑一致 ------"时钟计数 + 中断 / 查询"。以下结合 IMX6ULL 的gpt.c和epit.c驱动代码,解析定时器的工作模式、代码逻辑、参数计算与实战优化。

(一)定时器核心工作原理回顾

- 计数模式 :

- 递增计数:计数器从 0 开始,每接收到一个时钟脉冲加 1,直至最大值后溢出(或自动重装);

- 递减计数:计数器从预设值开始,每接收到一个时钟脉冲减 1,直至 0 后溢出(或自动重装);

- 定时时间计算 :

定时时间 = 计数次数 × 时钟周期 = 计数次数 / 时钟频率; - 核心功能 :

- 定时中断:计数达到预设值后触发中断,执行特定任务(如 LED 翻转、数据采集);

- 精准延时:通过查询计数器值实现指定时间的延时(如 us 级、ms 级);

- 输入捕获:捕获外部信号的边沿(上升沿 / 下降沿),记录计数器值,计算信号频率、周期或占空比;

- 比较输出:当计数器值与预设比较值相等时,输出特定电平信号(如 PWM 波)。

(二)GPT 定时器:通用精准延时

GPT(General Purpose Timer)是 IMX6ULL 的通用定时器,支持自由运行、输入捕获、比较输出等多种模式,gpt.c主要实现基于自由运行模式 的精准延时功能(us 级、ms 级),核心函数为gpt1_init()、delay_us()、delay_ms()。

1. GPT 初始化代码解析(gpt1_init ())

void reset_fun(void)

{

GPT1->CR |= (1 << 15); // 置位SWR位(Software Reset),复位GPT1

while((GPT1->CR & (1 << 15)) != 0); // 等待复位完成(SWR位自动清零)

}

void gpt1_init(void)

{

// 1. 复位GPT1,确保初始状态一致

reset_fun();

unsigned int t;

t = GPT1->CR; // 读取控制寄存器(Control Register)

t &= ~(7 << 26); // 清除CLKSRC位(时钟源选择,bit26~bit28)

t &= ~(3 << 18); // 清除DBG_MODE位(调试模式,默认关闭)

t |= (1 << 9); // 置位FRR位(Free-Run Mode),使能自由运行模式

t &= ~(7 << 6); // 清除PRESCALER位(预分频系数,bit6~bit8)

t |= (1 << 6); // 预分频系数=1→分频比=1+1=2?实际为bit6~bit8取值N→分频比N+1?

t &= ~(1 << 1); // 清除OM1位(输出模式1,关闭比较输出)

GPT1->CR = t; // 写入配置

// 2. 配置预分频器(PR寄存器,Prescaler Register)

GPT1->PR &= ~(0xFFF << 0); // 清除预分频系数(bit0~bit11,0~4095)

GPT1->PR |= (65 << 0); // 预分频系数=65→分频比=65+1=66

GPT1->CNT = 0; // 计数器(Counter Register)清零

// 3. 使能GPT1

GPT1->CR |= (1 << 0); // 置位EN位(Enable)

}- 关键配置解析 :

- 自由运行模式(FRR 位 = 1):计数器从 0 开始递增计数,达到最大值(32 位计数器为 0xFFFFFFFF)后自动溢出,重新从 0 开始计数,持续循环,适用于精准延时(无需频繁重装计数初值);

- 时钟源选择:代码中未明确设置 CLKSRC 位(默认选择 IPG_CLK),因此 GPT1 的时钟源为 IPG_CLK_ROOT(66MHz);

- 预分频配置:PR 寄存器的 bit0~bit11 控制预分频系数,取值 N(0~4095)对应分频比 N+1。此处设置为 65,即分频比 = 66,因此 GPT1 的实际计数时钟频率 = 66MHz / 66 = 1MHz,时钟周期 = 1us(计数器每计数 1 次对应 1us);

- 常见误区:预分频系数的计算容易混淆 "取值" 与 "分频比",例如 PR 寄存器设置为 65,实际分频比为 66,而非 65,若计算错误会导致延时精度偏差(如误认为分频比 65,时钟频率 = 66MHz/65≈1.015MHz,延时 1us 实际为 0.985us,累积误差会随延时时间增大)。

2. 精准延时函数解析(delay_us ()/delay_ms ())

void delay_ms(unsigned int ms)

{

while(ms--)

{

delay_us(1000); // 1ms = 1000us,直接调用微秒延时函数

}

}

void delay_us(unsigned int us)

{

unsigned int count = 0;

unsigned int old_count = 0, new_count = 0;

old_count = GPT1->CNT; // 记录计数器初始值

while(1)

{

new_count = GPT1->CNT; // 读取当前计数器值

if (new_count != old_count) // 计数器值变化(避免死循环)

{

// 处理计数器溢出(32位计数器从0xFFFFFFFF→0)

if (new_count > old_count)

{

count += new_count - old_count; // 未溢出,累加差值

} else {

count += 0xFFFFFFFF - old_count + new_count; // 溢出,累加溢出部分+当前值

}

}

if (count >= us) // 累加计数达到目标延时值(us),退出

{

return;

}

old_count = new_count; // 更新旧值,准备下一次循环

}

}- 核心逻辑 :

- 由于 GPT1 的计数时钟频率为 1MHz(1us / 次),因此 "count 累加值≥us" 即表示达到目标延时时间;

- 处理计数器溢出:32 位计数器的最大值为 0xFFFFFFFF(约 4294 秒),虽然短延时(如 us/ms 级)中溢出概率极低,但代码中仍需处理,确保延时函数的鲁棒性;

- 精度优化 :

- 关闭中断:延时过程中若发生中断,会导致循环执行延迟,影响延时精度,因此可在

delay_us()函数开头禁用全局中断,结尾恢复; - 避免冗余操作:函数内部尽量减少不必要的变量赋值和判断,提升执行速度;

- 关闭中断:延时过程中若发生中断,会导致循环执行延迟,影响延时精度,因此可在

- 实战应用:该延时函数适用于对精度要求较高的场景,如传感器数据采集(需在特定时间间隔内读取数据)、通信时序同步(如 I2C 总线的起始条件延时)。

(三)EPIT 定时器:周期中断控制

EPIT(Enhanced Periodic Interrupt Timer)是 IMX6ULL 的增强型周期中断定时器,专为周期中断设计,支持自动重装、递减计数等功能,epit.c实现 1s 周期中断,触发 LED 和蜂鸣器状态翻转,核心函数为epit1_init()、epit_irq_handler()。

1. EPIT 初始化代码解析(epit1_init ())

void epit1_init(void)

{

unsigned int t;

t = EPIT1->CR; // 读取控制寄存器

t &= ~(3 << 24); // 清除CLKSRC位(时钟源选择,bit24~bit25)

t |= (1 << 24); // 选择IPG_CLK(66MHz)作为时钟源

t |= (1 << 17); // 置位RLD位(Reload),使能自动重装(中断后加载LR寄存器值)

t &= ~(0xFFF << 4); // 清除PRESCALER位(预分频系数,bit4~bit15)

t |= (65 << 4); // 预分频系数=65→分频比=65+1=66→计数时钟频率=66MHz/66=1MHz

t |= (1 << 3); // 置位OCIEN位(Output Compare Interrupt Enable),使能比较中断

t |= (1 << 2); // 置位RST位(Reset),计数器达到0后复位(重新加载LR值)

t |= (1 << 1); // 置位ENMOD位(Enable Mode),使能自动重装模式

EPIT1->CR = t; // 写入配置

// 2. 配置重载值、比较值、初始计数值

EPIT1->LR = 1000*1000; // 重载值(Load Register):1MHz×1s=1000000次→定时1s

EPIT1->CMPR = 0; // 比较值(Compare Register):计数器减到0时触发中断

EPIT1->CNR = 1000*1000; // 初始计数值(Counter Register):从1000000开始递减

// 3. 中断控制器(GIC)配置

GIC_EnableIRQ(EPIT1_IRQn); // 使能EPIT1对应的IRQ中断

GIC_SetPriority(EPIT1_IRQn, 0); // 设置中断优先级为0(最高优先级)

system_interrupt_register(EPIT1_IRQn, epit_irq_handler); // 注册中断服务函数

// 4. 使能EPIT1

EPIT1->CR |= (1 << 0); // 置位EN位(Enable)

}- 关键配置解析 :

- 时钟源与预分频:与 GPT1 一致,选择 66MHz 的 IPG_CLK,经 66 分频后得到 1MHz 计数时钟(1us / 次),确保定时精度;

- 工作模式:"自动重装 + 递减计数 + 比较中断",计数器从 LR 寄存器的 1000000 开始递减,每 1us 减 1,减到 0 时触发中断,同时自动加载 LR 值,开始下一轮计数,实现 1s 周期中断;

- 中断配置:IMX6ULL 的中断需通过 GIC(Generic Interrupt Controller)管理,步骤为 "使能 IRQ→设置优先级→注册中断服务函数",优先级 0 为最高,确保 EPIT1 中断能及时响应;

- 定时时间验证 :

定时时间 = LR值 / 计数时钟频率 = 1000000 / 1MHz = 1s,与预期一致,若需调整定时时间,只需修改 LR 值(如 500000→0.5s,2000000→2s)。

2. 中断服务函数解析(epit_irq_handler ())

void epit_irq_handler(void)

{

if ((EPIT1->SR & (1 << 0)) != 0) // 检查中断标志位(SR寄存器的OCIF位,bit0)

{

led_nor(); // LED状态翻转(自定义函数,控制GPIO电平)

beep_nor(); // 蜂鸣器状态翻转(自定义函数,控制GPIO电平)

EPIT1->SR |= (1 << 0); // 清除中断标志位(写1清零)

}

}- 核心注意事项 :

- 中断标志位检查:必须先判断中断标志位是否置位,避免误触发(如其他中断共享 IRQ 线时);

- 清除中断标志位:EPIT 的中断标志位需通过写 1 清零,若未清除,中断会持续触发,导致 CPU 陷入死循环;

- 业务逻辑简化:中断服务函数应尽量简洁,避免执行耗时操作(如 printf、延时函数),否则会影响中断响应实时性。若需复杂处理,可设置标志位,在主循环中执行;

- 实战优化:若需实现多周期定时(如 1s、2s 切换),可在中断服务函数中动态修改 LR 寄存器的值,无需重新初始化 EPIT。

(四)51 单片机定时器与 IMX6ULL 定时器对比

为帮助开发者更好地理解定时器的共性与差异,以下对比 51 单片机定时器与 IMX6ULL 的 GPT/EPIT:

| 特性 | 51 单片机定时器(Timer0/Timer1) | IMX6ULL GPT | IMX6ULL EPIT |

|---|---|---|---|

| 计数位数 | 8 位 / 16 位(可配置) | 32 位 | 32 位 |

| 时钟源 | 系统时钟 12 分频(固定) | 可选(IPG_CLK、PLL 时钟等) | 可选(IPG_CLK、PLL 时钟等) |

| 预分频器 | 无(仅系统时钟 12 分频) | 12 位可编程(0~4095) | 12 位可编程(0~4095) |

| 工作模式 | 定时模式、计数模式 | 自由运行、输入捕获、比较输出 | 递减计数、自动重装、比较中断 |

| 定时精度 | ms 级(受限于 16 位计数和固定分频) | us 级(32 位计数 + 可编程分频) | us 级(32 位计数 + 可编程分频) |

| 中断响应 | 单级中断(优先级固定) | 多级中断(GIC 可控优先级) | 多级中断(GIC 可控优先级) |

| 核心应用 | 简单定时、串口波特率发生器 | 精准延时、脉冲测量 | 周期中断、周期性任务触发 |

三、核心问题解答与实战总结

(一)核心问题解答(含代码关联)

-

PLL、Prescaler、PFD、MUX、CG 门在时钟树中的作用

- PLL:倍频 + 相位同步,提升时钟频率(如 ARM PLL 将 24MHz 倍频至 2112MHz),为高性能模块提供支持;

- Prescaler:整数倍分频,降低时钟频率(如 GPT/EPIT 的 66 分频、AHB 总线的 3 分频),适配外设需求;

- PFD:分数倍调频(可升可降),实现高精度频率匹配(如 528PLL 的 PFD 输出 352MHz 供给 USB);

- MUX:时钟源切换(如 ARM 内核在 step_clk 与 PLL 时钟间切换),保证系统灵活性与稳定性;

- CG 门:控制时钟通断(如 CCGR 寄存器控制外设时钟),优化系统功耗。

-

IMX6ULL 的 PLL 与 PFD 数量及配置逻辑

- PLL 数量:核心 PLL 包括 ARM PLL(PLL1)、528PLL(PLL2)、480PLL(PLL3),共 3 个;

- PFD 数量:每个 PLL 对应 4 个 PFD,共 12 个;

- 配置逻辑:"PLL 倍频 + PFD 分数分频",先通过 PLL 将基础时钟提升至高频,再通过 PFD 微调,输出多档位精准时钟,满足不同外设需求。

-

ARM PLL 的配置流程(含代码步骤)

- 切换过渡时钟:通过 MUX 将 ARM 内核时钟切换为 24MHz step_clk(

CCM->CCSR |= (1 << 2)); - 配置预分频器:设置 CACRR 寄存器实现二分频(

CCM->CACRR |= (1 << 0)); - 配置 PLL 倍频:设置 PLL_ARM 寄存器的倍频因子(

CCM_ANALOG->PLL_ARM |= (88 << 0)); - 等待 PLL 稳定:可选(通过 PLL_STATUS 寄存器判断);

- 切换目标时钟:通过 MUX 将内核时钟切换回 PLL 输出(

CCM->CCSR &= ~(1 << 2))。

- 切换过渡时钟:通过 MUX 将 ARM 内核时钟切换为 24MHz step_clk(

-

GPT 与 EPIT 的工作原理及应用场景差异

- GPT:支持自由运行、输入捕获、比较输出模式,核心应用为精准延时(如

delay_us())、脉冲测量(输入捕获)、PWM 生成(比较输出); - EPIT:支持递减计数、自动重装、比较中断模式,核心应用为周期中断(如 1s 翻转 LED)、周期性任务触发(如定时数据采集)。

- GPT:支持自由运行、输入捕获、比较输出模式,核心应用为精准延时(如

(二)实战总结与优化建议

-

时钟配置优化:

- 稳定性优先:PLL 倍频因子不宜过大(建议≤100),避免输出时钟不稳定;

- 功耗优化:闲置外设及时关闭 CG 门,低功耗模式下切换为低频时钟源;

- 容错设计:配置时钟源切换时,添加延时或等待锁定逻辑,避免时序错乱。

-

定时器应用优化:

- 精度优化:延时函数中禁用全局中断,中断服务函数简化业务逻辑;

- 多任务处理:多个定时任务可通过一个定时器 + 软件定时器实现(如用 EPIT 产生 1ms 中断,在中断中维护多个软件定时器计数器),减少硬件定时器占用;

- 错误处理:定时器初始化后检查配置是否生效(如读取 CR 寄存器确认模式设置),中断函数中检查标志位避免误触发。

-

常见问题排查:

- 时钟频率错误:检查 PLL 倍频因子、预分频系数计算是否正确,寄存器配置位是否写对;

- 定时器定时不准:检查时钟源频率是否正确,预分频器配置是否匹配,中断是否被其他高优先级中断阻塞;

- 中断不触发:检查 GIC 配置(是否使能 IRQ、优先级是否正确)、中断标志位是否清除、中断服务函数是否注册成功。