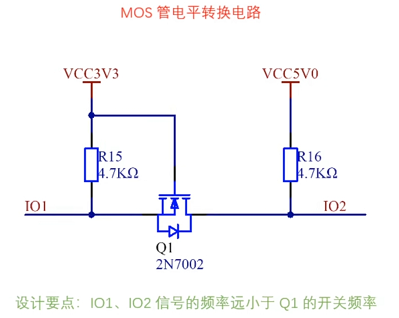

这个电路是典型的N 沟道 MOS 管反相电平转换电路 ,核心功能是将 3.3V 数字信号转换为 5V 数字信号,适用于不同电压域的 MCU 或外设之间的信号交互,下面从元件作用 、工作原理 、设计要点展开分析:

一、关键元件作用拆解

| 元件 | 作用说明 |

|---|---|

| Q1(2N7002) | N 沟道增强型 MOS 管,核心开关器件,通过栅极电压控制漏极与源极的通断,实现电平转换。 |

| R15(4.7KΩ) | 栅极上拉电阻,当输入信号IO1悬空时,将栅极上拉至 3.3V,防止 MOS 管误触发;同时在IO1低电平时,为栅极提供放电通路,保证 MOS 管快速截止。 |

| R16(4.7KΩ) | 漏极上拉电阻,将漏极(IO2)上拉至 5V,MOS 管截止时输出高电平,导通时输出低电平。 |

二、核心工作原理

该电路通过 MOS 管的开关特性实现 3.3V→5V 的反相电平转换,分两种工作状态:

1. 输入IO1为高电平(3.3V)

- 栅极电压

Vg=3.3V,源极接地(Vs=0V),因此栅源电压Vgs=3.3V-0V=3.3V,大于 2N7002 的阈值电压(Vth≈2V),MOS 管饱和导通。 - 漏极(

IO2)通过导通的 MOS 管被拉至地,输出低电平(0V)。

2. 输入IO1为低电平(0V)

- 栅极电压

Vg=0V,栅源电压Vgs=0V-0V=0V,小于阈值电压,MOS 管截止。 - 漏极(

IO2)通过 R16 上拉至VCC5V0(5V),输出高电平(5V)。

→ 最终实现反相电平转换:3.3V 高电平→5V 低电平;3.3V 低电平→5V 高电平。

三、设计要点解读

-

信号频率限制 设计要点提到 "IO1、IO2 信号的频率远小于 Q1 的开关频率",2N7002 的开关频率通常可达几十 MHz,因此该电路适合低频 / 中频数字信号(如几 MHz 以下),若信号频率过高(接近 MOS 管开关频率),会导致开关速度不足,出现信号上升沿 / 下降沿失真。

-

电阻取值优化

- R15(4.7KΩ):保证栅极驱动电流足够(既避免 IO1 悬空时误触发,又能在低电平时快速放电),若阻值过大,栅极放电变慢,MOS 管截止延迟;阻值过小,会增加输入电流,加重前级负载。

- R16(4.7KΩ):平衡输出电平的上升速度与功耗,阻值过大时,输出高电平的上升沿会变慢(寄生电容充电慢);阻值过小时,MOS 管导通时的电流过大,增加功耗。

-

MOS 管选型关键参数

- 阈值电压

Vth:2N7002 的Vth≈2V,3.3V 输入可保证Vgs>Vth,导通可靠。 - 漏源耐压

Vds:2N7002 的Vds=60V,远大于 5V 输出电压,满足耐压要求。 - 导通电阻

Rds(on):约 5Ω,导通时漏极压降极小,输出低电平接近 0V,保证信号逻辑清晰。

- 阈值电压

-

电平转换方向 该电路仅支持3.3V 转 5V(低电压域转高电压域),若需 5V 转 3.3V,需改用 P 沟道 MOS 管或双向电平转换芯片(如 SN74LVC8T245)。

四、电路优缺点

- 优点:电路简单,元件少,成本低;转换速度快,适合数字信号;功耗低(截止时几乎无电流,导通时仅漏极电流)。

- 缺点:输出信号与输入反相,若需同相转换需额外增加反相电路;输入信号频率不能过高;无 ESD 保护,高静电场景需在输入 / 输出端增加 TVS 管。