一、前言

FGPA器件中,I/O的模块分布以bank来划分,bank可分为HR(High Range) IO,HP(High Performance) IO,HD(Hign Density) IO三类,每个bank包含一定数量的可配置I/O。

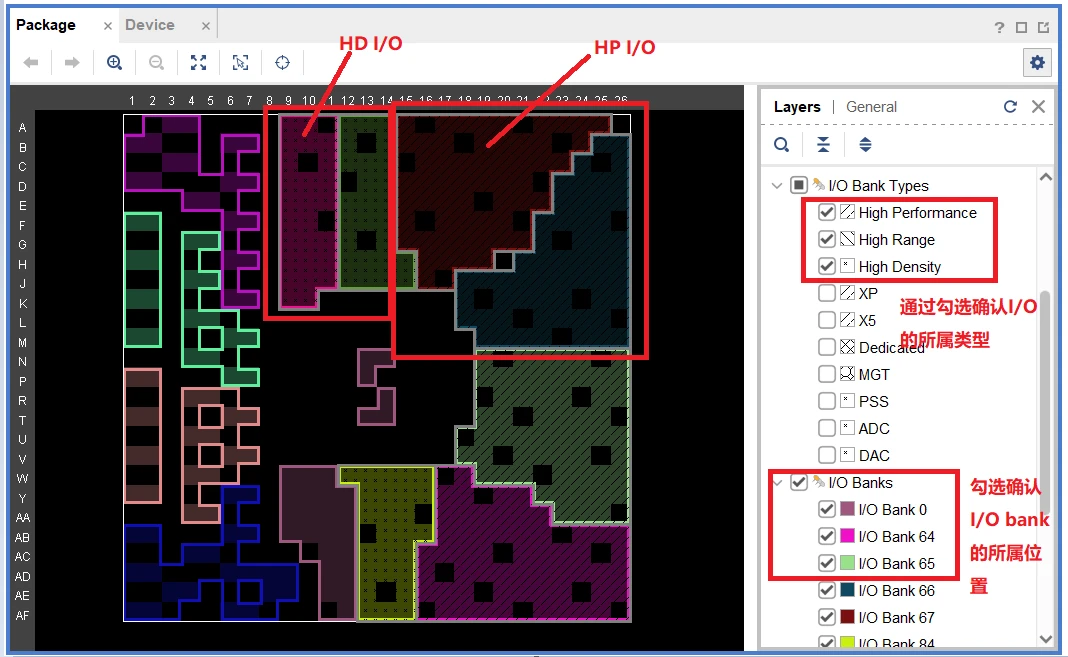

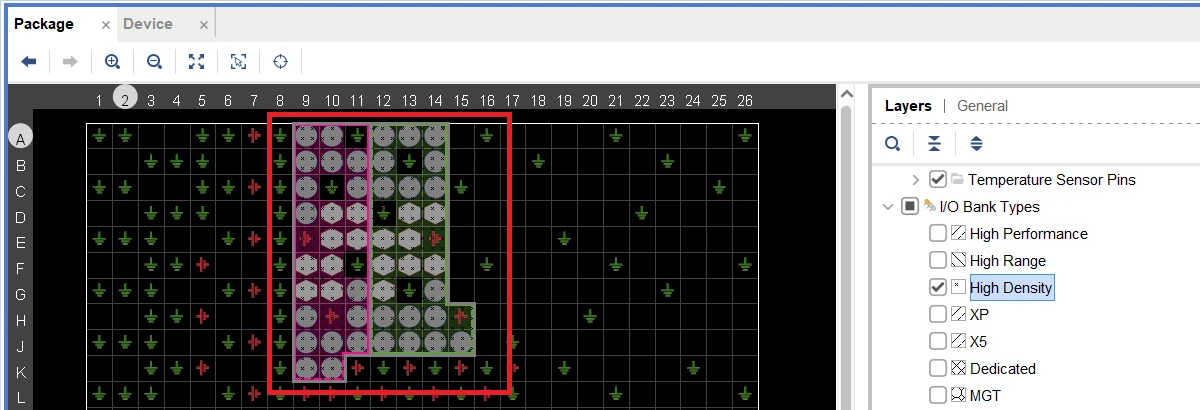

以Kintex UltraScale+器件为例,在I/O Planning中可以看到I/O bank的分布。

二、I/O Type

Xilinx器件目前支持的三种I/O 类型:HP I/0,HR I/0,HD I/0

HP I/0 banks:主要是满足高速存储和其他芯片与芯片接口的性能要求,支持的电压高达1.8V。

HR I/O banks:主要是满足支持更广泛的I/0标准,支持的电压最高可为3.3V。

HD I/O banks:主要是支持低速接口。

2.1 HR I/O与HP I/O

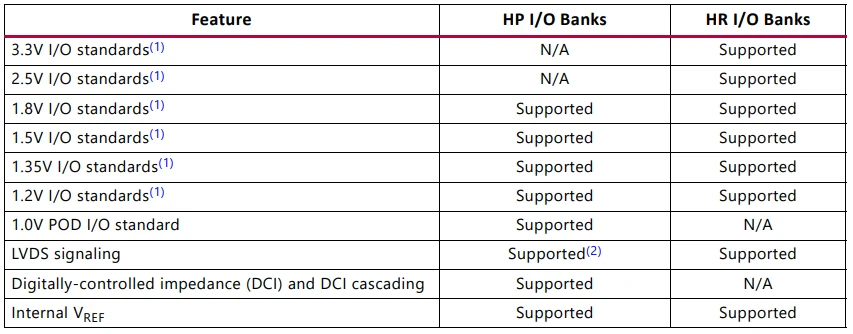

Ultrascale架构的器件HR I/O和HP I/O支持的电压差异如下表,HP I/O最高到1.8V

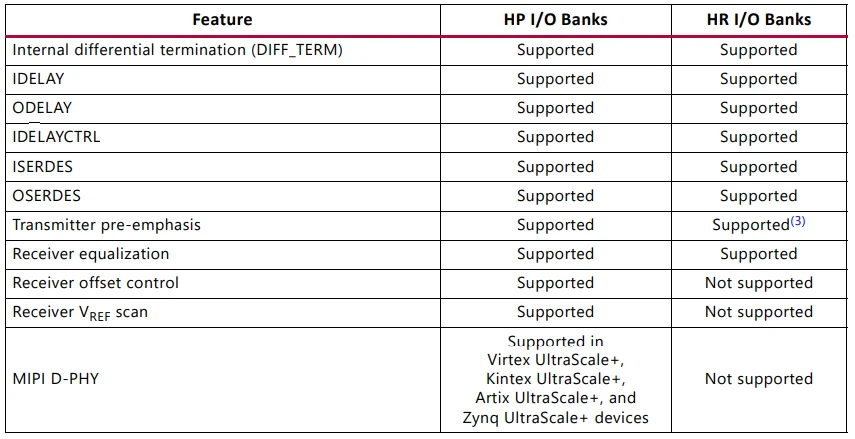

同时,HP I/O和HR I/O的内部支持配合一些其他单元如延时单元IDELAY/ODELAY和串并转换单元ISERDES/OSERDES等,具体支持的差异如下表

2.2 HP I/O中的DCI功能

随着器件引脚增加和系统时钟速度加快,PC板的设计和制造难度也随之增加。随着边缘速率不断加快,保持信号完整性成为了一个关键问题。PC板上的走线长度必须适当,以避免反射或振荡。

为了适当断开走线,通常会添加电阻,使输出和/或输入的阻抗与接收器或驱动器的阻抗相匹配,以达到与走线阻抗一致。然而,由于器件输入/输出(I/O)的增加,在器件引脚附近添加电阻会增加电路板面积和元件数量,在某些情况下在物理上无法实现。为了解决这些问题并实现更好的信号完整性,AMD开发了数控阻抗(DCI)技术。

根据I/O标准,DCl既可以控制驱动器的输出阻抗,也可以在接收器端添加并联终端,目的是精确匹配传输线的特性阻抗。DCl在I/O内部主动调整这些阻抗,以校准放置在VRP引脚上的外部精密参考电阻。这可以补偿由于工艺变化导致的I/O阻抗变化。此外,它还可以连续调整阻抗,以补偿温度变化和电源电压波动的影响。许多设计需要使用多个DCl参考VRP引脚,在这种情况下,每个VRP引脚都需要一个唯一的参考电阻。

2.3 输出驱动强度

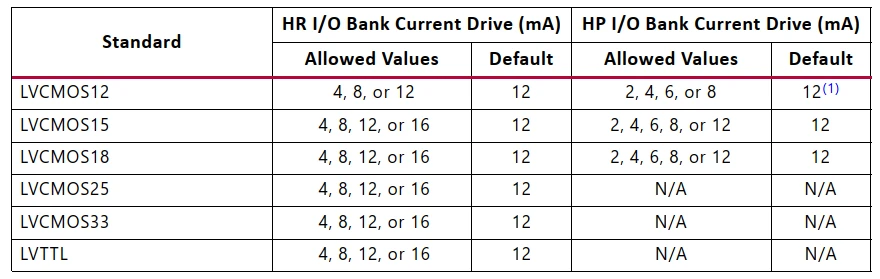

对于LVCMOS和LVTTL标准,HR I/O和HP I/O可配置的驱动负载强度也不同,HP I/O上允许设置的值总体上会更小

2.4 HD(高密度) I/O

HD I/O(高密度 I/O) Bank 是 Select I/O 资源,支持电压从 1.2V 到 3.3V 的各种 I/O 标准。HD I/O 针对信号端电压参考和伪差分I/O标准进行了优化,工作时数据速率高达 250 Mb/s。此外,HD I/O对真差分输入(带外部终端)的一定程度的支持,以支持LVDS和LVPECL时钟输入。

2.4.1 HD I/O标准

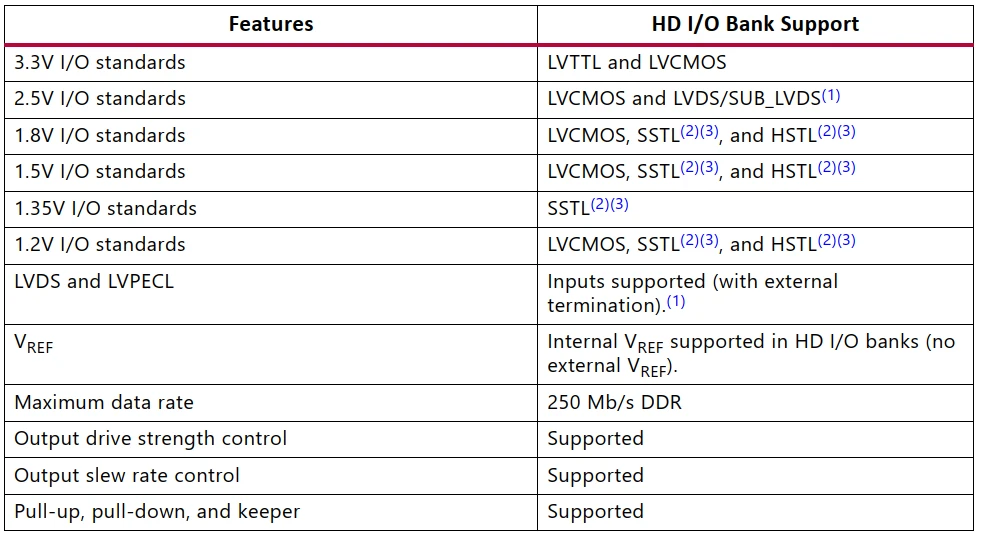

HD I/O 还包含接口逻辑,包括寄存器和静态延迟线,以支持异步、系统同步和基于时钟的源同步接口,HD I/O Bank 支持的特性如下。

2.4.2 HD I/O逻辑资源

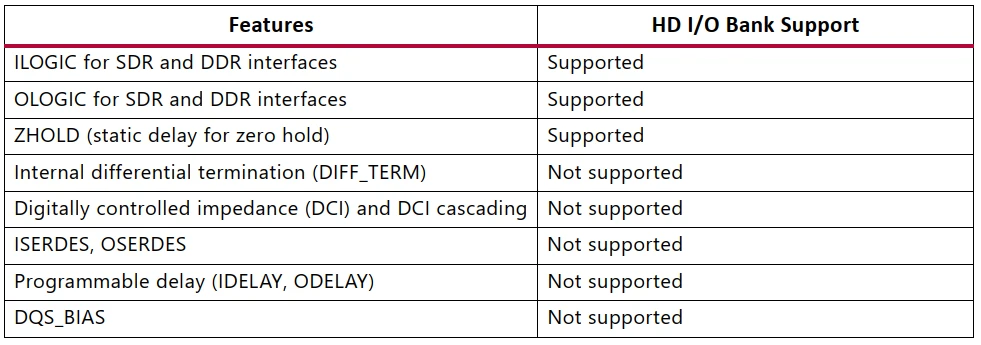

对于I/O内接口逻辑资源的支持情况如下,不支持DCI,SERDES和DELAY

HD I/O不支持差分终端或 LVDS/SUB LVDS 输出,但在HP I/O内支持。

SSTL 和 HSTL 输入支持可选的 502 个片上输入终端。

SSTL、HSTL 和 HSUL 支持可实现传统接口和芯片间接口,不支持与 DRAM 内存设备(DDR3、DDR4、LPDDR2 或 LPDDR3)的接口。

2.4.3 HD I/O Bank资源

每个 HD I/O Bank包含 24 个 I/O 引脚。每个bank内有四对支持时钟的引脚,可用于访问时钟资源,或在不用作输入时钟时作为用户 I/O。当定义为单端标准时,HD I/O 引脚支持输入、输出和双向工作模式。成对的 I/O 引脚可用于支持差分标准功能,对于伪差分标准,例如 DLFF SSTL15,提供输入、输出和双向支持。真差分标准,例如 LVDS25,只能用作输入缓冲器。下图为xcku3p-ffvb676-2-i Package图中的2个HD I/O bank区域。

2.5 HP I/O和HR I/O约束

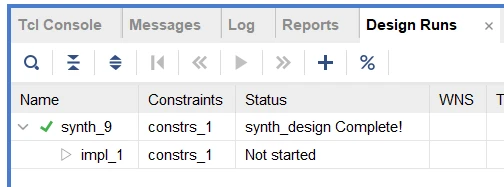

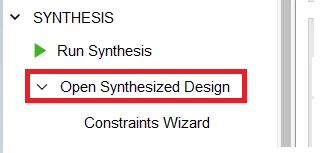

进行I/O 约束必须先将设计运行完synthesis阶段

打开综合设计

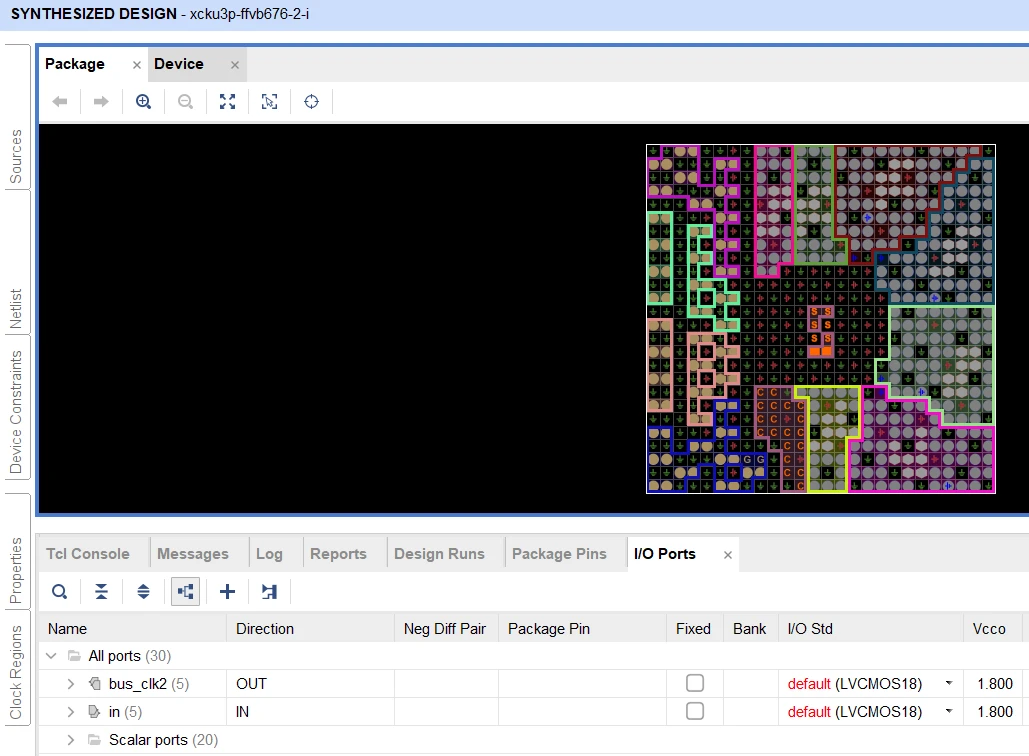

进入到package界面

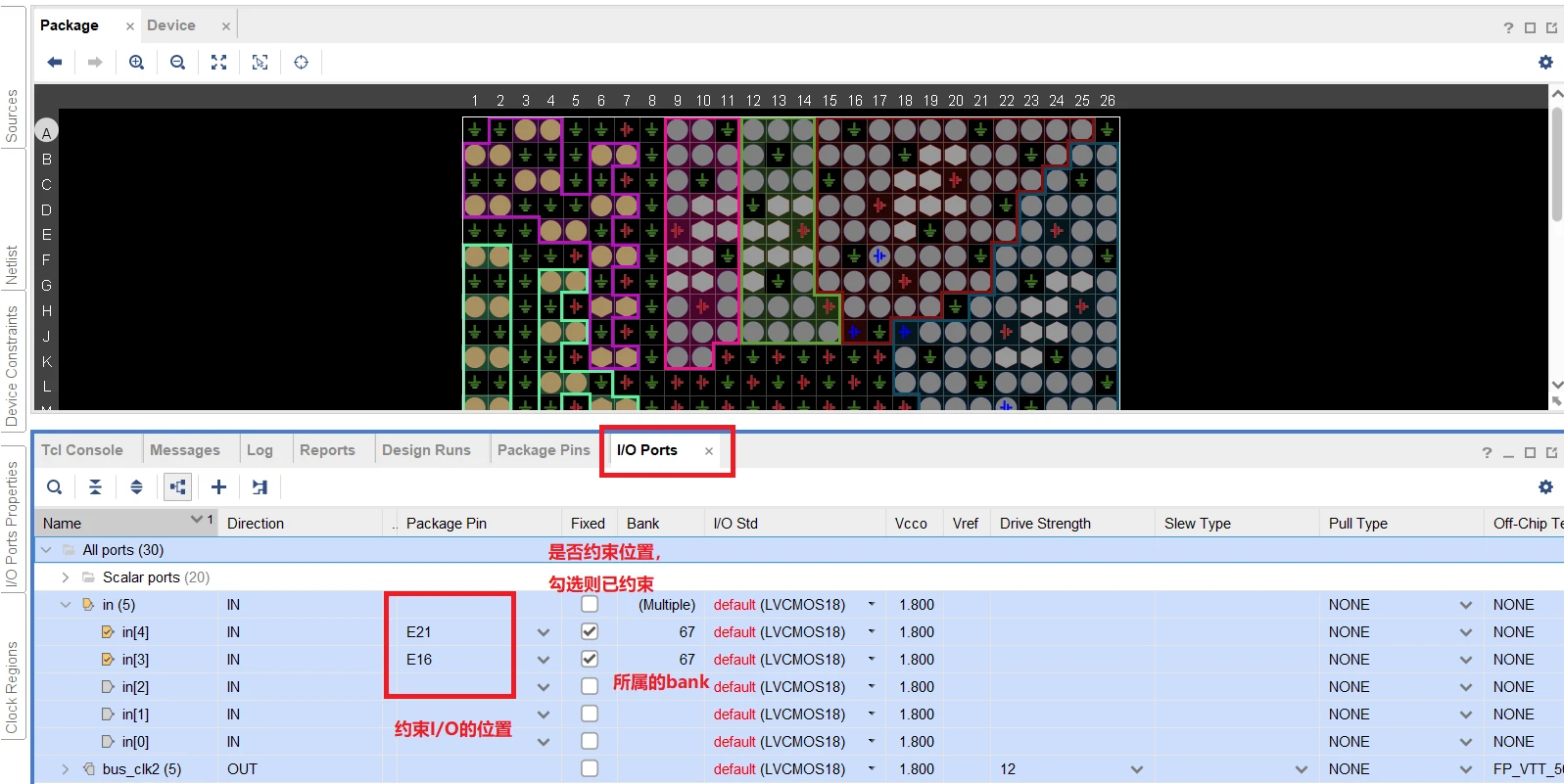

设计中,在I/O Ports界面中展示了设计中的I/O,Fixed勾选的表示已进行位置约束,Package Pin列即展示具体的位置坐标,如下图的E21,在下图的Package界面可找到该位置。该列可直接设置,也可鼠标右键选中IO,按住后一直拖入到Package中需约束的位置,根据Bank的约束可约束到HR I/O或HP I/O上,如下图的Bank 67为HP I/O。

三、参考资料

《ug571-ultrascale-selectio.pdf》