想当初笔者学习三极管的时候,既没有仿真,也没有实际电路,整个靠脑瓜子建立模型,最后bug太多,陷死于知识旋涡中。因为无法建立体系最终啥也没学会,最近又重新捡起颇有所得。

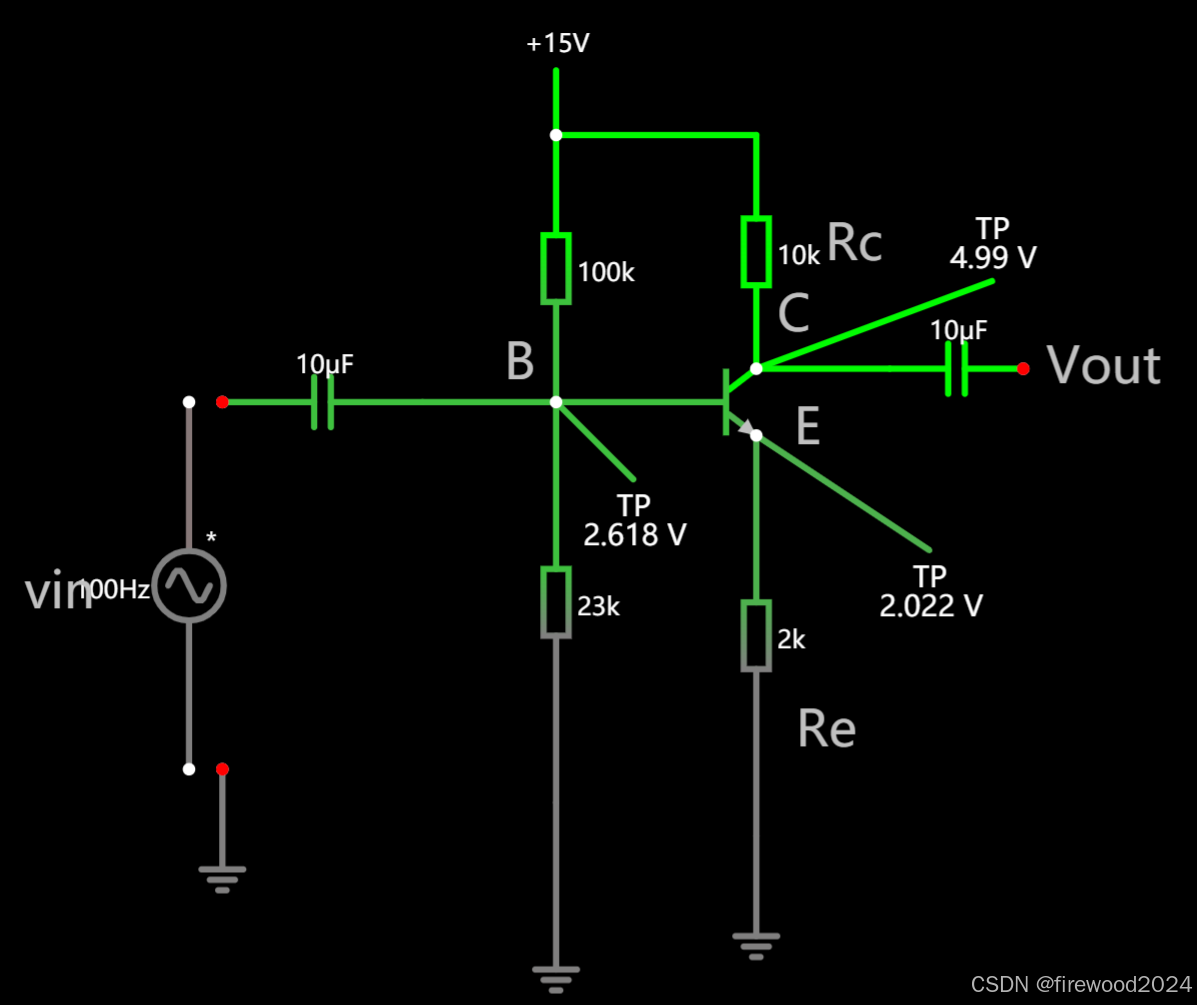

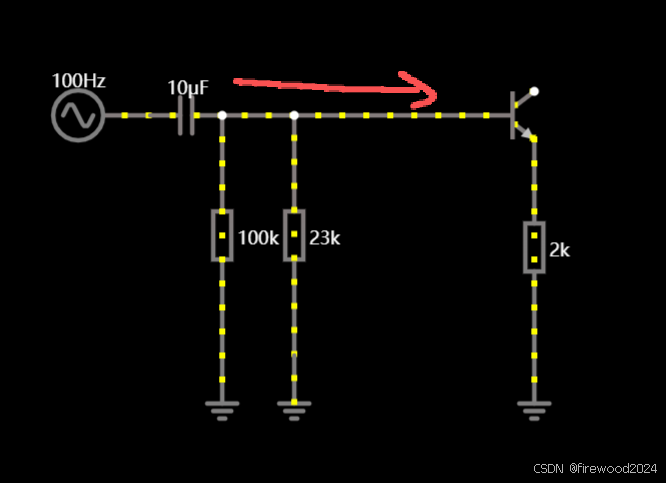

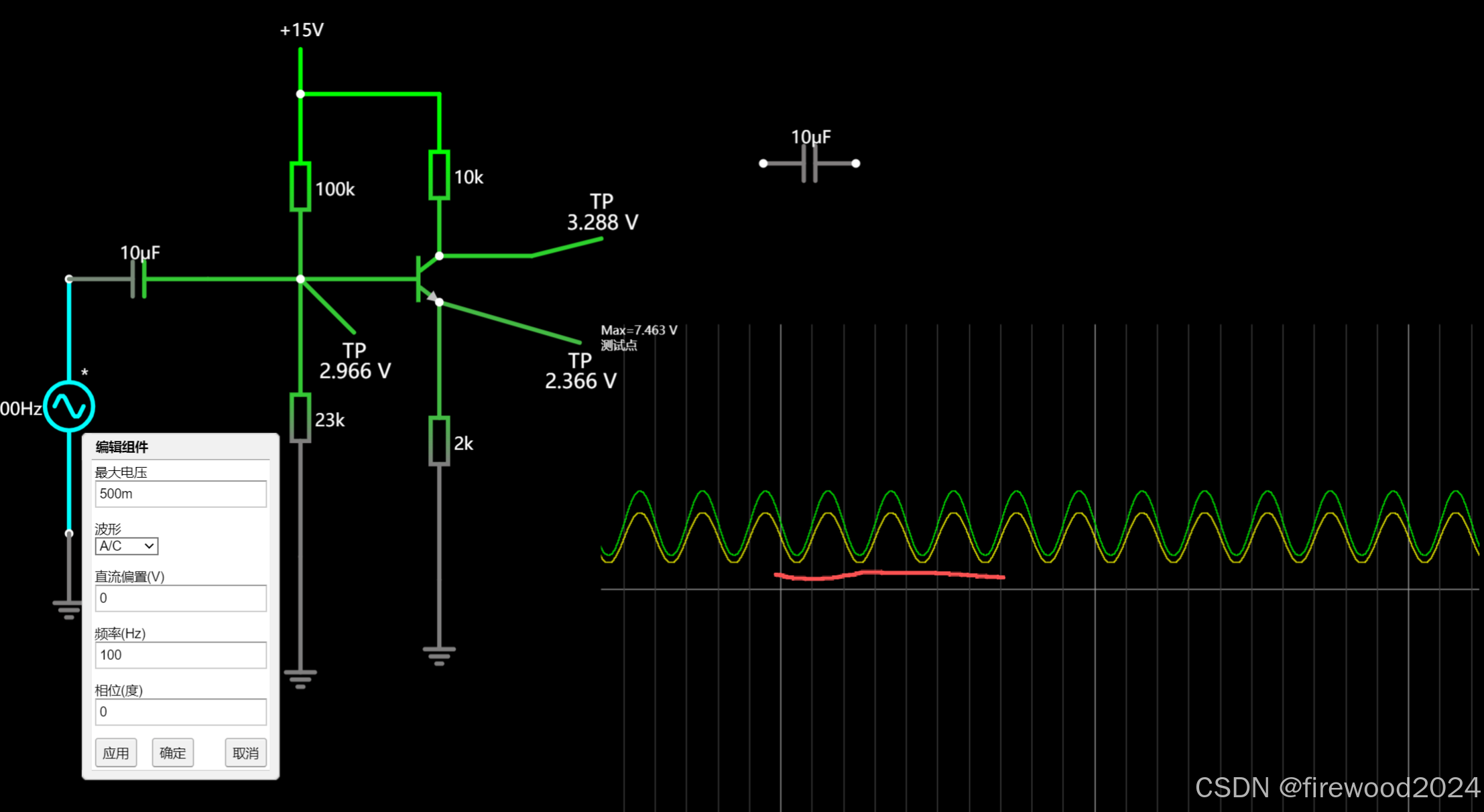

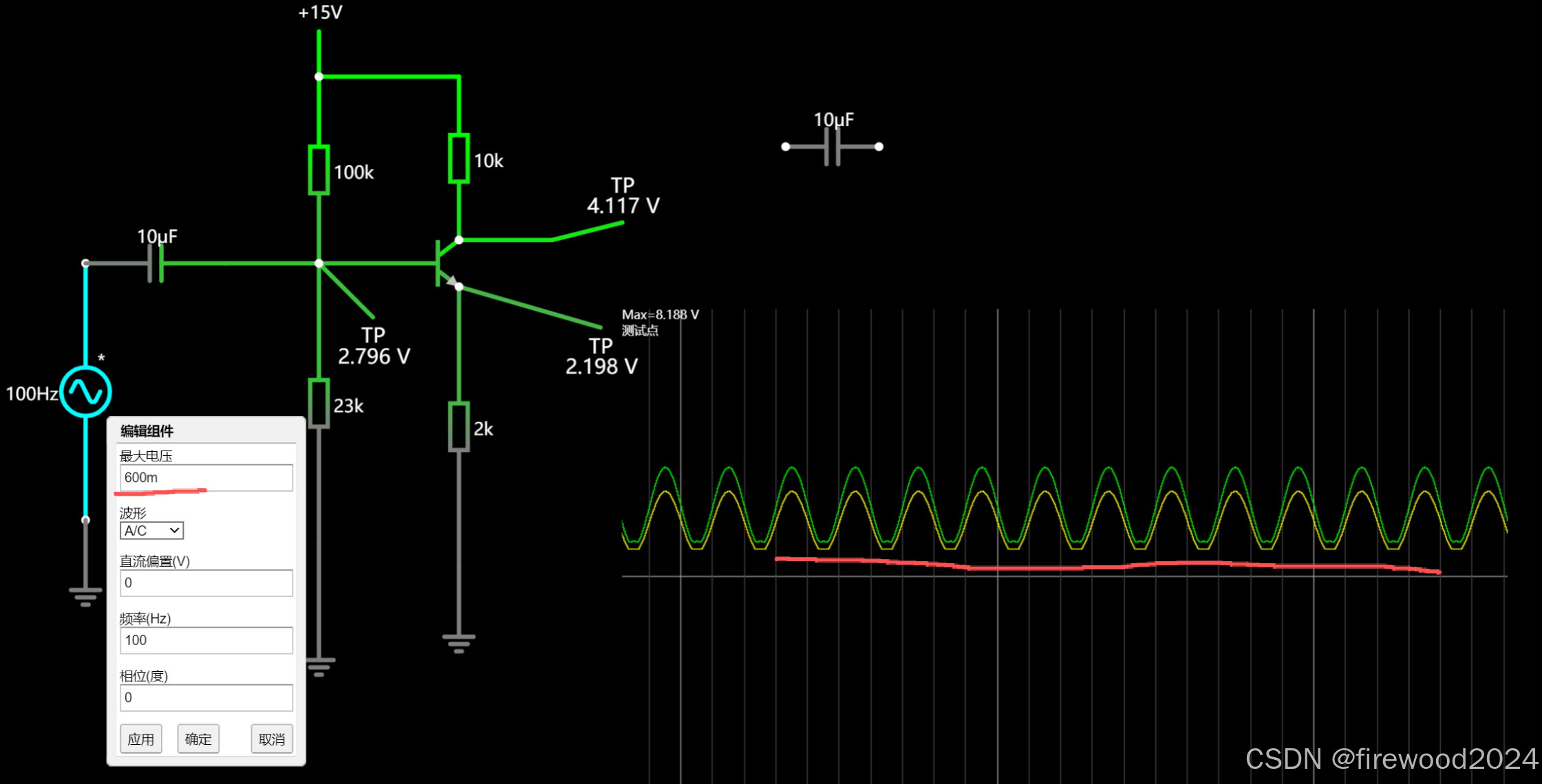

首先看共射极放大电路的原理图:该电路是由Circuit仿真软件得出的结论

- 首先是确认静态工作点,即没有输入信号vi只留下直流偏置时候的电路情况;

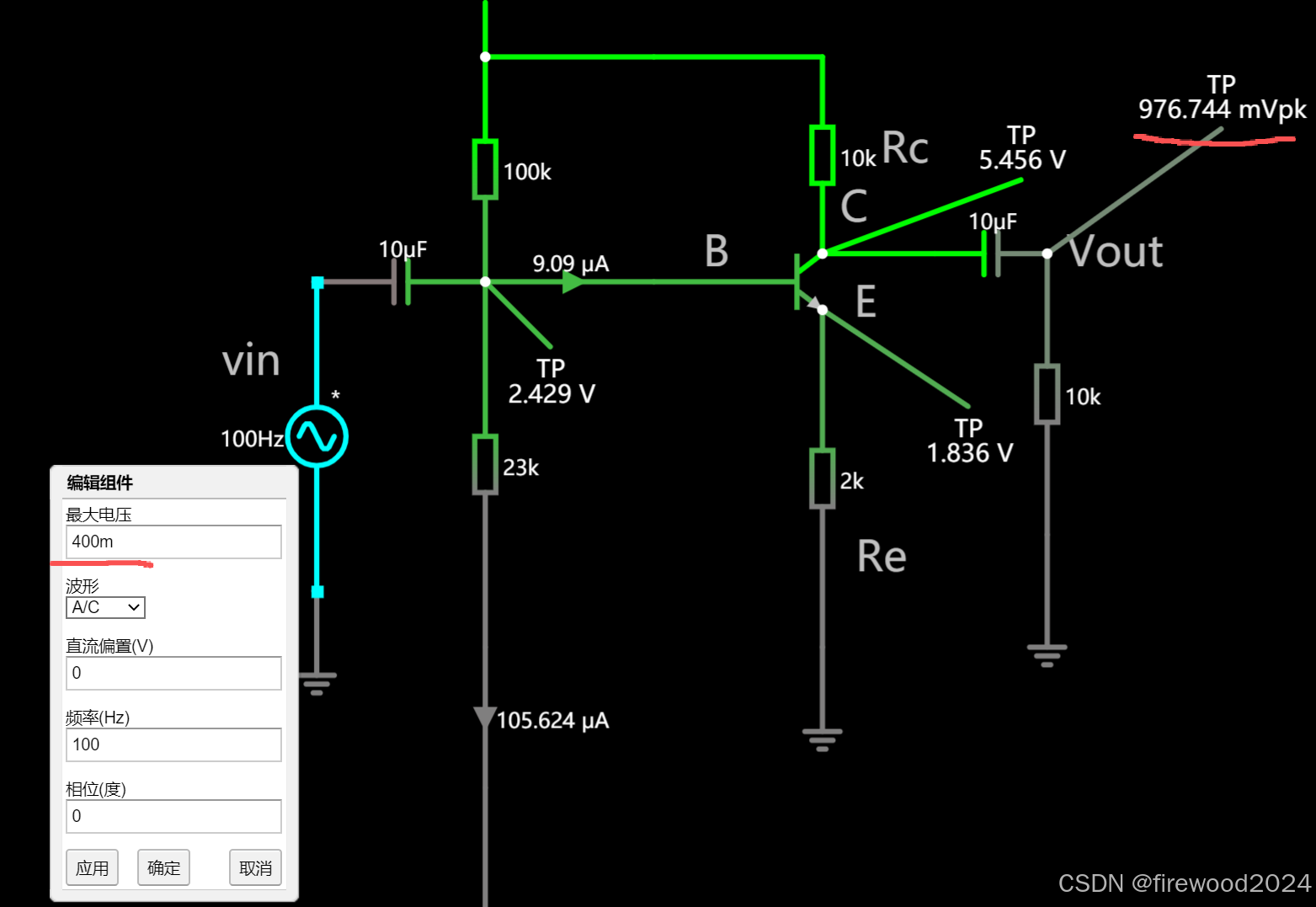

得到基极电压 Vb = 2.6V,集电集电压 Vc = 4.99V。这是很重要的两个静态工作点。

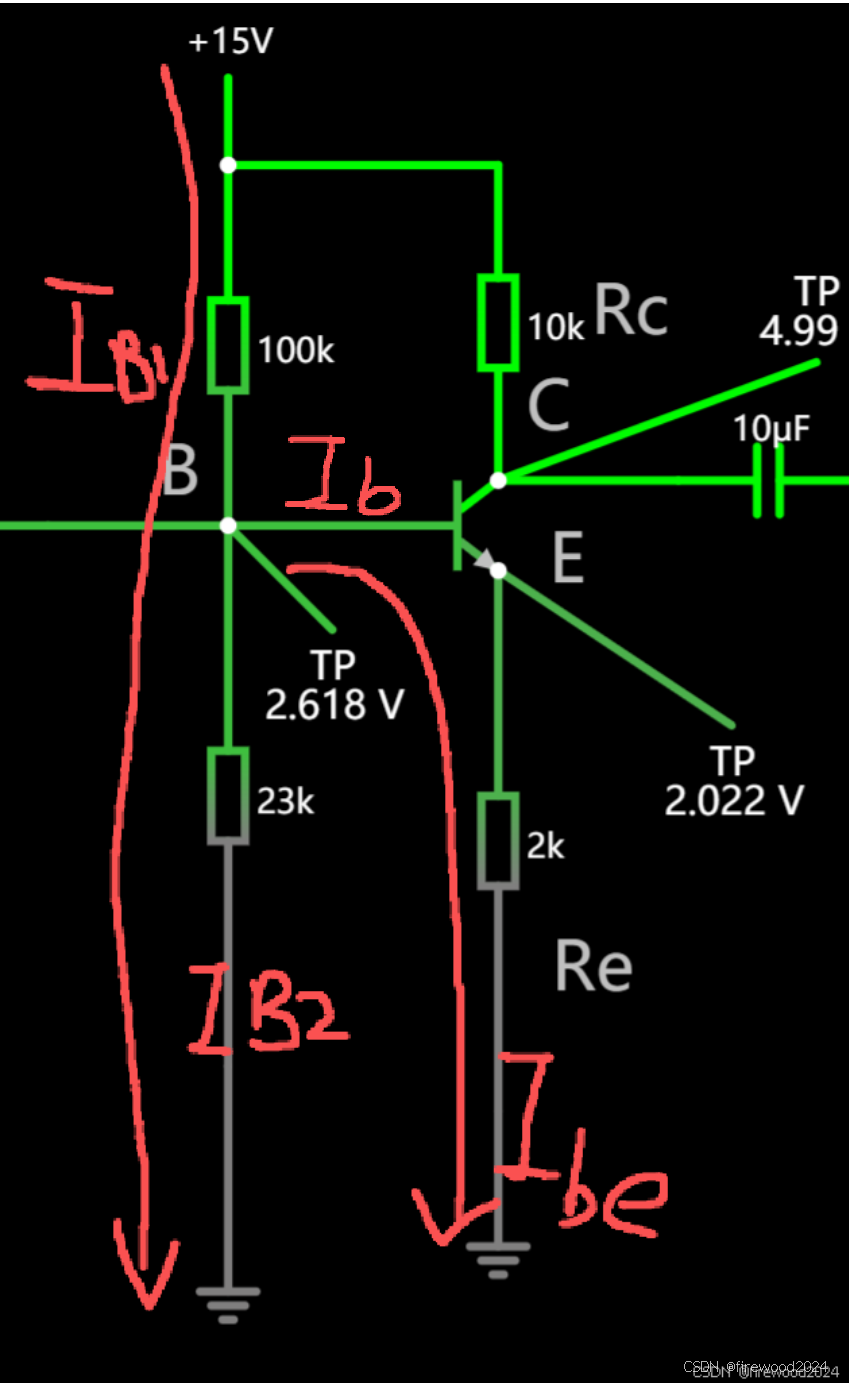

我们用理论知识来求解一下这个过程;看图

为什么基极的电压可以约等于VCC在两个电阻上的分压?

- 从电流回路来说,还有一条支路电流Ibe会从B点流出,流入BE极再流经Re最后灌入GND,假设这条支路的等效阻抗为Re',从并联等效阻抗的角度来说,与B1 = 100K电阻分压的阻抗,是B2 = 23K与Re'的并联阻抗 Rb2//Re'。

- 那么这个等效阻抗多大呢,Rb2//Re'?从结论来说 Rb2//Re' ≈ Rb2,这说明对于Rb2来说Re'阻抗远远大于它,从数量级来说Re'最起码要有230K,哎这就很反直觉了,为什么Ibe的这个支路的阻抗这么大呢?这不合理啊,BE结正向导通后,它的阻抗很小啊,Re的电阻也只有2K啊,两者相加的的阻抗应该是2K多一点啊?为什么会这样呢?

- 如果单独的设立一个电路,找一个二极管和2K电阻串联,使二极管正向偏置,带电测试得到的阻抗确实是2K多。

- 看似是矛盾了啊,但这就是三极管能够放大的原因。

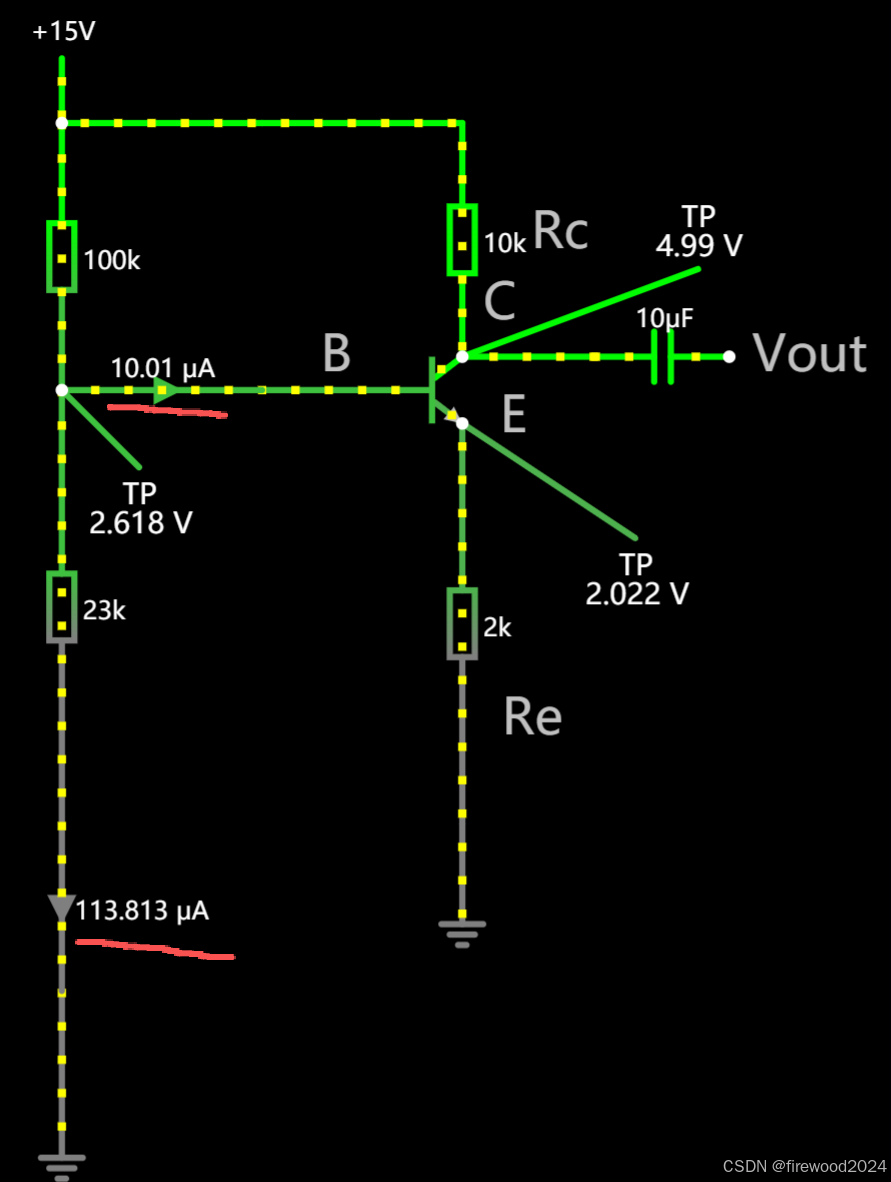

- 更具并联的端口电压原理; ib2*RB2 = Ib *Rx(Rx就是支路的等效阻抗),这个式子必然是正确的,然后我们实际测试或者通过仿真软件得到以下结果:

从仿真软件看出:Ib2的电流是Ib电流的11倍左右,即Rx的阻抗大约是Rb2的11倍即23K*11 = 253K. 从这个结论上可以看出另一支路的等效阻抗并非是之前的2K多一点,而是远远大于它。

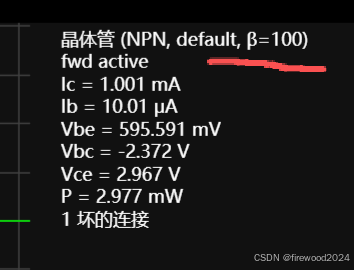

- 造成这个原因是电流流出三极管后,Ib的电流被放大了100倍,即IB = 100* 10ua = 1MA,那么它在Re上产生的压降就由原先的 10ua* 2K = 0.02V 变成了现在1ma*2K = 2V;看一下仿真软件的直流放大倍数β;

- 假设三极管不具有放大功能那么B的电压就会是:0.6V(Vbe) + 0.02V =0.62V;而不是现在的2.6V。

- 因此在选择直流分压电阻的时候,它的阻值不能取的太大,否则会导致总电流太小,从而导致Ib的电流不能满足最基本的条件 Ib1 > 10iB ;换句话说分压电阻产生的总电流最起码要大于Ib10倍以上,否则它的分压点就不约等于两个电阻分压。以该式为例:23/(100+23) *15 = 2.8V,但仿真只有2.6V,它往下偏了0.2V。

第二个问题是确定交流放大倍数Au;(IC,IE.ic,ie 大写的表示直流分量或者直流分量加交流分量,小写的只代表交流分量,请注意区别)

- 因为IE = IB +IC ; IB远远小于IC,因此有 IE ≈ IC。

- 输入端的交流路径是;vi - C(耦合电容) - Vbe - Re -GND ;当PN结正向偏置的时候,我们认为BE结对交流信号是无阻抗或者低阻抗的。因此vi上的压降全部都落在Re上,得到电流ie = vi/Re;

- 由前文得知 IE ≈ IC;得出 ie ≈ ic(即因为交流输入信号引起的电流变化是一致的); 因此VCC处的电压就是:VCC - IC*Rc 。显然当vi变大,IE变大,IC变大,在Rc电阻上的压降就变大,VC集电极电压反而是变小的,因此vc和vi显然是反相的。

- 显然用 VCC - IC*Rc不利于直观的理解集电极C处的电压情况,前文提到静态工作点的时候,我们计算出了VC的静态电压5V,那么集电极出的电压就可以变成,VC + vc == VCC - IC*Rc;即直流电压加上交流电压,因此有当vi是正的时候,集电极电压就是 VC - ic*RC,vi为负的时候 集电极电压是:VC + ic*RC;

- 显然我们需要的是把输入信号放大,因此要除去电压信号中的直流分量。得到交流信号为Vo = vc ,因此Vo/vi = -ic*RC/Ie*Re = -Rc/Re -5 ;即把输入信号放大5倍但是相位是反的;显然交流放大倍数只和Rc与Re的电阻有关,这是一个很重要的结论。

- 以该例说明当vi = 0.5V,那么VC处的电压是 VC + vc = 5 - 0.5X5 = 2.5V,当vi = -0.5V 那么VC处的电压是 5+ 0.5*5 = 7.5V;如果vi信号输入的最大电压就是0.5V即Vpp = 1V的时候,VC处的电压范围就是 2.5 ~ 7.5V它的交流电压是5VPP;

第三个问题,vi的交流通路路径不只有前文提到的一条,那么vi的输入信号难道就全部的落在了Re上且在别处没有分压?

- 因此要画出vi的交流通路,在此之前需要知道VCC作为理想电源也被认为是交流地,即VCC对于交流信号来说就是GND。

- 那么看等效图

- 可以看出这是个高通滤波器,23K和100K的等效并联电阻约是18.7K,晶体的输入阻抗很大,前文在求静态工作点的时候提过它也会略微降低输入电压,因此这个并联等效电阻认为是18K。

- 求这个高通滤波器的截止频率: 即求它的半功率点也就是电容上的阻抗等于电阻的时候的频率,18K = 1/2πfc 求得 fc = 1/2π*10uf*18K ≈ 0.9HZ

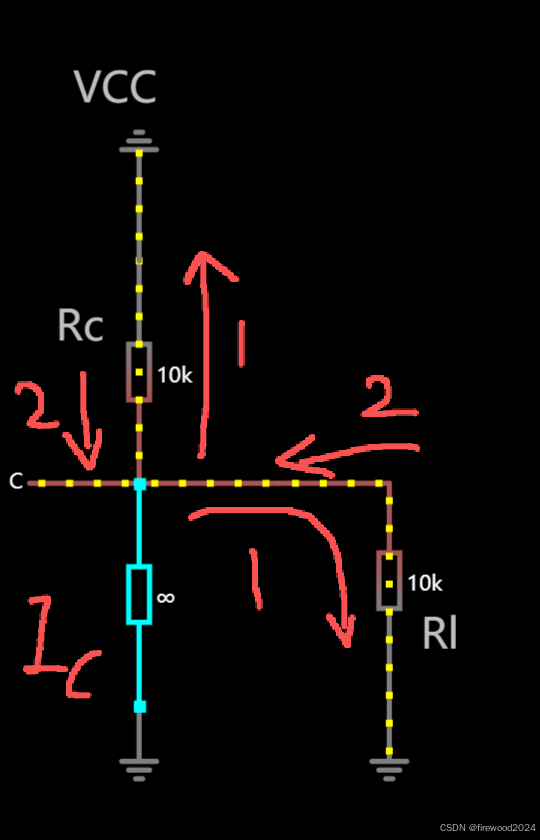

第4个问题,在讨论输出信号vc的时候,电路都是悬空的,当集电极处带上负载RL,它的信号会怎么样呢?

先看图:

当输入信号的最大值是400V的时候,输出信号只有0.976V,大约是2.5VPP,相比于之前求得的5VPP,输出信号变为了一半。从输出端口往里看(电路当成电压源),那么电路的输出阻抗就是10K,它与RL的阻抗分压,RL最终得到了2.5VPP原先的一半。

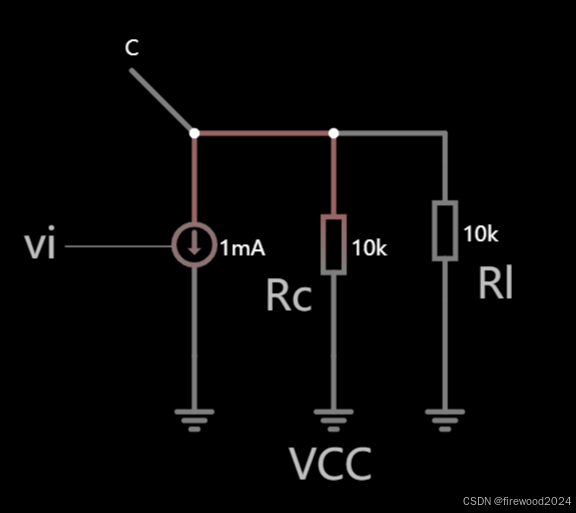

那么我们画出集电极处的交流通路,

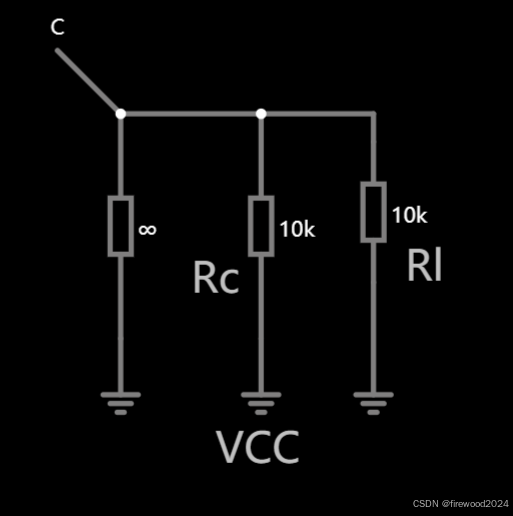

它的交流通路是这样的,左边是电流源因此它的等效电阻是无穷大,即有

因此RC与电流源电阻并联的阻抗就是RC本身。

因此RC与电流源电阻并联的阻抗就是RC本身。

- 这里理解的难点是为什么是电流源,并且这个电流源是和RC和RL并联的。

- 首先电路 有IE = IB +IC;由KCL得出。无论何时都是成立的,当输入信号产生一个小变动的时候,必然有 Δie +IE = IB + Δib + IC +Δic;

- 当Re确定后,那么有IE = (Vb -Vbe)/Re;显然IE也确定了,只要电路还工作在放大状态 ,IC就固定了,这是放大电路的特性,他会调整晶体管两端的电压,以至于在Rc变化的时候产生相同的IC电流。使得电路满足 IC = IE -IB;当环境变动不大工作稳定的时候。IB也是很稳定,因此IC电流就是恒定的。

- 我们可以完全模拟一下集电极出的电流情况,

- 这里理解难点情况是:交流电流可以从地GND 往集电极流,如上图的2号电流就是地往集电极流动。按理说C的的电势是一直大于0点电势的,它怎么能让电流从地往集电极流呢?这很不合理吧?你没有想错,但是你遗忘了一个器件耦合电容C,Vo端口接了一个耦合电容,当它稳定工作的时候,它两端的电压就是集电极的静态工作点的电压5V,这就是电流能够从地往集电极C流的原因。

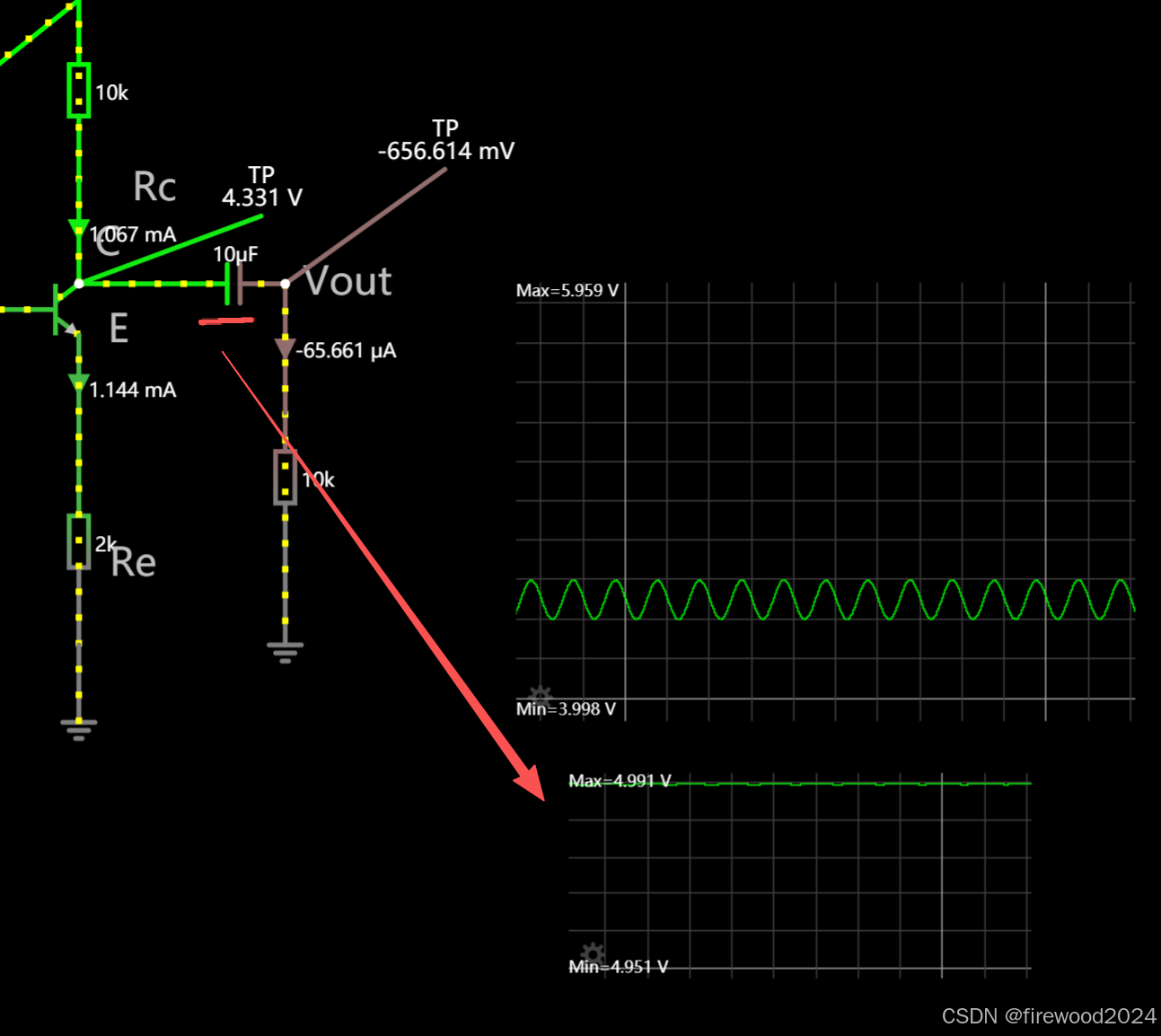

- 看下图

输出电容两端的电压保持在5V左右。

输出电容两端的电压保持在5V左右。- 知道这个结论,那么电流的分析情况就比较容易了,当VI(为正)有输入,那么必然会导致IC增大,该增大电流为Δic,因此集电极处的电流为: IC +Δ ic ;当Vo不接负载的时候,这个Δic就是VCC(15V)往集电极流,但是当Vo处接输出就有一部分交流电流Δic_RL是从GND流向集电极C。而VCC和GND都属于交流地,那么它们对集电极的电压差都是一样的,显然当RL与RC的电阻相同,它们能产生相同的电流1/2Δic.

- 那么这个不同路径1/2Δic会造成什么后果呢?显然它会使的流过Rc的电流变成IC+0.5Δic,因此由输入信号引起的压降变成原先的1/2即为Δvc,而RL上的电压是 -Δvc,电流是从GND流向C的,因此Vout的电压是低于GND的。而C点的电压由原先的VC - Δvc 变成 VC - 0.5vc,集电极的电压比之前上升。

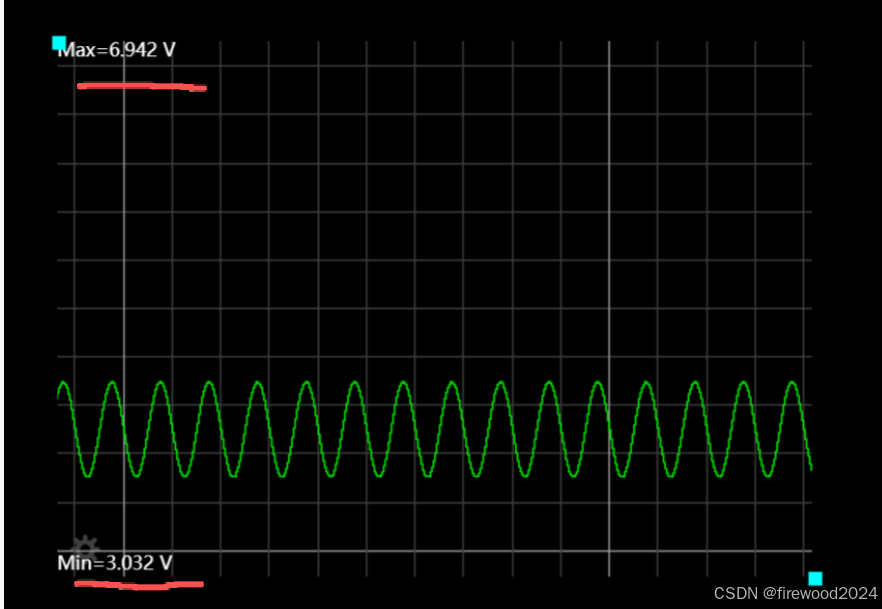

- 看一下未接输出的集电极电压范围:

- 它的范围是 3 ~ 7V 4vpp

- 接了10K RL电阻的时候它的电压范围是 4 ~6 V 2vpp

- 可以看到原先4VPP变成 2VPP了,最低电压从3V变成4V,提高了1伏是符合之前分析的。

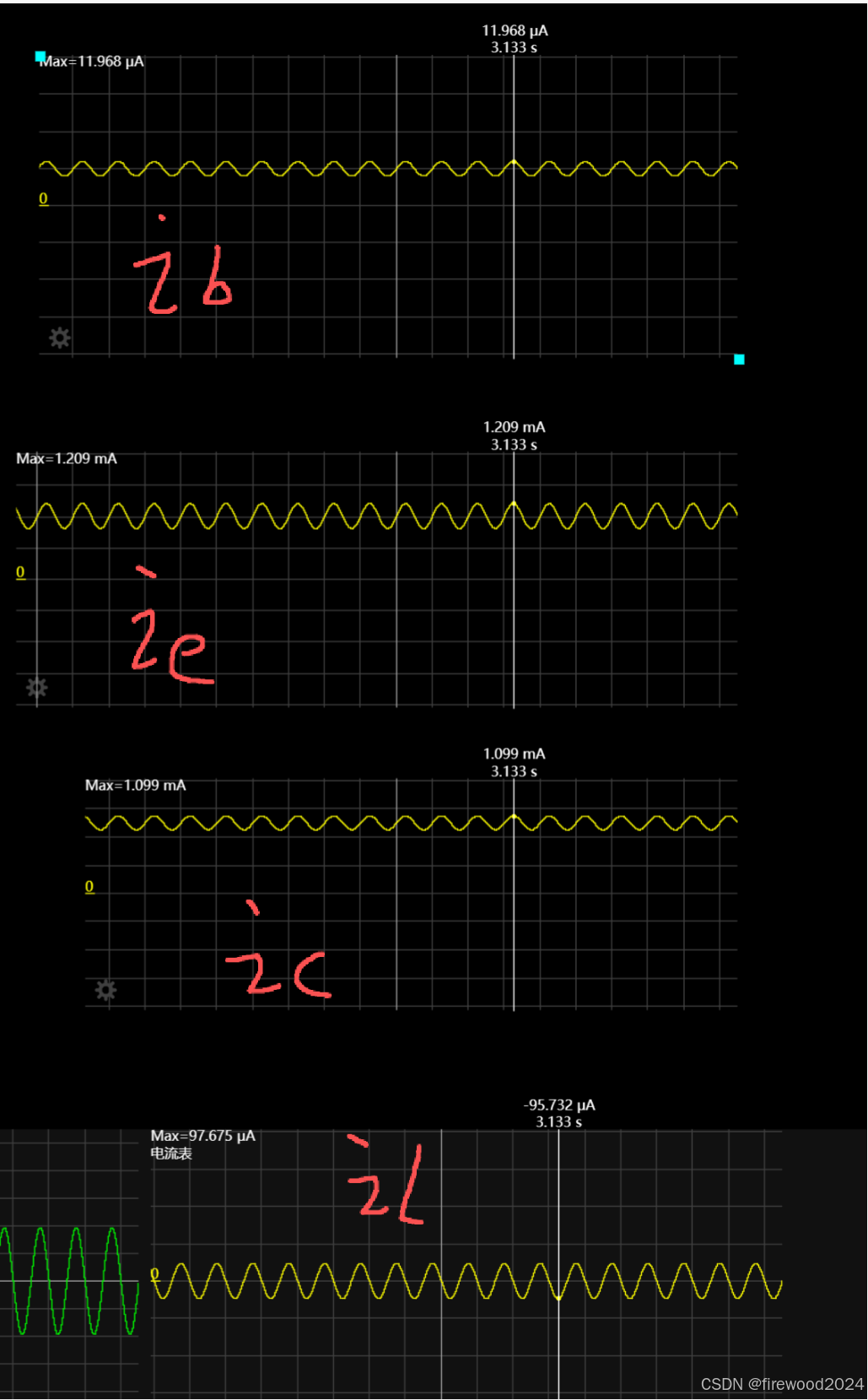

- 然后看一下仿真软件对这些电流的采样

- ie = ib + ic - il (解释一下这里为什么il是减法,因为都是流向节点C的电流,所以电流应该相加才对,但是与预设电流表设置的方向相反因此加个减号让它的电流变正)仿真的结果计算后差了几ua,应不影响结果。

第5个问题,怎么看待晶体管电路的输出阻抗

- 前文提到输出阻抗的计算的时候是采用用电压源方式计算的,当知道vo空载时候的输出,然后在外面接负载阻抗,通过测试RL上面的压降,来确定这个稳压电路的阻抗。即采用的是串联电阻分压。比如之前的RL/(RL+Rc) * 5VPP = 2.5VPP。

- 用恒流源的方式求解 即IC*Rc = 5Vpp; RL//RC = 5K 因此端口电压是 IC*RL//RC = 2.5vpp

- 发现两者求出的答案多少2.5VPP,当然也许你会猜测也是是恰好RL取值凑巧了。

- 那么我们任意去Rl的电阻是4K,用串联电阻分压法求:RL/(RL+Rc) * 5VPP = 2/7*5Vpp = 10/7Vpp;

- 然后用恒流源的方式求解,的RL//RC = 20K/7; IC = 5VPP/10K IC*RL//RC = 5VPP/10K*20K/7 = 10/7VPP; 结果是相同的。因此该晶体管电路的输出阻抗就是10K,无论你用哪种方式。

第6个问题,怎么看待三极管的密勒电容的问题以及它会造成什么后果

- 所谓密勒电容指的是三极管内部存在的寄生电容,这些电容因为三极管的特性,使得它的容值也相应的放大了这一特性,这种能放大的电容称为密勒电容。

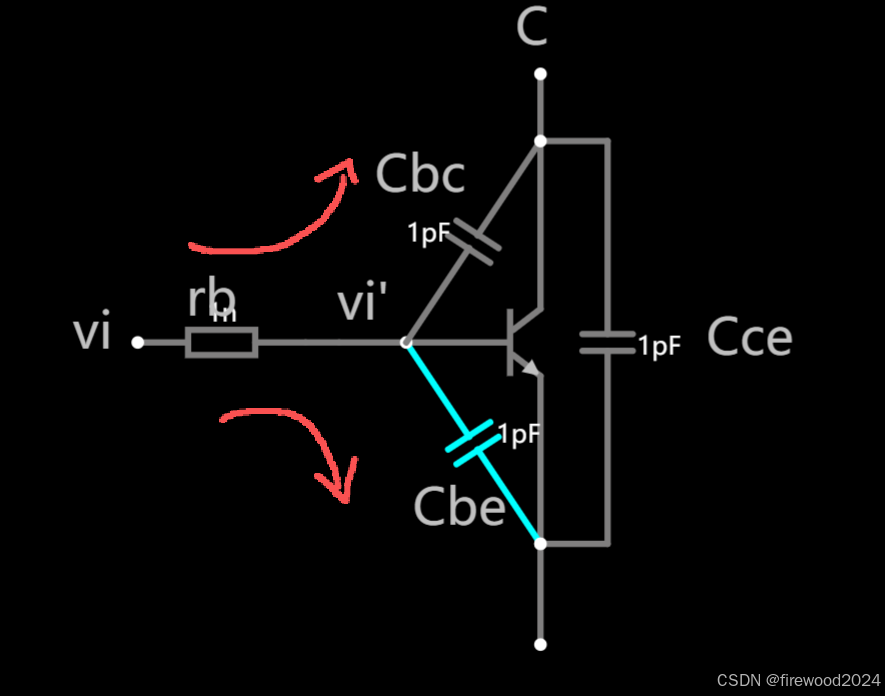

- 画一下它的寄生电容情况

- 先澄清一下这三个容值都是随便填的值,因为没有具体的数据。这里面主要有放大作用的是Cbc电容,rb是基极内部的寄生电阻。

- 先说说为什么要提这个电容,因为有人发现一个现象当输入信号的频率升高后,它的交流放大倍数会下降。比如对于三极管2SC2458这个三极管,对于本案5Au的放大电路,它的高频截止频率是3.98MHZ,而由手册得出的高频截止频率是80MHZ,显然实际测出的和手册给出的高频特性差距过大。造成这个原因就是Cbc这个电容被放大了。

- 显然由于考虑了寄生电容参数,vi的输入回路更加了,vi的负载加重了,它需要输出更多的电流或者灌入更多的电流才能够工作。显然集电极因此产生的的电压波动是 -vi*Au。前文关于Vo输出耦合电容的时候我们就提到过,类似这种耦合Cbc电容它在正常工作后,它的直流偏置电压是固定,应为它的存在,电流才会从"低电势"往高电势流而形成交流电。

- 我们来模拟下这个过程,当输入信号vi(为正),这时C端会产生 - vi' * Au的电压波动。我们知道电容的的电压是不能突变的 vi' + V_Cbc = VC > VC - vi' * Au ,这个时候电容就会往C极放电,最终电容就会放电,放掉的电荷是 Q = Cbc* Vi' * Au;

- 输入信号vi流经rb到达vi',这时vi'的电压就会升高那时VC的电流还没放大因此有 vi' +Cbc > VC,VC电压是恒定的,因此这个时候电容就要开始放电以达到电压相等,放掉的电荷是 Q' = Cbc * vi' ;最终在这两个过程中 电容Cbc一共放掉的电荷是 Q + Q' = (Au+1)Cbc * vi'

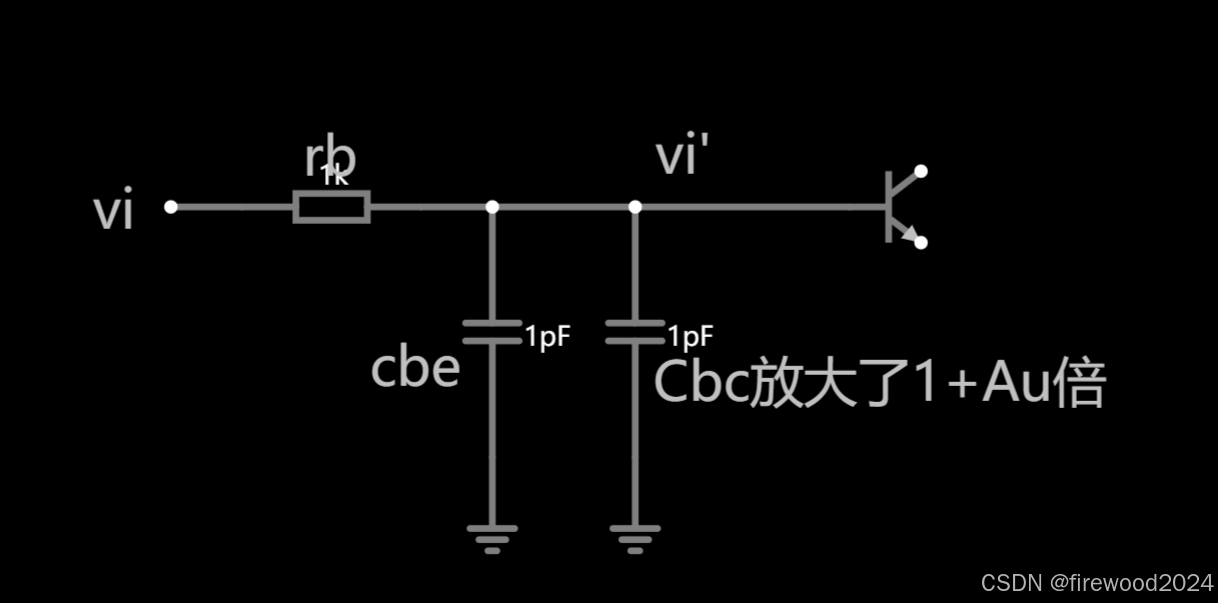

- 现在我们再讨论这个电容的时候是把它当做输入电容来考虑的,假设这个电容不存在放大作用,它两端的电压就应该和vi'一样 ,那么由公式 C = Q/U = (Au+1)Cbc * vi'/vi' = (Au+1)Cbc,就好似电容放大了1+Au倍。

- 看一下它的等效图

- 显然电阻rb和跨接接三极管不同两端的的电容构成低通滤波器,显然当频率高于某个频率ft的时候,vi'< 0.707vi,那么它的放大倍数自然会降低,因此它的高频特性也变差了。而电容并联的时候他的总容值是相加的即该低通滤波器的等效电容是 Cbc(1+Au) + Cbe;

- 这就是密勒电容造成的影响和后果。

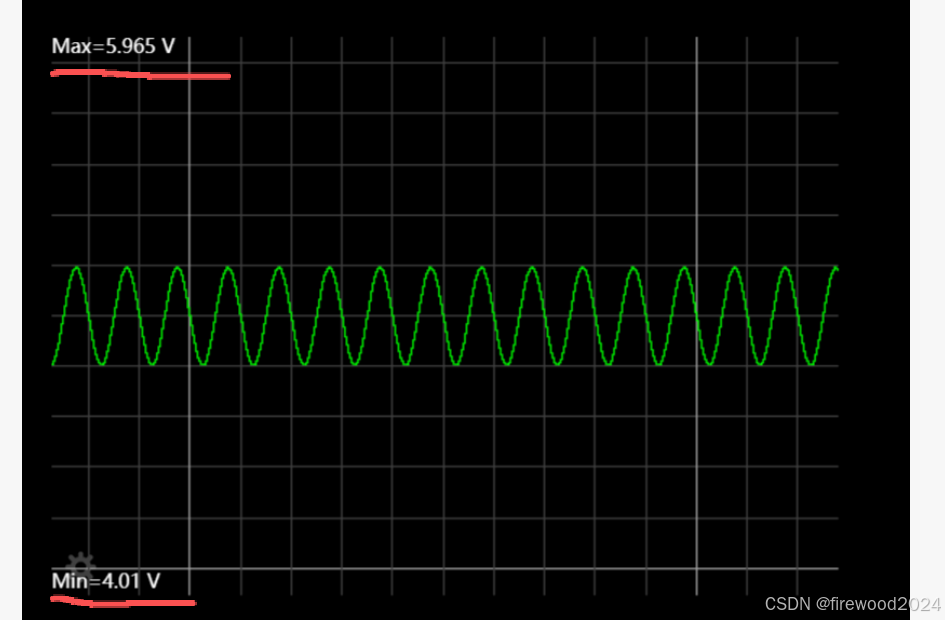

第7个问题是怎么看斩波情况的发生

- 当静态工作点设置不合理,那么输入信号的大小就会影响波形是否失真。看图:

当输入信号最大是500mv的时候,输出信号波形的下部分就好像有点被斩波了,为什么取这个值呢,因为电路的交流放大倍数是Au = 5,因此当输入信号最大是0.5V的时候,E端的电压是 2.5V,C即的电压是 5V - 0.5*5 = 2.5V,C端的电压都和E端相同了,现实情况下肯定波形下面被斩波了。

- 那么看一下不同输入信号下的波形情况

- 400MV的波形就比500MV的效果好一点了

- 600mv的可以明确的看到被斩波了。