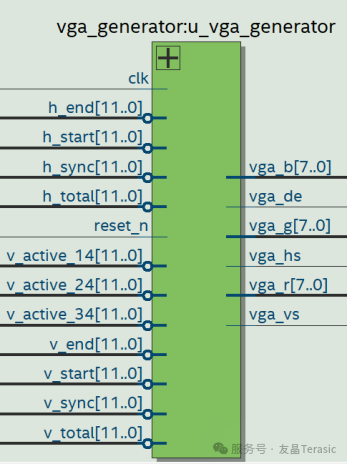

VGA显示控制器模块vga_generator.v(位于Demonstrations\FPGA\HDMI_TX\vpg_source路径下)可生成符合DMT(Display Monitor Timing 显示器时序)时序的视频信号。该模块的RTL Viewer视图如下:

该模块根据输入的时序参数生成VGA的行同步信号(vga_hs)、场同步信号(vga_vs)、数据有效信号(vga_de)以及24位真彩色(RGB888)数据(vga_r, vga_g, vga_b)。本案例利用该模块生成测试图案(彩条颜色渐变和边框)用于HDMI显示验证。

输入信号

clk:像素时钟PCLK输入。

reset_n:低电平有效的异步复位信号。

h_total:一行像素的总数(包括消隐区)。

h_sync:行同步脉冲的宽度(以像素数为单位)。

h_start:行有效数据开始的像素位置。

h_end:行有效数据结束的像素位置。

v_total:一帧的总行数(包括消隐区)。

v_sync:场同步脉冲的宽度(以行为单位)。

v_start:场有效数据开始的行位置。

v_end:场有效数据结束的行位置。

v_active_14,v_active_24, v_active_34:将像素有效显示区域分为4等分,每一部分显示一种颜色。

输出信号

vga_hs:行同步信号(低电平有效)。

vga_vs:场同步信号(低电平有效)。

vga_de:数据有效信号(高电平表示有效像素区域)。

vga_r,vga_g, vga_b:8位RGB颜色输出。

关键内部信号

h_count:水平像素计数器。

v_count:垂直行计数器。

pixel_x:当前行内的像素索引(用于颜色生成)。

h_act,v_act:行和场的有效区域标志。

color_mode:颜色模式控制信号(4位,分别代表4种颜色区域)。

boarder:边框标志(用于绘制白色边框)。

逻辑代码分析

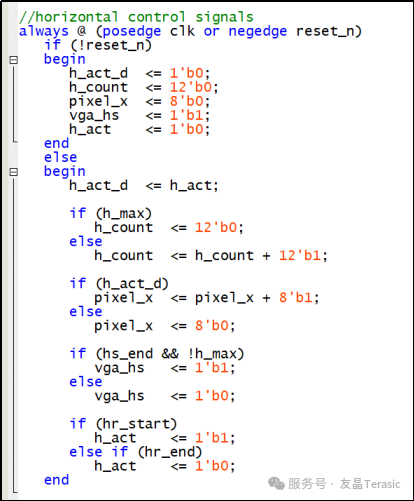

1.水平控制逻辑(Horizontal Control)

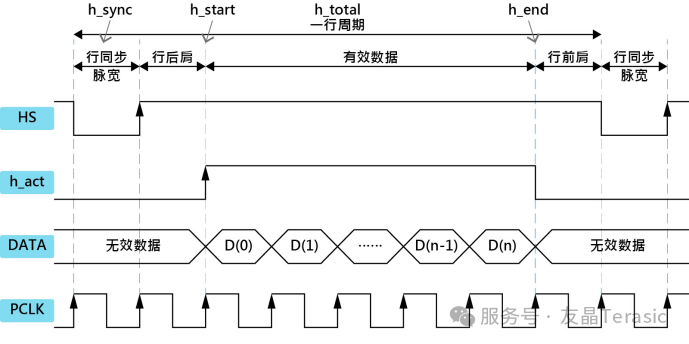

水平控制信号对应时序如下:

-

使用h_count计数像素位置,在达到h_total时归零。

-

生成行同步信号vga_hs:当h_count >= h_sync且未到行末时,同步信号为高(同步脉冲结束),否则为低(同步脉冲期间)。

-

控制行有效区域h_act:在h_start到h_end之间置位。

-

pixel_x在有效区域内递增,用于生成颜色渐变。

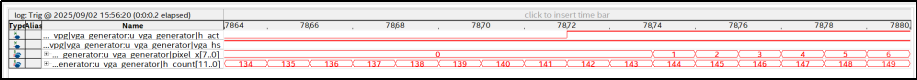

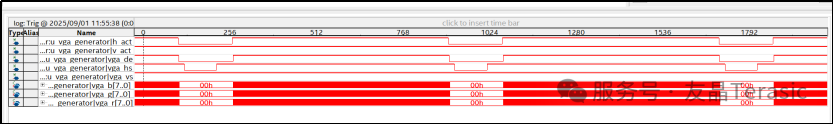

水平控制信号对应的Signaltap 波形如图,可见pixel_x信号比h_act信号延迟二拍。因为第 一拍h_act 变高,但 h_act_d 还是旧值(低电平);第二拍h_act 的高电平被锁存到 h_act_d 中,此时 h_act_d 变高电平,于是第三拍时pixel_x 值可以从0变1。

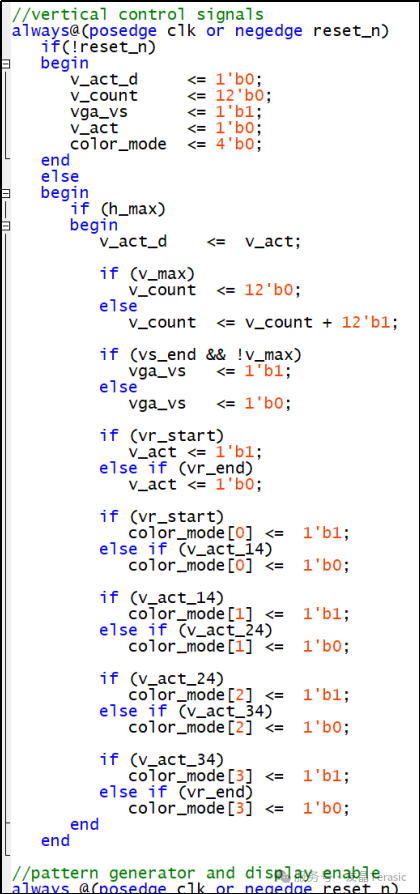

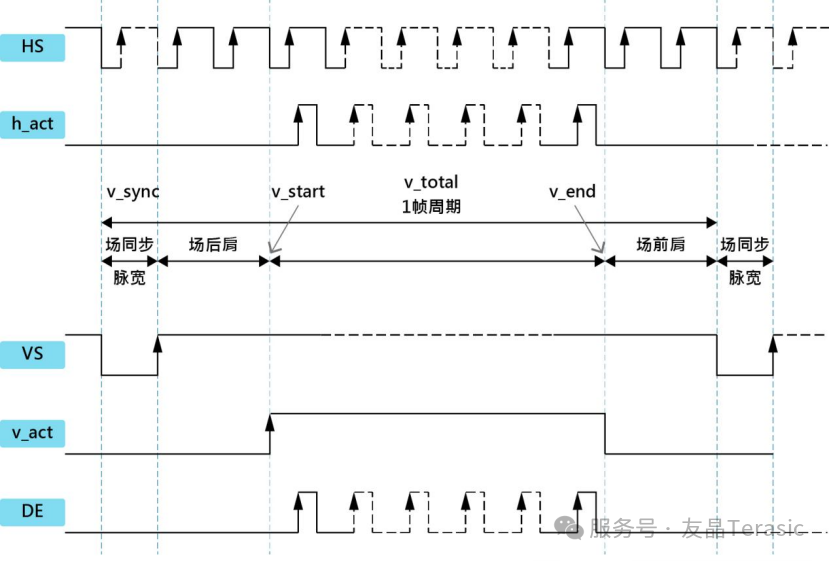

2.垂直控制逻辑(Vertical Control)

垂直控制信号对应时序如下:

-

在每行结束时(h_max为真)更新v_count。

-

生成场同步信号vga_vs:当v_count >= v_sync且未到帧末时,同步信号为高(同步脉冲结束),否则为低。

-

控制场有效区域v_act:在v_start到v_end之间置位。

-

根据垂直位置设置color_mode:v_active_14、v_active_24、v_active_34将有效区域分为4部分,分别对应不同的颜色模式。

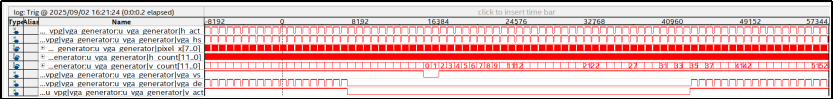

Signaltap 波形如下:

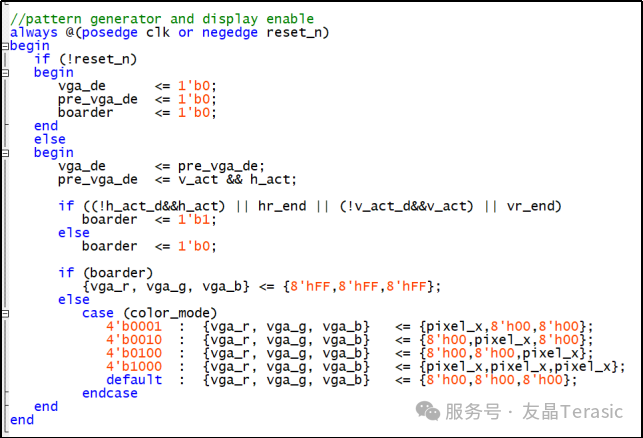

3.图像生成与数据有效(Pattern Generator and DE)

-

vga_de(数据有效)由pre_vga_de延迟一拍产生,pre_vga_de是h_act和v_act的逻辑与。

-

绘制白色边框:当进入或退出有效区域时(行或场的边界),boarder置位,输出白色(RGB=0xFF)。

-

在非边框区域,根据color_mode输出渐变颜色:

0001:由黑向红色渐变(红色分量随pixel_x递增)。

0010:由黑向绿色渐变。(绿色分量随pixel_x递增)。

0100:由黑向蓝色渐变。(蓝色分量随pixel_x递增)。

1000:由黑向白色渐变(三通道同时递增)。

默认状态:黑色(RGB=0x000000)。

Signaltap 波形如下:

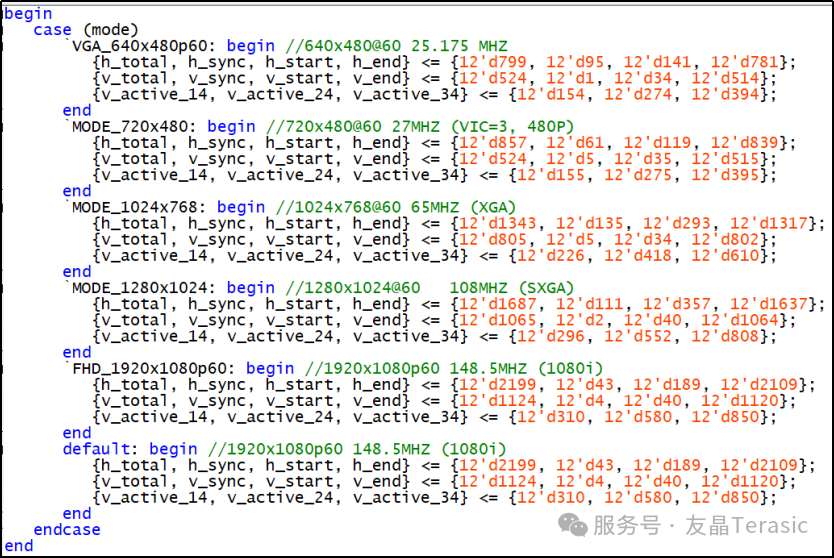

\Demonstrations\FPGA\HDMI_TX\vpg_source\vpg.v模块里面给出了各个分辨率参数:

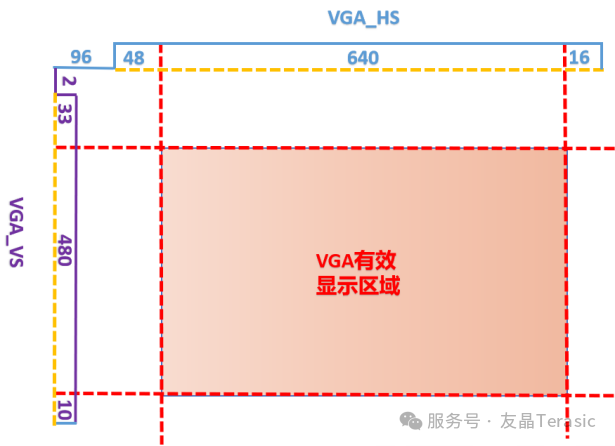

以上代码的这些参数数据参考1-DE10-Nano的HDMI方块移动案例------显示器时序(DMT)标准介绍 里面的显示器时序中不同分辨率刷新率的参数章节的表格。以640x480@60 为例,根据表格参数可以画出VGA有效显示区域如下:

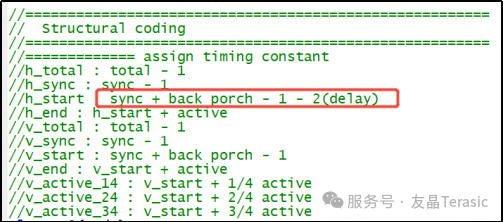

读者可能觉得vpg.v模块里面给出了各个分辨率参数跟表格的数据有不同,是因为时钟节拍从0开始计数,所以每个数据都减一, 另外h_start提前 2 拍其实是全局时序补偿,目标是抵消 "h_act信号到vga_de信号的总延迟(2 拍),让最终显示位置对齐 VGA 标准。具体的计算请参考vpg.v模块里面的注释部分:

往期阅读

1-DE10-Nano的HDMI方块移动案例------显示器时序(DMT)标准介绍

2-DE10-Nano的HDMI方块移动案例------HDMI接口介绍(含TMDS)

3-DE10-Nano的HDMI方块移动案例------ADV7513芯片解读

4-DE10-Nano的HDMI方块移动案例------I2C通信协议

5-DE10-Nano的HDMI方块移动案例------基于FPGA的I2C控制模块设计

6-DE10-Nano的HDMI方块移动案例------使用Modelsim仿真I2C控制器

7-DE10-Nano的HDMI方块移动案例的整体实现(含Quartus完整工程免费下载)