参考

axi_uartlite测试

AXI UART16550测试

官网ip文档

官网驱动设备树文档

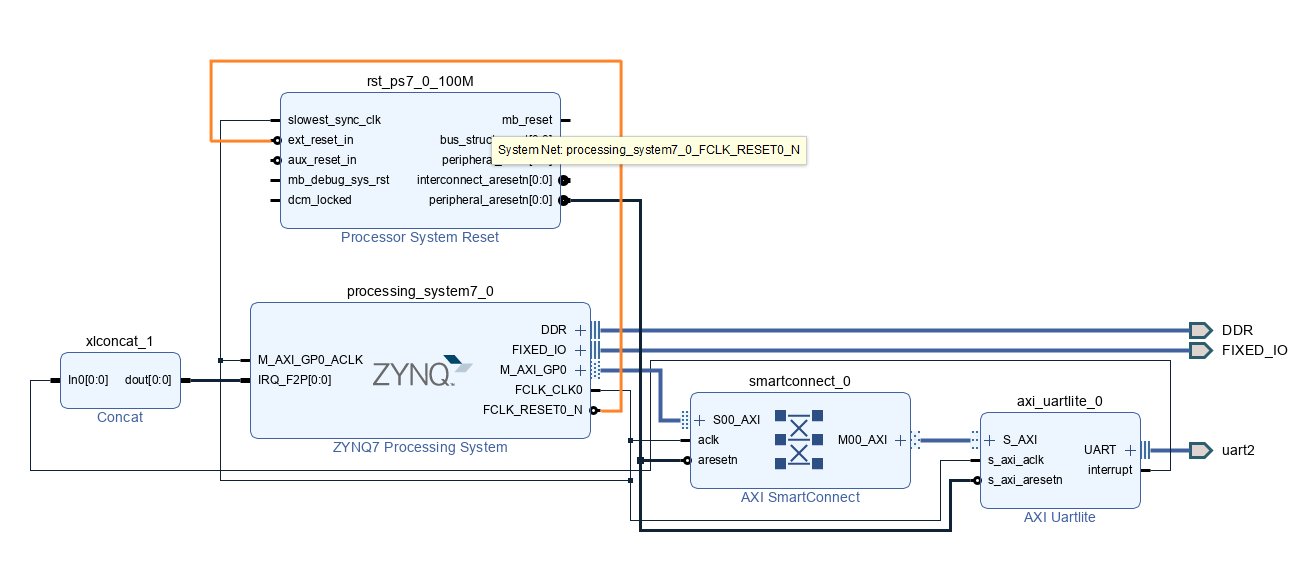

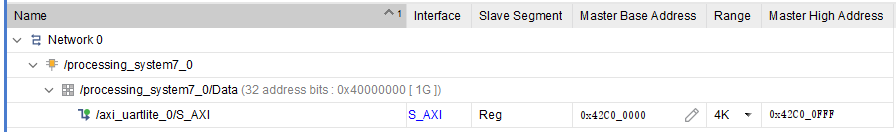

BD

bash

################################################################

# This is a generated script based on design: system

#

# Though there are limitations about the generated script,

# the main purpose of this utility is to make learning

# IP Integrator Tcl commands easier.

################################################################

namespace eval _tcl {

proc get_script_folder {} {

set script_path [file normalize [info script]]

set script_folder [file dirname $script_path]

return $script_folder

}

}

variable script_folder

set script_folder [_tcl::get_script_folder]

################################################################

# Check if script is running in correct Vivado version.

################################################################

set scripts_vivado_version 2020.2

set current_vivado_version [version -short]

if { [string first $scripts_vivado_version $current_vivado_version] == -1 } {

puts ""

catch {common::send_gid_msg -ssname BD::TCL -id 2041 -severity "ERROR" "This script was generated using Vivado <$scripts_vivado_version> and is being run in <$current_vivado_version> of Vivado. Please run the script in Vivado <$scripts_vivado_version> then open the design in Vivado <$current_vivado_version>. Upgrade the design by running \"Tools => Report => Report IP Status...\", then run write_bd_tcl to create an updated script."}

return 1

}

################################################################

# START

################################################################

# To test this script, run the following commands from Vivado Tcl console:

# source system_script.tcl

# If there is no project opened, this script will create a

# project, but make sure you do not have an existing project

# <./myproj/project_1.xpr> in the current working folder.

set list_projs [get_projects -quiet]

if { $list_projs eq "" } {

create_project project_1 myproj -part xc7z020clg400-2

}

# CHANGE DESIGN NAME HERE

variable design_name

set design_name system

# If you do not already have an existing IP Integrator design open,

# you can create a design using the following command:

# create_bd_design $design_name

# Creating design if needed

set errMsg ""

set nRet 0

set cur_design [current_bd_design -quiet]

set list_cells [get_bd_cells -quiet]

if { ${design_name} eq "" } {

# USE CASES:

# 1) Design_name not set

set errMsg "Please set the variable <design_name> to a non-empty value."

set nRet 1

} elseif { ${cur_design} ne "" && ${list_cells} eq "" } {

# USE CASES:

# 2): Current design opened AND is empty AND names same.

# 3): Current design opened AND is empty AND names diff; design_name NOT in project.

# 4): Current design opened AND is empty AND names diff; design_name exists in project.

if { $cur_design ne $design_name } {

common::send_gid_msg -ssname BD::TCL -id 2001 -severity "INFO" "Changing value of <design_name> from <$design_name> to <$cur_design> since current design is empty."

set design_name [get_property NAME $cur_design]

}

common::send_gid_msg -ssname BD::TCL -id 2002 -severity "INFO" "Constructing design in IPI design <$cur_design>..."

} elseif { ${cur_design} ne "" && $list_cells ne "" && $cur_design eq $design_name } {

# USE CASES:

# 5) Current design opened AND has components AND same names.

set errMsg "Design <$design_name> already exists in your project, please set the variable <design_name> to another value."

set nRet 1

} elseif { [get_files -quiet ${design_name}.bd] ne "" } {

# USE CASES:

# 6) Current opened design, has components, but diff names, design_name exists in project.

# 7) No opened design, design_name exists in project.

set errMsg "Design <$design_name> already exists in your project, please set the variable <design_name> to another value."

set nRet 2

} else {

# USE CASES:

# 8) No opened design, design_name not in project.

# 9) Current opened design, has components, but diff names, design_name not in project.

common::send_gid_msg -ssname BD::TCL -id 2003 -severity "INFO" "Currently there is no design <$design_name> in project, so creating one..."

create_bd_design $design_name

common::send_gid_msg -ssname BD::TCL -id 2004 -severity "INFO" "Making design <$design_name> as current_bd_design."

current_bd_design $design_name

}

common::send_gid_msg -ssname BD::TCL -id 2005 -severity "INFO" "Currently the variable <design_name> is equal to \"$design_name\"."

if { $nRet != 0 } {

catch {common::send_gid_msg -ssname BD::TCL -id 2006 -severity "ERROR" $errMsg}

return $nRet

}

set bCheckIPsPassed 1

##################################################################

# CHECK IPs

##################################################################

set bCheckIPs 1

if { $bCheckIPs == 1 } {

set list_check_ips "\

xilinx.com:ip:axi_uartlite:2.0\

xilinx.com:ip:processing_system7:5.5\

xilinx.com:ip:proc_sys_reset:5.0\

xilinx.com:ip:smartconnect:1.0\

xilinx.com:ip:xlconcat:2.1\

"

set list_ips_missing ""

common::send_gid_msg -ssname BD::TCL -id 2011 -severity "INFO" "Checking if the following IPs exist in the project's IP catalog: $list_check_ips ."

foreach ip_vlnv $list_check_ips {

set ip_obj [get_ipdefs -all $ip_vlnv]

if { $ip_obj eq "" } {

lappend list_ips_missing $ip_vlnv

}

}

if { $list_ips_missing ne "" } {

catch {common::send_gid_msg -ssname BD::TCL -id 2012 -severity "ERROR" "The following IPs are not found in the IP Catalog:\n $list_ips_missing\n\nResolution: Please add the repository containing the IP(s) to the project." }

set bCheckIPsPassed 0

}

}

if { $bCheckIPsPassed != 1 } {

common::send_gid_msg -ssname BD::TCL -id 2023 -severity "WARNING" "Will not continue with creation of design due to the error(s) above."

return 3

}

##################################################################

# DESIGN PROCs

##################################################################

# Procedure to create entire design; Provide argument to make

# procedure reusable. If parentCell is "", will use root.

proc create_root_design { parentCell } {

variable script_folder

variable design_name

if { $parentCell eq "" } {

set parentCell [get_bd_cells /]

}

# Get object for parentCell

set parentObj [get_bd_cells $parentCell]

if { $parentObj == "" } {

catch {common::send_gid_msg -ssname BD::TCL -id 2090 -severity "ERROR" "Unable to find parent cell <$parentCell>!"}

return

}

# Make sure parentObj is hier blk

set parentType [get_property TYPE $parentObj]

if { $parentType ne "hier" } {

catch {common::send_gid_msg -ssname BD::TCL -id 2091 -severity "ERROR" "Parent <$parentObj> has TYPE = <$parentType>. Expected to be <hier>."}

return

}

# Save current instance; Restore later

set oldCurInst [current_bd_instance .]

# Set parent object as current

current_bd_instance $parentObj

# Create interface ports

set DDR [ create_bd_intf_port -mode Master -vlnv xilinx.com:interface:ddrx_rtl:1.0 DDR ]

set FIXED_IO [ create_bd_intf_port -mode Master -vlnv xilinx.com:display_processing_system7:fixedio_rtl:1.0 FIXED_IO ]

set uart2 [ create_bd_intf_port -mode Master -vlnv xilinx.com:interface:uart_rtl:1.0 uart2 ]

# Create ports

# Create instance: axi_uartlite_0, and set properties

set axi_uartlite_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:axi_uartlite:2.0 axi_uartlite_0 ]

# Create instance: processing_system7_0, and set properties

set processing_system7_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:processing_system7:5.5 processing_system7_0 ]

set_property -dict [ list \

CONFIG.PCW_ACT_APU_PERIPHERAL_FREQMHZ {666.666687} \

CONFIG.PCW_ACT_CAN_PERIPHERAL_FREQMHZ {10.000000} \

CONFIG.PCW_ACT_DCI_PERIPHERAL_FREQMHZ {10.158730} \

CONFIG.PCW_ACT_ENET0_PERIPHERAL_FREQMHZ {125.000000} \

CONFIG.PCW_ACT_ENET1_PERIPHERAL_FREQMHZ {10.000000} \

CONFIG.PCW_ACT_FPGA0_PERIPHERAL_FREQMHZ {100.000000} \

CONFIG.PCW_ACT_FPGA1_PERIPHERAL_FREQMHZ {10.000000} \

CONFIG.PCW_ACT_FPGA2_PERIPHERAL_FREQMHZ {10.000000} \

CONFIG.PCW_ACT_FPGA3_PERIPHERAL_FREQMHZ {10.000000} \

CONFIG.PCW_ACT_PCAP_PERIPHERAL_FREQMHZ {200.000000} \

CONFIG.PCW_ACT_QSPI_PERIPHERAL_FREQMHZ {200.000000} \

CONFIG.PCW_ACT_SDIO_PERIPHERAL_FREQMHZ {100.000000} \

CONFIG.PCW_ACT_SMC_PERIPHERAL_FREQMHZ {10.000000} \

CONFIG.PCW_ACT_SPI_PERIPHERAL_FREQMHZ {10.000000} \

CONFIG.PCW_ACT_TPIU_PERIPHERAL_FREQMHZ {200.000000} \

CONFIG.PCW_ACT_TTC0_CLK0_PERIPHERAL_FREQMHZ {111.111115} \

CONFIG.PCW_ACT_TTC0_CLK1_PERIPHERAL_FREQMHZ {111.111115} \

CONFIG.PCW_ACT_TTC0_CLK2_PERIPHERAL_FREQMHZ {111.111115} \

CONFIG.PCW_ACT_TTC1_CLK0_PERIPHERAL_FREQMHZ {111.111115} \

CONFIG.PCW_ACT_TTC1_CLK1_PERIPHERAL_FREQMHZ {111.111115} \

CONFIG.PCW_ACT_TTC1_CLK2_PERIPHERAL_FREQMHZ {111.111115} \

CONFIG.PCW_ACT_UART_PERIPHERAL_FREQMHZ {100.000000} \

CONFIG.PCW_ACT_WDT_PERIPHERAL_FREQMHZ {111.111115} \

CONFIG.PCW_ARMPLL_CTRL_FBDIV {40} \

CONFIG.PCW_CAN_PERIPHERAL_DIVISOR0 {1} \

CONFIG.PCW_CAN_PERIPHERAL_DIVISOR1 {1} \

CONFIG.PCW_CLK0_FREQ {100000000} \

CONFIG.PCW_CLK1_FREQ {10000000} \

CONFIG.PCW_CLK2_FREQ {10000000} \

CONFIG.PCW_CLK3_FREQ {10000000} \

CONFIG.PCW_CPU_CPU_PLL_FREQMHZ {1333.333} \

CONFIG.PCW_CPU_PERIPHERAL_DIVISOR0 {2} \

CONFIG.PCW_CRYSTAL_PERIPHERAL_FREQMHZ {33.33333333333333333333333} \

CONFIG.PCW_DCI_PERIPHERAL_DIVISOR0 {15} \

CONFIG.PCW_DCI_PERIPHERAL_DIVISOR1 {7} \

CONFIG.PCW_DDRPLL_CTRL_FBDIV {32} \

CONFIG.PCW_DDR_DDR_PLL_FREQMHZ {1066.667} \

CONFIG.PCW_DDR_PERIPHERAL_DIVISOR0 {2} \

CONFIG.PCW_DDR_RAM_HIGHADDR {0x3FFFFFFF} \

CONFIG.PCW_ENET0_ENET0_IO {MIO 16 .. 27} \

CONFIG.PCW_ENET0_GRP_MDIO_ENABLE {1} \

CONFIG.PCW_ENET0_GRP_MDIO_IO {MIO 52 .. 53} \

CONFIG.PCW_ENET0_PERIPHERAL_CLKSRC {IO PLL} \

CONFIG.PCW_ENET0_PERIPHERAL_DIVISOR0 {8} \

CONFIG.PCW_ENET0_PERIPHERAL_DIVISOR1 {1} \

CONFIG.PCW_ENET0_PERIPHERAL_ENABLE {1} \

CONFIG.PCW_ENET0_PERIPHERAL_FREQMHZ {1000 Mbps} \

CONFIG.PCW_ENET0_RESET_ENABLE {0} \

CONFIG.PCW_ENET1_PERIPHERAL_DIVISOR0 {1} \

CONFIG.PCW_ENET1_PERIPHERAL_DIVISOR1 {1} \

CONFIG.PCW_ENET1_RESET_ENABLE {0} \

CONFIG.PCW_ENET_RESET_ENABLE {0} \

CONFIG.PCW_EN_CLK0_PORT {1} \

CONFIG.PCW_EN_EMIO_CD_SDIO0 {0} \

CONFIG.PCW_EN_EMIO_CD_SDIO1 {0} \

CONFIG.PCW_EN_EMIO_ENET0 {0} \

CONFIG.PCW_EN_EMIO_GPIO {0} \

CONFIG.PCW_EN_EMIO_I2C0 {0} \

CONFIG.PCW_EN_EMIO_I2C1 {0} \

CONFIG.PCW_EN_EMIO_SDIO1 {0} \

CONFIG.PCW_EN_EMIO_UART0 {0} \

CONFIG.PCW_EN_EMIO_UART1 {0} \

CONFIG.PCW_EN_EMIO_WP_SDIO1 {0} \

CONFIG.PCW_EN_ENET0 {1} \

CONFIG.PCW_EN_GPIO {0} \

CONFIG.PCW_EN_I2C0 {0} \

CONFIG.PCW_EN_I2C1 {0} \

CONFIG.PCW_EN_QSPI {1} \

CONFIG.PCW_EN_SDIO0 {1} \

CONFIG.PCW_EN_SDIO1 {1} \

CONFIG.PCW_EN_UART0 {1} \

CONFIG.PCW_EN_UART1 {0} \

CONFIG.PCW_EN_USB0 {0} \

CONFIG.PCW_FCLK0_PERIPHERAL_DIVISOR0 {5} \

CONFIG.PCW_FCLK0_PERIPHERAL_DIVISOR1 {2} \

CONFIG.PCW_FCLK1_PERIPHERAL_DIVISOR0 {1} \

CONFIG.PCW_FCLK1_PERIPHERAL_DIVISOR1 {1} \

CONFIG.PCW_FCLK2_PERIPHERAL_DIVISOR0 {1} \

CONFIG.PCW_FCLK2_PERIPHERAL_DIVISOR1 {1} \

CONFIG.PCW_FCLK3_PERIPHERAL_DIVISOR0 {1} \

CONFIG.PCW_FCLK3_PERIPHERAL_DIVISOR1 {1} \

CONFIG.PCW_FCLK_CLK0_BUF {FALSE} \

CONFIG.PCW_FPGA0_PERIPHERAL_FREQMHZ {100} \

CONFIG.PCW_FPGA_FCLK0_ENABLE {1} \

CONFIG.PCW_FPGA_FCLK1_ENABLE {0} \

CONFIG.PCW_FPGA_FCLK2_ENABLE {0} \

CONFIG.PCW_FPGA_FCLK3_ENABLE {0} \

CONFIG.PCW_GPIO_EMIO_GPIO_ENABLE {0} \

CONFIG.PCW_GPIO_EMIO_GPIO_IO {<Select>} \

CONFIG.PCW_GPIO_EMIO_GPIO_WIDTH {64} \

CONFIG.PCW_GPIO_MIO_GPIO_ENABLE {0} \

CONFIG.PCW_GPIO_MIO_GPIO_IO {<Select>} \

CONFIG.PCW_I2C0_GRP_INT_ENABLE {0} \

CONFIG.PCW_I2C0_GRP_INT_IO {<Select>} \

CONFIG.PCW_I2C0_I2C0_IO {<Select>} \

CONFIG.PCW_I2C0_PERIPHERAL_ENABLE {0} \

CONFIG.PCW_I2C0_RESET_ENABLE {0} \

CONFIG.PCW_I2C1_GRP_INT_ENABLE {0} \

CONFIG.PCW_I2C1_GRP_INT_IO {<Select>} \

CONFIG.PCW_I2C1_I2C1_IO {<Select>} \

CONFIG.PCW_I2C1_PERIPHERAL_ENABLE {0} \

CONFIG.PCW_I2C1_RESET_ENABLE {0} \

CONFIG.PCW_I2C_PERIPHERAL_FREQMHZ {25} \

CONFIG.PCW_I2C_RESET_ENABLE {0} \

CONFIG.PCW_IOPLL_CTRL_FBDIV {30} \

CONFIG.PCW_IO_IO_PLL_FREQMHZ {1000.000} \

CONFIG.PCW_IRQ_F2P_INTR {1} \

CONFIG.PCW_MIO_0_DIRECTION {<Select>} \

CONFIG.PCW_MIO_0_IOTYPE {<Select>} \

CONFIG.PCW_MIO_0_PULLUP {<Select>} \

CONFIG.PCW_MIO_0_SLEW {<Select>} \

CONFIG.PCW_MIO_10_DIRECTION {in} \

CONFIG.PCW_MIO_10_IOTYPE {LVCMOS 3.3V} \

CONFIG.PCW_MIO_10_PULLUP {enabled} \

CONFIG.PCW_MIO_10_SLEW {slow} \

CONFIG.PCW_MIO_11_DIRECTION {<Select>} \

CONFIG.PCW_MIO_11_IOTYPE {<Select>} \

CONFIG.PCW_MIO_11_PULLUP {<Select>} \

CONFIG.PCW_MIO_11_SLEW {<Select>} \

CONFIG.PCW_MIO_12_DIRECTION {<Select>} \

CONFIG.PCW_MIO_12_IOTYPE {<Select>} \

CONFIG.PCW_MIO_12_PULLUP {<Select>} \

CONFIG.PCW_MIO_12_SLEW {<Select>} \

CONFIG.PCW_MIO_13_DIRECTION {<Select>} \

CONFIG.PCW_MIO_13_IOTYPE {<Select>} \

CONFIG.PCW_MIO_13_PULLUP {<Select>} \

CONFIG.PCW_MIO_13_SLEW {<Select>} \

CONFIG.PCW_MIO_14_DIRECTION {in} \

CONFIG.PCW_MIO_14_IOTYPE {LVCMOS 3.3V} \

CONFIG.PCW_MIO_14_PULLUP {enabled} \

CONFIG.PCW_MIO_14_SLEW {slow} \

CONFIG.PCW_MIO_15_DIRECTION {out} \

CONFIG.PCW_MIO_15_IOTYPE {LVCMOS 3.3V} \

CONFIG.PCW_MIO_15_PULLUP {enabled} \

CONFIG.PCW_MIO_15_SLEW {slow} \

CONFIG.PCW_MIO_16_DIRECTION {out} \

CONFIG.PCW_MIO_16_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_16_PULLUP {enabled} \

CONFIG.PCW_MIO_16_SLEW {slow} \

CONFIG.PCW_MIO_17_DIRECTION {out} \

CONFIG.PCW_MIO_17_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_17_PULLUP {enabled} \

CONFIG.PCW_MIO_17_SLEW {slow} \

CONFIG.PCW_MIO_18_DIRECTION {out} \

CONFIG.PCW_MIO_18_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_18_PULLUP {enabled} \

CONFIG.PCW_MIO_18_SLEW {slow} \

CONFIG.PCW_MIO_19_DIRECTION {out} \

CONFIG.PCW_MIO_19_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_19_PULLUP {enabled} \

CONFIG.PCW_MIO_19_SLEW {slow} \

CONFIG.PCW_MIO_1_DIRECTION {out} \

CONFIG.PCW_MIO_1_IOTYPE {LVCMOS 3.3V} \

CONFIG.PCW_MIO_1_PULLUP {enabled} \

CONFIG.PCW_MIO_1_SLEW {slow} \

CONFIG.PCW_MIO_20_DIRECTION {out} \

CONFIG.PCW_MIO_20_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_20_PULLUP {enabled} \

CONFIG.PCW_MIO_20_SLEW {slow} \

CONFIG.PCW_MIO_21_DIRECTION {out} \

CONFIG.PCW_MIO_21_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_21_PULLUP {enabled} \

CONFIG.PCW_MIO_21_SLEW {slow} \

CONFIG.PCW_MIO_22_DIRECTION {in} \

CONFIG.PCW_MIO_22_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_22_PULLUP {enabled} \

CONFIG.PCW_MIO_22_SLEW {slow} \

CONFIG.PCW_MIO_23_DIRECTION {in} \

CONFIG.PCW_MIO_23_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_23_PULLUP {enabled} \

CONFIG.PCW_MIO_23_SLEW {slow} \

CONFIG.PCW_MIO_24_DIRECTION {in} \

CONFIG.PCW_MIO_24_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_24_PULLUP {enabled} \

CONFIG.PCW_MIO_24_SLEW {slow} \

CONFIG.PCW_MIO_25_DIRECTION {in} \

CONFIG.PCW_MIO_25_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_25_PULLUP {enabled} \

CONFIG.PCW_MIO_25_SLEW {slow} \

CONFIG.PCW_MIO_26_DIRECTION {in} \

CONFIG.PCW_MIO_26_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_26_PULLUP {enabled} \

CONFIG.PCW_MIO_26_SLEW {slow} \

CONFIG.PCW_MIO_27_DIRECTION {in} \

CONFIG.PCW_MIO_27_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_27_PULLUP {enabled} \

CONFIG.PCW_MIO_27_SLEW {slow} \

CONFIG.PCW_MIO_28_DIRECTION {inout} \

CONFIG.PCW_MIO_28_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_28_PULLUP {enabled} \

CONFIG.PCW_MIO_28_SLEW {slow} \

CONFIG.PCW_MIO_29_DIRECTION {in} \

CONFIG.PCW_MIO_29_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_29_PULLUP {enabled} \

CONFIG.PCW_MIO_29_SLEW {slow} \

CONFIG.PCW_MIO_2_DIRECTION {inout} \

CONFIG.PCW_MIO_2_IOTYPE {LVCMOS 3.3V} \

CONFIG.PCW_MIO_2_PULLUP {disabled} \

CONFIG.PCW_MIO_2_SLEW {slow} \

CONFIG.PCW_MIO_30_DIRECTION {out} \

CONFIG.PCW_MIO_30_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_30_PULLUP {enabled} \

CONFIG.PCW_MIO_30_SLEW {slow} \

CONFIG.PCW_MIO_31_DIRECTION {in} \

CONFIG.PCW_MIO_31_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_31_PULLUP {enabled} \

CONFIG.PCW_MIO_31_SLEW {slow} \

CONFIG.PCW_MIO_32_DIRECTION {inout} \

CONFIG.PCW_MIO_32_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_32_PULLUP {enabled} \

CONFIG.PCW_MIO_32_SLEW {slow} \

CONFIG.PCW_MIO_33_DIRECTION {inout} \

CONFIG.PCW_MIO_33_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_33_PULLUP {enabled} \

CONFIG.PCW_MIO_33_SLEW {slow} \

CONFIG.PCW_MIO_34_DIRECTION {inout} \

CONFIG.PCW_MIO_34_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_34_PULLUP {enabled} \

CONFIG.PCW_MIO_34_SLEW {slow} \

CONFIG.PCW_MIO_35_DIRECTION {inout} \

CONFIG.PCW_MIO_35_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_35_PULLUP {enabled} \

CONFIG.PCW_MIO_35_SLEW {slow} \

CONFIG.PCW_MIO_36_DIRECTION {in} \

CONFIG.PCW_MIO_36_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_36_PULLUP {enabled} \

CONFIG.PCW_MIO_36_SLEW {slow} \

CONFIG.PCW_MIO_37_DIRECTION {inout} \

CONFIG.PCW_MIO_37_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_37_PULLUP {enabled} \

CONFIG.PCW_MIO_37_SLEW {slow} \

CONFIG.PCW_MIO_38_DIRECTION {inout} \

CONFIG.PCW_MIO_38_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_38_PULLUP {enabled} \

CONFIG.PCW_MIO_38_SLEW {slow} \

CONFIG.PCW_MIO_39_DIRECTION {inout} \

CONFIG.PCW_MIO_39_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_39_PULLUP {enabled} \

CONFIG.PCW_MIO_39_SLEW {slow} \

CONFIG.PCW_MIO_3_DIRECTION {inout} \

CONFIG.PCW_MIO_3_IOTYPE {LVCMOS 3.3V} \

CONFIG.PCW_MIO_3_PULLUP {disabled} \

CONFIG.PCW_MIO_3_SLEW {slow} \

CONFIG.PCW_MIO_40_DIRECTION {inout} \

CONFIG.PCW_MIO_40_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_40_PULLUP {enabled} \

CONFIG.PCW_MIO_40_SLEW {slow} \

CONFIG.PCW_MIO_41_DIRECTION {inout} \

CONFIG.PCW_MIO_41_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_41_PULLUP {enabled} \

CONFIG.PCW_MIO_41_SLEW {slow} \

CONFIG.PCW_MIO_42_DIRECTION {inout} \

CONFIG.PCW_MIO_42_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_42_PULLUP {enabled} \

CONFIG.PCW_MIO_42_SLEW {slow} \

CONFIG.PCW_MIO_43_DIRECTION {inout} \

CONFIG.PCW_MIO_43_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_43_PULLUP {enabled} \

CONFIG.PCW_MIO_43_SLEW {slow} \

CONFIG.PCW_MIO_44_DIRECTION {inout} \

CONFIG.PCW_MIO_44_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_44_PULLUP {enabled} \

CONFIG.PCW_MIO_44_SLEW {slow} \

CONFIG.PCW_MIO_45_DIRECTION {inout} \

CONFIG.PCW_MIO_45_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_45_PULLUP {enabled} \

CONFIG.PCW_MIO_45_SLEW {slow} \

CONFIG.PCW_MIO_46_DIRECTION {inout} \

CONFIG.PCW_MIO_46_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_46_PULLUP {enabled} \

CONFIG.PCW_MIO_46_SLEW {slow} \

CONFIG.PCW_MIO_47_DIRECTION {inout} \

CONFIG.PCW_MIO_47_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_47_PULLUP {enabled} \

CONFIG.PCW_MIO_47_SLEW {slow} \

CONFIG.PCW_MIO_48_DIRECTION {inout} \

CONFIG.PCW_MIO_48_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_48_PULLUP {enabled} \

CONFIG.PCW_MIO_48_SLEW {slow} \

CONFIG.PCW_MIO_49_DIRECTION {inout} \

CONFIG.PCW_MIO_49_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_49_PULLUP {enabled} \

CONFIG.PCW_MIO_49_SLEW {slow} \

CONFIG.PCW_MIO_4_DIRECTION {inout} \

CONFIG.PCW_MIO_4_IOTYPE {LVCMOS 3.3V} \

CONFIG.PCW_MIO_4_PULLUP {disabled} \

CONFIG.PCW_MIO_4_SLEW {slow} \

CONFIG.PCW_MIO_50_DIRECTION {inout} \

CONFIG.PCW_MIO_50_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_50_PULLUP {enabled} \

CONFIG.PCW_MIO_50_SLEW {slow} \

CONFIG.PCW_MIO_51_DIRECTION {inout} \

CONFIG.PCW_MIO_51_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_51_PULLUP {enabled} \

CONFIG.PCW_MIO_51_SLEW {slow} \

CONFIG.PCW_MIO_52_DIRECTION {out} \

CONFIG.PCW_MIO_52_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_52_PULLUP {enabled} \

CONFIG.PCW_MIO_52_SLEW {slow} \

CONFIG.PCW_MIO_53_DIRECTION {inout} \

CONFIG.PCW_MIO_53_IOTYPE {LVCMOS 1.8V} \

CONFIG.PCW_MIO_53_PULLUP {enabled} \

CONFIG.PCW_MIO_53_SLEW {slow} \

CONFIG.PCW_MIO_5_DIRECTION {inout} \

CONFIG.PCW_MIO_5_IOTYPE {LVCMOS 3.3V} \

CONFIG.PCW_MIO_5_PULLUP {disabled} \

CONFIG.PCW_MIO_5_SLEW {slow} \

CONFIG.PCW_MIO_6_DIRECTION {out} \

CONFIG.PCW_MIO_6_IOTYPE {LVCMOS 3.3V} \

CONFIG.PCW_MIO_6_PULLUP {disabled} \

CONFIG.PCW_MIO_6_SLEW {slow} \

CONFIG.PCW_MIO_7_DIRECTION {<Select>} \

CONFIG.PCW_MIO_7_IOTYPE {<Select>} \

CONFIG.PCW_MIO_7_PULLUP {<Select>} \

CONFIG.PCW_MIO_7_SLEW {<Select>} \

CONFIG.PCW_MIO_8_DIRECTION {<Select>} \

CONFIG.PCW_MIO_8_IOTYPE {<Select>} \

CONFIG.PCW_MIO_8_PULLUP {<Select>} \

CONFIG.PCW_MIO_8_SLEW {<Select>} \

CONFIG.PCW_MIO_9_DIRECTION {<Select>} \

CONFIG.PCW_MIO_9_IOTYPE {<Select>} \

CONFIG.PCW_MIO_9_PULLUP {<Select>} \

CONFIG.PCW_MIO_9_SLEW {<Select>} \

CONFIG.PCW_MIO_TREE_PERIPHERALS { \

0#Enet 0 \

0#Enet 0 \

0#Enet 0 \

0#Enet 0 \

0#Enet 0 \

0#Enet 0 \

0#Enet 0 \

0#SD 0#SD \

0#SD 0#SD \

0#SD 0#SD \

0#UART 0#Enet \

1#SD 1#Enet \

1#SD 1#Enet \

1#SD 1#Enet \

Flash#Quad SPI \

Flash#Quad SPI \

Flash#Quad SPI \

Flash#Quad SPI \

Flash#Quad SPI \

Flash#unassigned#unassigned#unassigned#SD 0#unassigned#unassigned#unassigned#UART \

unassigned#Quad SPI \

} \

CONFIG.PCW_MIO_TREE_SIGNALS {unassigned#qspi0_ss_b#qspi0_io[0]#qspi0_io[1]#qspi0_io[2]#qspi0_io[3]/HOLD_B#qspi0_sclk#unassigned#unassigned#unassigned#cd#unassigned#unassigned#unassigned#rx#tx#tx_clk#txd[0]#txd[1]#txd[2]#txd[3]#tx_ctl#rx_clk#rxd[0]#rxd[1]#rxd[2]#rxd[3]#rx_ctl#unassigned#unassigned#unassigned#unassigned#unassigned#unassigned#unassigned#unassigned#unassigned#unassigned#unassigned#unassigned#clk#cmd#data[0]#data[1]#data[2]#data[3]#data[0]#cmd#clk#data[1]#data[2]#data[3]#mdc#mdio} \

CONFIG.PCW_NAND_GRP_D8_ENABLE {0} \

CONFIG.PCW_NAND_PERIPHERAL_ENABLE {0} \

CONFIG.PCW_NOR_GRP_A25_ENABLE {0} \

CONFIG.PCW_NOR_GRP_CS0_ENABLE {0} \

CONFIG.PCW_NOR_GRP_CS1_ENABLE {0} \

CONFIG.PCW_NOR_GRP_SRAM_CS0_ENABLE {0} \

CONFIG.PCW_NOR_GRP_SRAM_CS1_ENABLE {0} \

CONFIG.PCW_NOR_GRP_SRAM_INT_ENABLE {0} \

CONFIG.PCW_NOR_PERIPHERAL_ENABLE {0} \

CONFIG.PCW_PCAP_PERIPHERAL_DIVISOR0 {5} \

CONFIG.PCW_PRESET_BANK1_VOLTAGE {LVCMOS 1.8V} \

CONFIG.PCW_QSPI_GRP_FBCLK_ENABLE {0} \

CONFIG.PCW_QSPI_GRP_IO1_ENABLE {0} \

CONFIG.PCW_QSPI_GRP_SINGLE_SS_ENABLE {1} \

CONFIG.PCW_QSPI_GRP_SINGLE_SS_IO {MIO 1 .. 6} \

CONFIG.PCW_QSPI_GRP_SS1_ENABLE {0} \

CONFIG.PCW_QSPI_PERIPHERAL_DIVISOR0 {5} \

CONFIG.PCW_QSPI_PERIPHERAL_ENABLE {1} \

CONFIG.PCW_QSPI_PERIPHERAL_FREQMHZ {200} \

CONFIG.PCW_QSPI_QSPI_IO {MIO 1 .. 6} \

CONFIG.PCW_SD0_GRP_CD_ENABLE {1} \

CONFIG.PCW_SD0_GRP_CD_IO {MIO 10} \

CONFIG.PCW_SD0_GRP_POW_ENABLE {0} \

CONFIG.PCW_SD0_GRP_WP_ENABLE {0} \

CONFIG.PCW_SD0_PERIPHERAL_ENABLE {1} \

CONFIG.PCW_SD0_SD0_IO {MIO 40 .. 45} \

CONFIG.PCW_SD1_GRP_CD_ENABLE {0} \

CONFIG.PCW_SD1_GRP_POW_ENABLE {0} \

CONFIG.PCW_SD1_GRP_WP_ENABLE {0} \

CONFIG.PCW_SD1_PERIPHERAL_ENABLE {1} \

CONFIG.PCW_SD1_SD1_IO {MIO 46 .. 51} \

CONFIG.PCW_SDIO_PERIPHERAL_DIVISOR0 {10} \

CONFIG.PCW_SDIO_PERIPHERAL_FREQMHZ {100} \

CONFIG.PCW_SDIO_PERIPHERAL_VALID {1} \

CONFIG.PCW_SINGLE_QSPI_DATA_MODE {x4} \

CONFIG.PCW_SMC_PERIPHERAL_DIVISOR0 {1} \

CONFIG.PCW_SPI_PERIPHERAL_DIVISOR0 {1} \

CONFIG.PCW_TPIU_PERIPHERAL_DIVISOR0 {1} \

CONFIG.PCW_UART0_GRP_FULL_ENABLE {0} \

CONFIG.PCW_UART0_PERIPHERAL_ENABLE {1} \

CONFIG.PCW_UART0_UART0_IO {MIO 14 .. 15} \

CONFIG.PCW_UART1_GRP_FULL_ENABLE {0} \

CONFIG.PCW_UART1_PERIPHERAL_ENABLE {0} \

CONFIG.PCW_UART1_UART1_IO {<Select>} \

CONFIG.PCW_UART_PERIPHERAL_DIVISOR0 {10} \

CONFIG.PCW_UART_PERIPHERAL_FREQMHZ {100} \

CONFIG.PCW_UART_PERIPHERAL_VALID {1} \

CONFIG.PCW_UIPARAM_ACT_DDR_FREQ_MHZ {533.333374} \

CONFIG.PCW_UIPARAM_DDR_BANK_ADDR_COUNT {3} \

CONFIG.PCW_UIPARAM_DDR_CL {7} \

CONFIG.PCW_UIPARAM_DDR_COL_ADDR_COUNT {10} \

CONFIG.PCW_UIPARAM_DDR_CWL {6} \

CONFIG.PCW_UIPARAM_DDR_DEVICE_CAPACITY {4096 MBits} \

CONFIG.PCW_UIPARAM_DDR_DRAM_WIDTH {16 Bits} \

CONFIG.PCW_UIPARAM_DDR_PARTNO {MT41K256M16 RE-125} \

CONFIG.PCW_UIPARAM_DDR_ROW_ADDR_COUNT {15} \

CONFIG.PCW_UIPARAM_DDR_SPEED_BIN {DDR3_1066F} \

CONFIG.PCW_UIPARAM_DDR_T_FAW {40.0} \

CONFIG.PCW_UIPARAM_DDR_T_RAS_MIN {35.0} \

CONFIG.PCW_UIPARAM_DDR_T_RC {48.75} \

CONFIG.PCW_UIPARAM_DDR_T_RCD {7} \

CONFIG.PCW_UIPARAM_DDR_T_RP {7} \

CONFIG.PCW_USB0_PERIPHERAL_ENABLE {0} \

CONFIG.PCW_USB0_PERIPHERAL_FREQMHZ {60} \

CONFIG.PCW_USB0_RESET_ENABLE {0} \

CONFIG.PCW_USB0_USB0_IO {<Select>} \

CONFIG.PCW_USB1_RESET_ENABLE {0} \

CONFIG.PCW_USB_RESET_ENABLE {0} \

CONFIG.PCW_USB_RESET_SELECT {<Select>} \

CONFIG.PCW_USE_FABRIC_INTERRUPT {1} \

CONFIG.PCW_USE_M_AXI_GP0 {1} \

CONFIG.PCW_USE_S_AXI_HP0 {0} \

] $processing_system7_0

# Create instance: rst_ps7_0_100M, and set properties

set rst_ps7_0_100M [ create_bd_cell -type ip -vlnv xilinx.com:ip:proc_sys_reset:5.0 rst_ps7_0_100M ]

# Create instance: smartconnect_0, and set properties

set smartconnect_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:smartconnect:1.0 smartconnect_0 ]

set_property -dict [ list \

CONFIG.NUM_MI {1} \

CONFIG.NUM_SI {1} \

] $smartconnect_0

# Create instance: xlconcat_1, and set properties

set xlconcat_1 [ create_bd_cell -type ip -vlnv xilinx.com:ip:xlconcat:2.1 xlconcat_1 ]

set_property -dict [ list \

CONFIG.NUM_PORTS {1} \

] $xlconcat_1

# Create interface connections

connect_bd_intf_net -intf_net axi_uartlite_0_UART [get_bd_intf_ports uart2] [get_bd_intf_pins axi_uartlite_0/UART]

connect_bd_intf_net -intf_net processing_system7_0_DDR [get_bd_intf_ports DDR] [get_bd_intf_pins processing_system7_0/DDR]

connect_bd_intf_net -intf_net processing_system7_0_FIXED_IO [get_bd_intf_ports FIXED_IO] [get_bd_intf_pins processing_system7_0/FIXED_IO]

connect_bd_intf_net -intf_net processing_system7_0_M_AXI_GP0 [get_bd_intf_pins processing_system7_0/M_AXI_GP0] [get_bd_intf_pins smartconnect_0/S00_AXI]

connect_bd_intf_net -intf_net smartconnect_0_M00_AXI [get_bd_intf_pins axi_uartlite_0/S_AXI] [get_bd_intf_pins smartconnect_0/M00_AXI]

# Create port connections

connect_bd_net -net axi_uartlite_0_interrupt [get_bd_pins axi_uartlite_0/interrupt] [get_bd_pins xlconcat_1/In0]

connect_bd_net -net processing_system7_0_FCLK_CLK0 [get_bd_pins axi_uartlite_0/s_axi_aclk] [get_bd_pins processing_system7_0/FCLK_CLK0] [get_bd_pins processing_system7_0/M_AXI_GP0_ACLK] [get_bd_pins rst_ps7_0_100M/slowest_sync_clk] [get_bd_pins smartconnect_0/aclk]

connect_bd_net -net processing_system7_0_FCLK_RESET0_N [get_bd_pins processing_system7_0/FCLK_RESET0_N] [get_bd_pins rst_ps7_0_100M/ext_reset_in]

connect_bd_net -net rst_ps7_0_100M_peripheral_aresetn [get_bd_pins axi_uartlite_0/s_axi_aresetn] [get_bd_pins rst_ps7_0_100M/peripheral_aresetn] [get_bd_pins smartconnect_0/aresetn]

connect_bd_net -net xlconcat_1_dout [get_bd_pins processing_system7_0/IRQ_F2P] [get_bd_pins xlconcat_1/dout]

# Create address segments

assign_bd_address -offset 0x42C00000 -range 0x00001000 -target_address_space [get_bd_addr_spaces processing_system7_0/Data] [get_bd_addr_segs axi_uartlite_0/S_AXI/Reg] -force

# Restore current instance

current_bd_instance $oldCurInst

validate_bd_design

save_bd_design

}

# End of create_root_design()

##################################################################

# MAIN FLOW

##################################################################

create_root_design ""XDC

bash

# PL 串口

set_property -dict {PACKAGE_PIN K14 IOSTANDARD LVCMOS33} [get_ports uart2_rxd]

set_property -dict {PACKAGE_PIN M15 IOSTANDARD LVCMOS33} [get_ports uart2_txd]裸机回显测试 main.c

注意,这个文件未兼容c++

c

#include "xparameters.h"

#include "xuartlite.h"

#include "xil_printf.h"

#include "sleep.h"

#define UART_DEVICE_ID XPAR_AXI_UARTLITE_0_DEVICE_ID

#define MAX_RECV_LEN 16

XUartLite UartInstance;

int main() {

int status;

u8 recv_buf[MAX_RECV_LEN];

u32 recv_len;

xil_printf("UART Library API Echo Example\r\n");

// 初始化 UARTLite

status = XUartLite_Initialize(&UartInstance, UART_DEVICE_ID);

if (status != XST_SUCCESS) {

xil_printf("UART Init Failed!\r\n");

return -1;

}

XUartLite_ResetFifos(&UartInstance);

while (1) {

// 发送固定测试字节

// XUartLite_SendByte(UartInstance.RegBaseAddress, 0x55);

// 批量接收

recv_len = XUartLite_Recv(&UartInstance, recv_buf, MAX_RECV_LEN);

if (recv_len > 0) {

// 回显收到的全部内容

for (u32 i = 0; i < recv_len; i++) {

XUartLite_SendByte(UartInstance.RegBaseAddress, recv_buf[i]);

}

}

usleep(1000);

}

return 0;

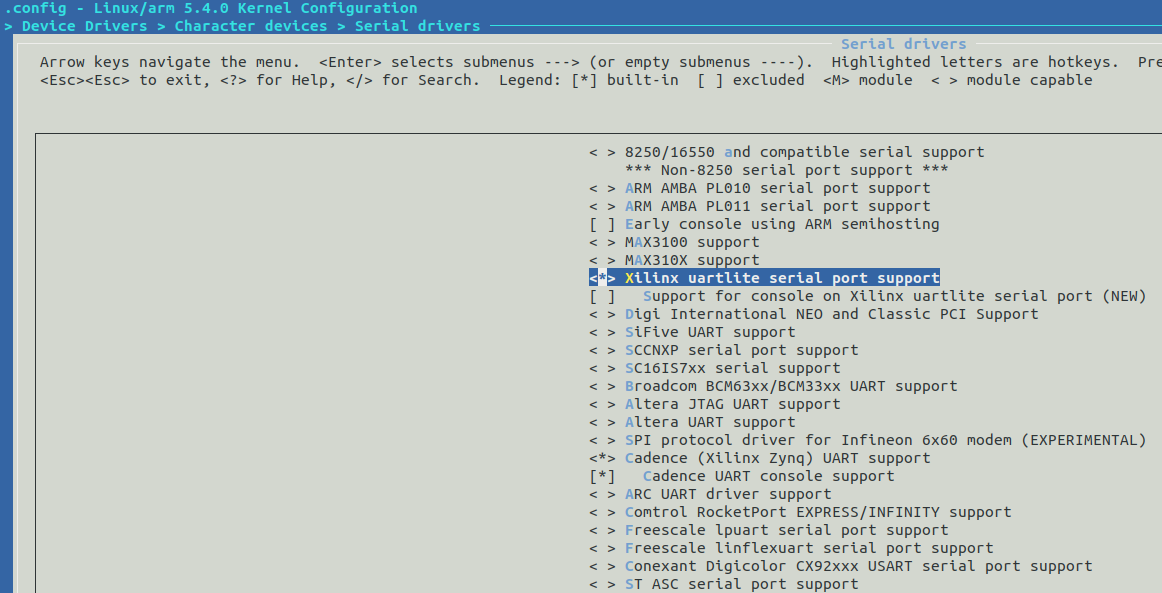

}内核配置

设备树

设备树不用写, petalinux自动生成pl.dtsi

pl.dtsi

bash

/*

* CAUTION: This file is automatically generated by Xilinx.

* Version:

* Today is: Thu Feb 12 04:39:14 2026

*/

/ {

amba_pl: amba_pl {

#address-cells = <1>;

#size-cells = <1>;

compatible = "simple-bus";

ranges ;

axi_uartlite_0: serial@42c00000 {

clock-names = "s_axi_aclk";

clocks = <&clkc 15>;

compatible = "xlnx,axi-uartlite-2.0", "xlnx,xps-uartlite-1.00.a";

current-speed = <9600>;

device_type = "serial";

interrupt-names = "interrupt";

interrupt-parent = <&intc>;

interrupts = <0 29 1>;

port-number = <1>;

reg = <0x42c00000 0x1000>;

xlnx,baudrate = <0x2580>;

xlnx,data-bits = <0x8>;

xlnx,odd-parity = <0x0>;

xlnx,s-axi-aclk-freq-hz-d = "100.0";

xlnx,use-parity = <0x0>;

};

};

};system-user.dtsi

bash

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/input/input.h>

#include <dt-bindings/media/xilinx-vip.h>

#include <dt-bindings/phy/phy.h>

/ {

model = "ant7020 Board";

compatible = "xlnx,zynq-zc702", "xlnx,zynq-7000";

chosen {

bootargs = "console=ttyPS0,115200 earlycon=cdns,mmio,0xe0000000,115200n8 keep_bootcon earlyprintk root=/dev/mmcblk0p2 rw rootwait";

stdout-path = "serial0:115200n8";

};

leds {

compatible = "gpio-leds";

gpio-led1 {

label = "led2";

gpios = <&gpio0 0 GPIO_ACTIVE_HIGH>;

default-state = "on";

};

gpio-led5 {

label = "ps_led0";

gpios = <&gpio0 7 GPIO_ACTIVE_HIGH>;

default-state = "on";

};

gpio-led6 {

label = "ps_led1";

gpios = <&gpio0 8 GPIO_ACTIVE_HIGH>;

linux,default-trigger = "timer";

};

};

};

&uart0 {

u-boot,dm-pre-reloc;

status = "okay";

};

&sdhci0 {

u-boot,dm-pre-reloc;

status = "okay";

};

&qspi {

u-boot,dm-pre-reloc;

flash@0 { /* 16 MB */

compatible = "w25q256", "jedec,spi-nor";

reg = <0x0>;

spi-max-frequency = <50000000>;

#address-cells = <1>;

#size-cells = <1>;

partition@0x00000000 {

label = "boot";

reg = <0x00000000 0x00100000>;

};

partition@0x00100000 {

label = "bootenv";

reg = <0x00100000 0x00020000>;

};

partition@0x00120000 {

label = "bitstream";

reg = <0x00120000 0x00400000>;

};

partition@0x00520000 {

label = "device-tree";

reg = <0x00520000 0x00020000>;

};

partition@0x00540000 {

label = "kernel";

reg = <0x00540000 0x00500000>;

};

partition@0x00A40000 {

label = "space";

reg = <0x00A40000 0x00000000>;

};

};

};

&gem0 {

local-mac-address = [00 0a 35 00 8b 87];

phy-handle = <ðernet_phy>;

ethernet_phy: ethernet-phy@7 { /* yt8521 */

reg = <0x7>;

device_type = "ethernet-phy";

};

};u-boot启动脚本

bash

# mkimage -c none -A arm -T script -d boot.cmd.default boot.scr

#

################

ming_mmc_devnum=1

for boot_target in ${boot_targets};

do

if test "${boot_target}" = "jtag" ; then

bootm 0x00200000 0x04000000 0x00100000

exit;

fi

if test "${boot_target}" = "mmc0" || test "${boot_target}" = "mmc1" ; then

echo " AAAAAAAAAAAAAWPF Booting from SD (zImage)...${boot_target}--${devtype} -${devnum}-${distro_bootpart} "

if test -e ${devtype} ${devnum}:${distro_bootpart} /zImage; then

fatload ${devtype} ${devnum}:${distro_bootpart} 0x00200000 zImage;;

fi

if test -e ${devtype} ${devnum}:${distro_bootpart} /system.dtb; then

fatload ${devtype} ${devnum}:${distro_bootpart} 0x00100000 system.dtb;

fi

if test -e ${devtype} ${devnum}:${distro_bootpart} /rootfs.cpio.gz.u-boot; then

fatload ${devtype} ${devnum}:${distro_bootpart} 0x04000000 rootfs.cpio.gz.u-boot;

bootm 0x00200000 0x04000000 0x00100000

exit;

fi

if test -e ${devtype} ${devnum}:${distro_bootpart} /system.bit; then

fatload ${devtype} ${devnum}:${distro_bootpart} 0x00800000 system.bit;

fpga loadb 0 ${fileaddr} ${filesize}

fi

bootz 0x00200000 - 0x00100000

exit;

fi

if test "${boot_target}" = "xspi0" || test "${boot_target}" = "qspi" || test "${boot_target}" = "qspi0"; then

echo "BBBBBBBCCCCCCKYLV1 Booting from QSPI (zImage)...${boot_target}--${devtype} -${ming_mmc_devnum}-${distro_bootpart}"

if test -z "${bootargs}"; then

setenv bootargs 'console=ttyPS0,115200 root=/dev/mmcblk1p2 rw rootwait rootfstype=ext4 earlyprintk'

fi

fatload ${devtype} ${ming_mmc_devnum}:${distro_bootpart} 0x00200000 zImage || echo "zImage not found"

fatload ${devtype} ${ming_mmc_devnum}:${distro_bootpart} 0x00100000 system.dtb || echo "system.dtb not found"

fatload ${devtype} ${ming_mmc_devnum}:${distro_bootpart} 0x00800000 system.bit && fpga loadb 0 0x00800000 ${filesize}

bootz 0x00200000 - 0x00100000

exit

fi

if test "${boot_target}" = "nand" || test "${boot_target}" = "nand0"; then

nand info

if test "image.ub" = "image.ub"; then

nand read 0x10000000 0x1000000 0x6400000;

bootm 0x10000000;

exit;

fi

if test "image.ub" = "uImage"; then

nand read 0x00200000 0x1000000 0x3200000;

nand read 0x04000000 0x4600000 0x3200000;

bootm 0x00200000 0x04000000 0x00100000

exit;

fi

fi

donedevmem简单测试

发送 helloWord

bash

#!/bin/bash

set -euo pipefail

UART_BASE=0x42C00000

RX_FIFO=0x00

TX_FIFO=0x04

STATUS=0x08

CONTROL=0x0C

echo "Using AXI UART Lite @ $UART_BASE"

# --- 复位 TX/RX FIFO ---

# bit0 = reset RX

# bit1 = reset TX

devmem $((UART_BASE+CONTROL)) 32 0x03

sleep 0.1

# --- 发送 helloWord ---

msg="helloWord"

for ((i=0; i<${#msg}; i++)); do

char=${msg:$i:1}

# 等待 TX FIFO 不满 (bit3=0)

while true; do

status=$(devmem $((UART_BASE+STATUS)) 32)

if (( (status & 0x08) == 0 )); then

break

fi

done

# 写入 TX FIFO

devmem $((UART_BASE+TX_FIFO)) 32 "$(printf '0x%x' "'$char")"

done

echo "Done sending 'helloWord' via AXI UART Lite!"回环测试

bash

#!/bin/bash

set -euo pipefail

UART_BASE=0x42C00000

RX_FIFO=0x00

TX_FIFO=0x04

STATUS=0x08

CONTROL=0x0C

echo "Using AXI UART Lite @ $UART_BASE"

# --- 复位 FIFO ---

# bit0 = reset RX

# bit1 = reset TX

devmem $((UART_BASE+CONTROL)) 32 0x03

sleep 0.1

echo "Starting AXI UART Lite loopback test. Press Ctrl+C to exit."

while true; do

status=$(devmem $((UART_BASE+STATUS)) 32)

# --- RX 有数据 (bit0=1) ---

if (( (status & 0x01) != 0 )); then

# 读取一个字节

data=$(devmem $((UART_BASE+RX_FIFO)) 32)

data=$((data & 0xFF))

# 本地打印

printf "%s" "$(printf '\\x%02x' $data)"

# --- 等待 TX FIFO 不满 (bit3=0) ---

while true; do

status_tx=$(devmem $((UART_BASE+STATUS)) 32)

if (( (status_tx & 0x08) == 0 )); then

break

fi

done

# 写回发送 FIFO(回显)

devmem $((UART_BASE+TX_FIFO)) 32 "$data"

fi

done测试

bash

root@ant:~# dmesg | grep tty

[ 0.000000] Kernel command line: console=ttyPS0,115200 root=/dev/mmcblk1p2 rw rootwait rootfstype=ext4 earlyprintk

[ 0.290141] e0000000.serial: ttyPS0 at MMIO 0xe0000000 (irq = 24, base_baud = 6249999) is a xuartps

[ 0.615716] printk: console [ttyPS0] enabled

[ 0.815396] 42c00000.serial: ttyUL1 at MMIO 0x42c00000 (irq = 46, base_baud = 0) is a uartlite

root@ant:~# echo "hello" > /dev/ttyUL1