GTX DRP动态重配置技术

- [1. 动态重配置端口](#1. 动态重配置端口)

-

- [1.1 功能描述](#1.1 功能描述)

- [1.2 端口属性](#1.2 端口属性)

- [1.3 使用模式](#1.3 使用模式)

-

- [1.3.1 写入操作](#1.3.1 写入操作)

- [1.3.2 读取操作](#1.3.2 读取操作)

- [2. 总结](#2. 总结)

1. 动态重配置端口

1.1 功能描述

动态重配置端口(DRP)允许动态改变GTXE2_CHANNEL/GTHE2_CHANNEL和GTXE2-COMMON/GTHE2_COMMIN的参数。DRP接口是一个处理器友好的同步接口,具有地址总线(DRPADDR)和独立的数据总线,用于读取(DRPDO)和写入(DRPDI)配置数据到基元。使能信号(DRPEN)、读写信号(DRPWE)和就绪/有效信号(DRPRDY)是实现读和写操作、指示操作完成或指示数据可用性的控制信号。

1.2 端口属性

下面显示GTXE2_CHANNEL/GTHE2_CHANNEL的DRP相关端口。

| 端口 | 方向 | 时钟域 | 描述 |

|---|---|---|---|

| DRPADDR[8:0] | 输入 | DRPCLK | DRP地址总线 |

| DRPCLK | 输入 | N/A | DRP接口时钟 |

| DRPEN | 输入 | DRPCLK | DRP使能信号。0:不执行读取或写入操作。1:使能读或写操作。 |

| DRPDI[15:0] | 输入 | DRPCLK | 用于将配置数据从FPGA逻辑资源写入收发器的数据总线。 |

| DRPRDY | 输出 | DRPCLK | 表示写操作完成,数据对读操作有效 |

| DRPDO[15:0] | 输出 | DRPCLK | 用于从GTX/GTH收发器向FPGA逻辑资源读取配置数据的数据总线。 |

| DRPWE | 输入 | DRPCLK | DRP写使能。DRPEN为1时的读取操作。DRPEN为1时的写操作。 |

下面显示了GTXE2_COMMON/GTHE2_COMMON的DRP相关端口。

| 端口 | 方向 | 时钟域 | 描述 |

|---|---|---|---|

| DRPADDR[7:0] | 输入 | DRPCLK | DRP地址总线 |

| DRPCLK | 输入 | N/A | DRP接口时钟 |

| DRPEN | 输入 | DRPCLK | DRP使能信号。0:不执行读取或写入操作。1:使能读或写操作。 |

| DRPDI[15:0] | 输入 | DRPCLK | 用于将配置数据从FPGA逻辑资源写入收发器的数据总线。 |

| DRPRDY | 输出 | DRPCLK | 表示写操作完成,数据对读操作有效 |

| DRPDO[15:0] | 输出 | DRPCLK | 用于从GTX/GTH收发器向FPGA逻辑资源读取配置数据的数据总线。 |

| DRPWE | 输入 | DRPCLK | DRP写使能。DRPEN为1时的读取操作。DRPEN为1时的写操作。 |

1.3 使用模式

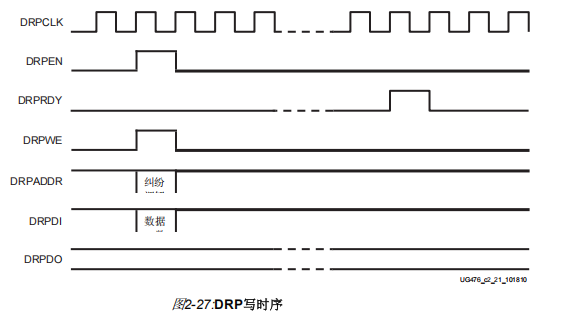

1.3.1 写入操作

下图显示了DRP写操作时序。当DRPRDY置位时,可以启动新的DRP操作。

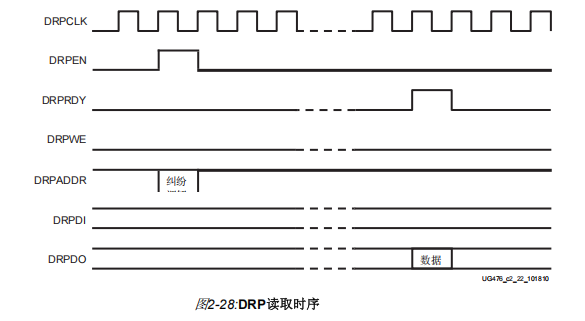

1.3.2 读取操作

下图显示了DRP读取操作时序。当DRPRDY置位时,可以启动新的DRP操作。

2. 总结

今天就简单介绍到这里,后续会更新DRP如何用软件实现动态配置,我是码不停蹄,咱们下期见~~~