UVM的 uvm_object类的随机化、拷贝、克隆、比较、打印

-

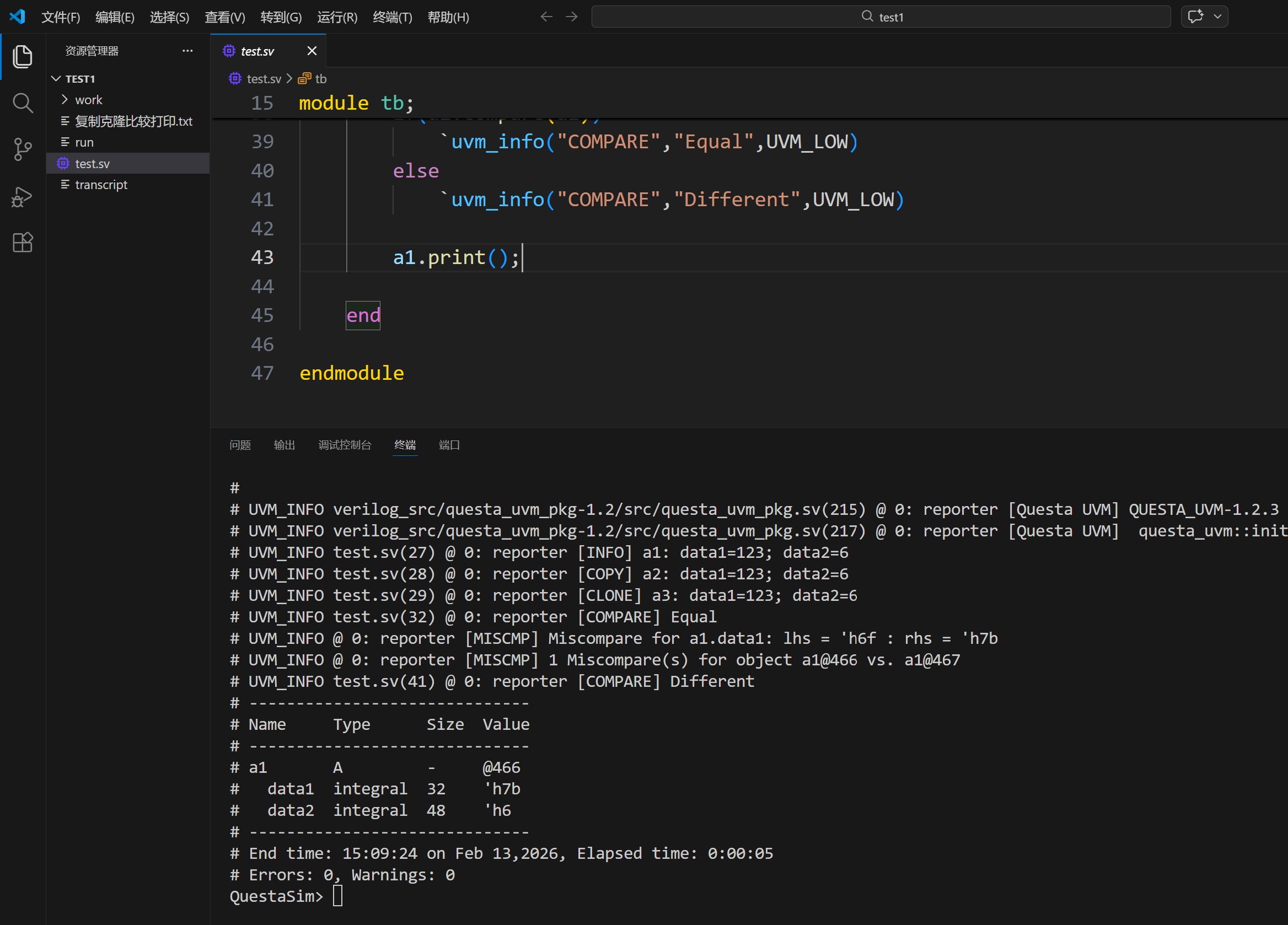

create():UVM工厂模式创建对象,是UVM推荐的对象实例化方式(而非直接new());

-

copy():浅拷贝,仅复制注册字段的值(基本类型直接复制,对象句柄仅复制指向);

-

clone():深拷贝,先创建新对象,再将原对象的字段值拷贝到新对象,返回父类uvm_object句柄,需$cast转换;

-

compare():对比两个对象的所有注册字段值,返回布尔值;

-

print():自动化打印所有注册字段的信息(名称、类型、大小、值)。

// 导入UVM核心包,包含UVM的基础类、方法和宏定义

import uvm_pkg::*;

// 包含UVM宏定义文件,必须和uvm_pkg配合使用

`include "uvm_macros.svh"// 定义自定义UVM对象类A,继承自uvm_object(UVM所有数据对象的基类)

// uvm_object主要用于存储数据,支持copy/clone/compare/print等自动化方法

class A extends uvm_object;

// 定义随机整型变量data1(32位有符号整型)

rand int data1;

// 定义随机48位无符号比特变量data2(bit类型默认无符号)

rand bit[47:0] data2;// UVM自动化字段注册宏:开始注册类A的字段 // 注册后才能使用UVM提供的copy/clone/compare/print等自动化方法 `uvm_object_utils_begin(A) // 注册整型字段data1,UVM_ALL_ON表示启用该字段的所有自动化功能 `uvm_field_int(data1, UVM_ALL_ON) // 注册48位比特字段data2,同样启用所有自动化功能 `uvm_field_int(data2, UVM_ALL_ON) // 结束字段注册 `uvm_object_utils_end // 类的构造函数(UVM推荐显式定义,调用父类构造函数) // name参数用于UVM的层次化打印和调试 function new(string name = "A"); super.new(name); endfunctionendclass

// 测试模块tb:仿真的顶层模块,用于验证类A的功能

module tb;// initial块:SystemVerilog的初始化块,仿真开始时执行(仅执行一次) initial begin // 声明三个类A的对象句柄(仅声明,未分配内存) A a1,a2,a3; // 1. 创建UVM对象:通过type_id::create()方法(UVM推荐方式) // 相比直接new(),create()支持工厂模式,便于后续重载/替换类 a1 = A::type_id::create("a1"); // 创建对象a1,命名为"a1" a2 = A::type_id::create("a1"); // 注意:a2命名也为"a1"(名称重复不影响功能,仅调试时易混淆) // 2. 带内联约束的随机化: // randomize() with {} 为内联约束,优先级高于类内约束(本例类内无约束) // assert检查随机化是否成功:成功返回1,失败返回0(触发assert报错) assert(a1.randomize() with { data1 == 123; data2<10;}); // 3. copy方法:将a1的所有注册字段值浅拷贝到a2 // 浅拷贝:对于基本类型(int/bit),直接复制值;对于对象句柄,仅复制句柄(指向同一对象) a2.copy(a1); // 4. clone方法:克隆a1(深拷贝),返回uvm_object类型的句柄 // $cast:将父类句柄(uvm_object)向下转换为子类句柄(A),确保类型匹配 $cast(a3,a1.clone()); // 打印a1的数值:UVM_INFO宏(优先级UVM_LOW,默认打印) // $sformatf:格式化字符串,输出data1和data2的十进制值 `uvm_info("INFO", $sformatf("a1: data1=%0d; data2=%0d",a1.data1,a1.data2), UVM_LOW) // 打印copy后的a2数值,验证拷贝是否成功 `uvm_info("COPY", $sformatf("a2: data1=%0d; data2=%0d",a2.data1,a2.data2), UVM_LOW) // 打印clone后的a3数值,验证克隆是否成功 `uvm_info("CLONE", $sformatf("a3: data1=%0d; data2=%0d",a3.data1,a3.data2), UVM_LOW) // 5. compare方法:比较a2和a1的所有注册字段值是否完全一致 // 一致返回1,不一致返回0 if(a2.compare(a1)) `uvm_info("COMPARE","a2 and a1 are Equal",UVM_LOW) else `uvm_info("COMPARE","a2 and a1 are Different",UVM_LOW) // 修改a2的data1值,破坏与a1的一致性 a2.data1 = 111; // 再次比较a2和a1,验证修改后是否不一致 if(a2.compare(a1)) `uvm_info("COMPARE","a2 and a1 are Equal",UVM_LOW) else `uvm_info("COMPARE","a2 and a1 are Different",UVM_LOW) // 6. print方法:打印a1的所有注册字段的详细信息(层次化、类型、值) // 依赖`uvm_field_int`注册的字段,自动输出格式规整的信息 a1.print(); endendmodule

关键语法:

- rand:标记变量为随机变量,需调用randomize()才能随机取值;

- randomize() with {}:内联约束,临时修改/添加随机约束,优先级高于类内约束;

- $cast:类型转换,确保父类句柄安全转换为子类句柄(避免类型不匹配错误);

- UVM_INFO:UVM标准打印宏,格式为(标识, 消息, 优先级),便于日志分类和过滤。

上机实操

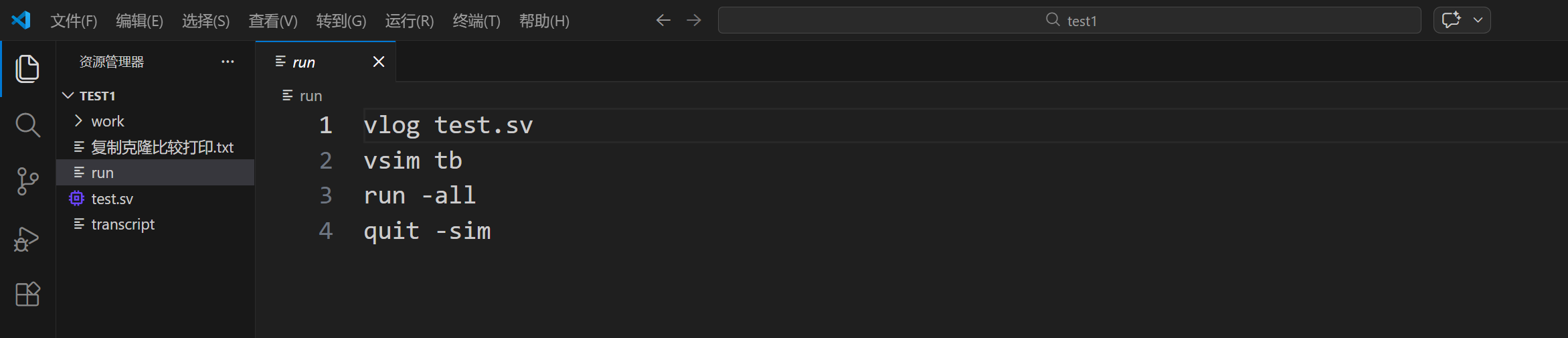

按照**SystemVerilog小白入门2,QuestaSim初体验** 配置编译允许环境。