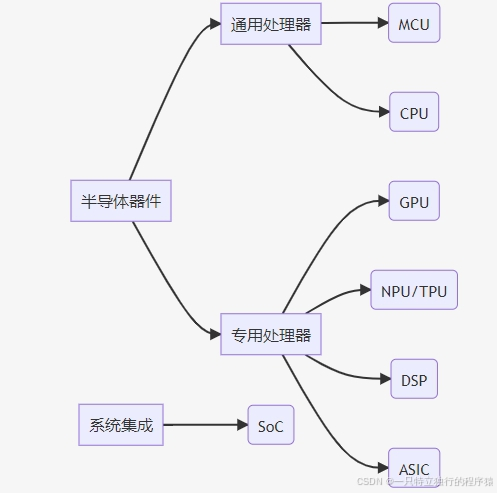

车载SoC是智能汽车的核心计算平台,集成了CPU、GPU、NPU和DSP等异构处理单元。CPU作为系统管家负责任务调度和操作系统管理;GPU专注图形渲染和并行计算;NPU专精AI推理,支撑自动驾驶感知;DSP处理实时信号,优化音视频数据。评估SoC需关注算力、能效比、内存带宽、延迟和功能安全等指标。其中安全CPU采用锁步核技术,通过双核冗余运行确保系统可靠性,是满足汽车最高安全等级(ASIL-D)的关键设计。各单元协同工作,共同实现智能驾驶和座舱功能。

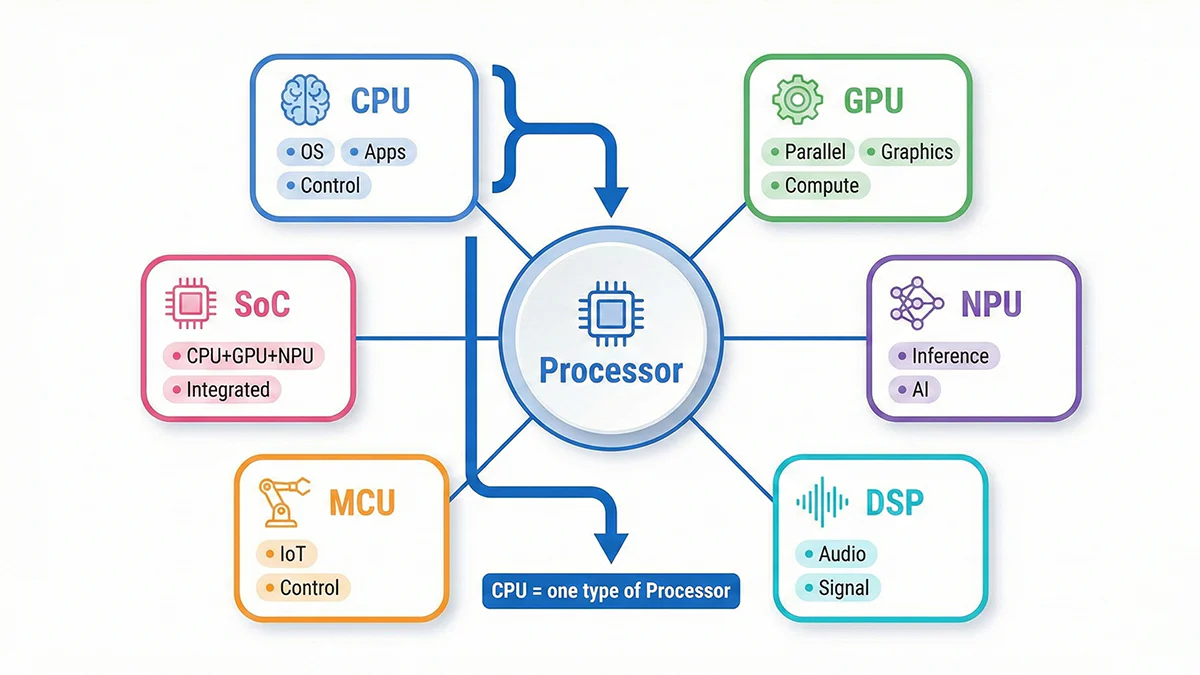

车载 SoC(System-on-Chip,片上系统)是智能汽车的"大脑",它不是单一的处理器,而是一个集成了 CPU、GPU、NPU、DSP 等多种异构处理单元的复杂系统。不同的处理单元各司其职,共同支撑起智能座舱、自动驾驶等核心功能。

以下是对 CPU、GPU、NPU、DSP 的详细介绍,关键技术评估指标,以及它们在车载 SoC 中的角色解析。

一、 核心处理单元详解

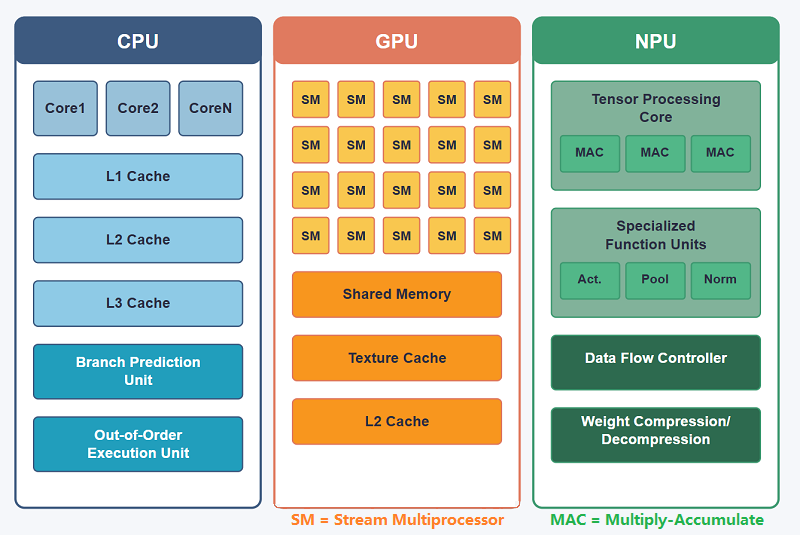

1. CPU (Central Processing Unit) - 中央处理器

- 角色: 它是 SoC 的"管家"和"指挥官"。CPU 擅长处理复杂的逻辑控制、任务调度、操作系统管理以及通用的串行计算。

- 在车载 SoC 中的作用:

- 运行操作系统(如 Android, QNX, Linux)。

- 管理应用逻辑(如 APP 启动、导航逻辑)。

- 调度其他处理器(如指挥 NPU 进行 AI 推理)。

- 处理高实时性、高安全性的控制指令(如车辆状态监控)。

- 特点: 通用性强,但并行计算效率不如专用加速器。

2. GPU (Graphics Processing Unit) - 图形处理器

- 角色: 它是"画家"和"并行计算专家"。最初用于图形渲染,现在也广泛用于大规模并行计算(GPGPU)。

- 在车载 SoC 中的作用:

- 图形渲染: 负责 3D 仪表盘、中控大屏 UI、3D 导航地图、流媒体后视镜的图像显示。

- 通用计算: 早期自动驾驶算法常利用 GPU 进行图像预处理和部分 AI 推理(虽然效率不如 NPU,但灵活性高)。

- 特点: 擅长处理海量、同类型的数据(如像素点),高并发,吞吐量大。

3. NPU (Neural Processing Unit) - 神经网络处理器

- 别名: AI 加速器、TPU(Tensor Processing Unit)、BPU(Brain Processing Unit,地平线命名)。

- 角色: 它是"AI 专才"。专为深度学习算法(如卷积神经网络 CNN、Transformer)设计的专用硬件,擅长进行矩阵乘法运算。

- 在车载 SoC 中的作用:

- 自动驾驶感知: 实时处理摄像头、激光雷达数据,识别行人、车辆、车道线、交通标志。

- 座舱交互: 语音识别(NLP)、手势识别、驾驶员疲劳监测(DMS)。

- 特点: 相比 GPU,NPU 在执行 AI 任务时能效比(Performance per Watt)极高,速度更快,功耗更低。

4. DSP (Digital Signal Processor) - 数字信号处理器

- 角色: 它是"数学家"。专为实时数字信号处理设计,擅长快速进行加法、乘法等数学运算。

- 在车载 SoC 中的作用:

- 音频处理: 降噪、回声消除、音效增强、主动降噪(ANC)。

- 图像预处理(ISP 辅助): 摄像头原始数据(RAW Data)的去噪、白平衡。

- 雷达信号处理: 处理毫米波雷达的回波数据,计算距离和速度。

- 特点: 实时性极强,延迟极低,功耗极低,适合处理流式数据。

二、 关键技术指标评估

在选型或评估车载 SoC 时,我们通常关注以下核心指标:

1. 算力 (Performance)

- CPU: DMIPS (Dhrystone Million Instructions Per Second)。衡量整数运算能力。

- 参考值: 高通 8155 约为 90-100k DMIPS;8295 约为 200k+ DMIPS。

- GPU: GFLOPS (Giga Floating-point Operations Per Second) 或 TFLOPS 。衡量浮点运算能力。

- 参考值: 8155 约为 1 TFLOPS;8295 约为 3 TFLOPS。

- NPU: TOPS (Tera Operations Per Second)。衡量 AI 推理能力(通常指 INT8 精度)。

- 参考值:

- 座舱芯片:8155 (4-8 TOPS), 8295 (30 TOPS)。

- 智驾芯片:Orin-X (254 TOPS), 地平线 J5 (128 TOPS)。

- 参考值:

- 注意: 单看 TOPS 是不够的,还要看有效算力(FPS/Watt)和ResNet-50 等标准模型的实测帧率。

2. 能效比 (Energy Efficiency)

- 指标: TOPS/Watt。

- 意义: 车载环境散热受限(尤其是集成在密闭空间),高能效意味着在同等功耗下性能更强,发热更少。NPU 的能效通常远高于 GPU。

3. 内存带宽 (Memory Bandwidth)

- 指标: GB/s。

- 意义: 即使算力再强,如果数据传输跟不上("内存墙"问题),性能也发挥不出来。处理高清视频流(如 800万像素摄像头)和大型 AI 模型时,高带宽至关重要。

4. 实时性与延迟 (Latency)

- 指标: 毫秒 (ms)。

- 意义: 对于自动驾驶(如 AEB 紧急制动)和音频处理,低延迟是安全红线。DSP 和 MCU(微控制器单元)通常用于保障低延迟任务。

5. 功能安全 (Functional Safety)

- 指标: ISO 26262 ASIL 等级 (A/B/C/D)。

- 意义: 智驾相关模块通常要求达到 ASIL-D(最高等级),座舱娱乐一般要求 ASIL-B。SoC 内部通常会有独立的**安全岛(Safety Island)**设计,由锁步核(Lockstep Cores)MCU 负责。

三、 异构计算在车载 SoC 中的协同关系

现代车载 SoC(如高通 Snapdragon Ride、NVIDIA Orin、地平线征程)采用异构计算架构,让不同的核做最擅长的事,实现"1+1+1+1 > 4"的效果。

协同工作流示例(以自动驾驶场景为例):

- ISP (图像信号处理,常与 DSP 结合): 接收摄像头原始数据,进行降噪、曝光调整,输出 YUV 图像。

- NPU: 接手图像,运行深度学习模型,识别出"前方 50 米有人"、"车道线向左弯"。

- DSP: 处理毫米波雷达数据,计算出"前方障碍物速度 30km/h"。

- CPU: 汇总 NPU 和 DSP 的结果(传感器融合),基于规则逻辑("有人且距离近 -> 刹车"),做出驾驶决策,并向底盘发送指令。同时,CPU 负责将识别结果绘制到 GPU 进行可视化显示。

- GPU: 渲染 3D 场景,将车辆感知到的世界(车道、行人、车辆模型)实时显示在中控屏上供驾驶员参考。

总结

- CPU 是统筹全局的大脑。

- GPU 是负责视觉呈现的画师。

- NPU 是识别万物的 AI 引擎。

- DSP 是处理信号的数学工兵。

车载 SoC 的强大不在于某一个指标的极致,而在于异构单元的均衡配置 、高带宽的数据吞吐能力 以及软硬件的深度耦合。

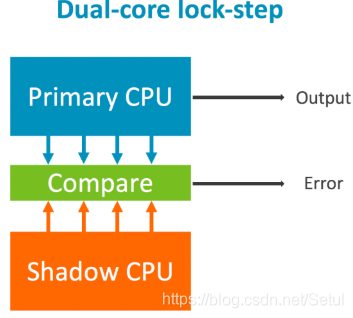

安全 CPU 与锁步核(Lockstep Core)技术介绍

在车载 SoC(系统级芯片)中,除了负责高性能计算的通用 CPU、GPU 和 NPU 外,还有一个至关重要的部分------安全 CPU 。它通常作为 SoC 内部的"安全岛"(Safety Island)存在,或者作为独立的 MCU(微控制器)芯片存在,其核心任务不是跑得快,而是跑得稳、不出错。

而**锁步核(Lockstep Core)**技术,正是实现高等级功能安全(Functional Safety)的核心手段。

一、 什么是安全 CPU?

安全 CPU 是专门为满足汽车行业严苛的功能安全标准(如 ISO 26262)而设计的处理器单元。它的设计目标是:在发生硬件故障(如宇宙射线导致的比特翻转、电路老化短路等)时,能够及时检测出错误,并使系统进入安全状态(Fail-Safe),防止灾难性后果(如车辆失控)。

1. 核心特征

- 高可靠性: 能够容忍恶劣环境(高温、震动、电磁干扰)。

- 高诊断覆盖率: 能够检测出 99% 以上的单点故障(Single Point Fault)。

- 确定性: 任务执行时间是可预测的,不能有时快有时慢。

- 独立性: 通常拥有独立的电源、时钟和复位电路,与 SoC 上的其他高性能计算单元(如跑 Android 的大核)在物理和逻辑上隔离。

2. 在车载 SoC 中的作用

- 系统监控: 监控主 SoC 的健康状态(看门狗功能)。

- 车辆控制: 负责底盘控制、刹车、转向等与生命安全直接相关的指令执行。

- 安全启动与管理: 负责 SoC 的安全启动(Secure Boot)、密钥管理、OTA 升级验证。

- 最后一道防线: 当主计算单元(如 NPU 跑飞了)失效时,安全 CPU 接管车辆控制权,执行最小风险策略(如缓慢停车)。

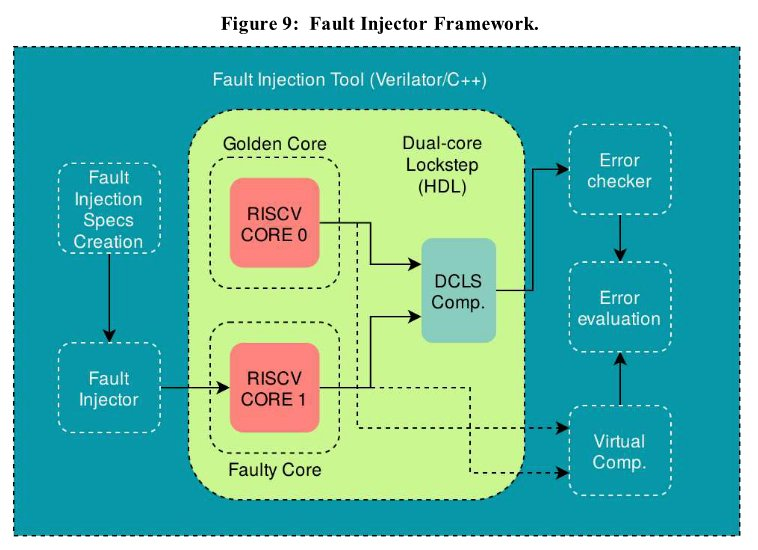

二、 什么是锁步核(Lockstep Core)?

锁步核是一种硬件冗余架构,是实现安全 CPU 最高安全等级(ASIL-D)的关键技术。

1. 工作原理:双核"连体婴"

想象一下,为了确保一道数学题算对,找两个学生同时做题:

- 双核运行: 两个完全相同的 CPU 核心(Core 1 和 Core 2),运行完全相同的指令序列。

- 时钟同步: 两个核心在时钟周期上是严格同步的(Lockstep),或者有固定的时钟延迟(为了防止共因失效,比如电压波动同时影响两个核)。

- 输出比较: 两个核心的输出结果不直接去控制外设,而是先送入一个**比较器(Comparator)**硬件逻辑。

- 如果 Core 1 的结果 == Core 2 的结果,比较器才放行,输出指令。

- 如果 Core 1 的结果 != Core 2 的结果(说明其中一个核出错了),比较器立即报错,触发安全中断或复位。

2. 为什么要"锁步"?

在半导体工艺越来越微小的今天,**软错误(Soft Error)**发生的概率越来越大。比如一个高能粒子打在芯片上,可能把内存里的一个 0 变成了 1(比特翻转)。

- 非锁步核(普通 CPU): 根本不知道自己算错了,错误指令发出,导致车辆误动作。

- 锁步核: 粒子同时打中两个核且产生相同错误的概率极低。只要结果不一致,系统就能立刻感知到"有错误发生",从而采取保护措施。

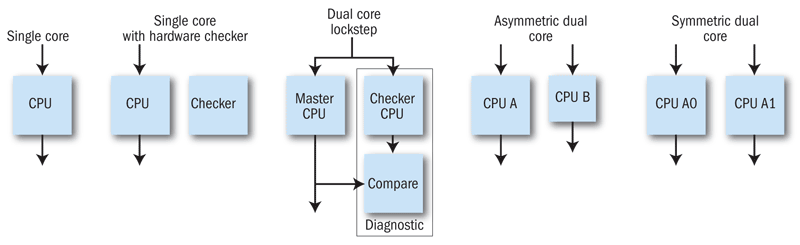

3. 常见的锁步架构

- 1oo1 (1 out of 1): 单核,无硬件冗余,通过软件自检实现低等级安全(ASIL-A/B)。

- 1oo2 (1 out of 2) Lockstep: 这是最主流的车载安全架构。 双核锁步,用于检测错误。一旦发现不一致,系统报错并进入安全状态(Fail-Safe)。这能达到 ISO 26262 ASIL-D(最高等级)。

- 2oo3 (2 out of 3): 三核冗余(常见于航空航天)。三个核投票,两个一样的就输出结果。这不仅能检测错误,还能纠正错误并继续运行(Fail-Operational)。但在汽车成本敏感场景下,通常通过系统级冗余(如两个独立的 SoC)来实现类似效果,单芯片内较少用三核锁步。

三、 锁步核与普通多核的区别

| 特性 | 锁步核模式 (Lockstep Mode) | 分离/性能模式 (Split/Performance Mode) |

|---|---|---|

| 核心数量 | 物理上有 2 个核,但在软件/系统看来只有 1 个逻辑核。 | 物理上 2 个核,软件也看到 2 个逻辑核。 |

| 算力 | 算力 减半(两个核干一件事)。 | 算力 翻倍(两个核各干各的事)。 |

| 安全性 | 极高 (ASIL-D),硬件实时检测错误。 | 较低 (ASIL-B),依赖软件机制检测错误。 |

| 应用场景 | 刹车、转向、气囊、底盘控制。 | 娱乐系统、仪表显示、辅助驾驶感知。 |

| 典型架构 | ARM Cortex-R52 Lockstep, Infineon TriCore | ARM Cortex-A 系列 SMP (对称多处理) |

注: 现代先进的安全 CPU(如 ARM Cortex-R52)通常支持动态配置。既可以在启动时配置为"锁步模式"跑安全任务,也可以配置为"分离模式"跑高性能任务,提供了极大的灵活性。

四、 总结

- 安全 CPU 是车载 SoC 中负责"保命"的独立单元,是功能安全的基石。

- 锁步核 是安全 CPU 达到 ASIL-D 最高安全等级的核心技术手段,通过"双核同步计算、硬件实时比对"来消灭随机硬件故障带来的风险。

- 在智能汽车中,你可以容忍中控屏死机(由普通 CPU/GPU 负责),但绝不能容忍刹车失灵(由安全 CPU/锁步核 负责)。