汽车电子架构正加速向区域化和集中化演进,MCUless(去微控制器化)方案成为重要技术方向。该方案将传统MCU功能集成至高性能SoC的"安全岛"中,需重点考量五大核心指标:功能安全(需满足ASIL-D级别)、实时性与确定性(微秒级响应)、电源管理(待机功耗控制)、I/O资源集成度(多路CAN-FD支持等)以及成本与供应链稳定性。同时,边缘连接技术呈现多元化发展,传统CAN、10BASE-T1S、E2B和GPAN等技术各具特点,其中E2B凭借硬件状态机设计成为MCUless标杆方案。方案选型需特别关注静态功耗、启动时序、同步精度等关键性能参数。

在汽车电子架构向 Zonal(区域化) 和 Centralized(中心化) 演进的过程中,MCUless(去微控制器化) 方案成了一个热门但极具挑战的选项。所谓 MCUless,并非真的不需要实时处理能力,而是将原本独立的物理 MCU 撤掉,将其功能集成进性能更强大的 SoC(如高通 8155/8295、恩智浦 S32G、芯驰 X9 等) 内部的"安全岛"(Safety Island)或实时核中。

在进行 MCUless 方案选型和设计时,需要重点关注以下五个维度的核心指标:

1. 功能安全 (Functional Safety) ------ 核心门槛

MCU 被"裁掉"了,但它承担的 ASIL 级别(通常是 ASIL-D)不能丢。这是 MCUless 设计中最难的一环。

-

安全岛隔离度 (Hardware Isolation): 观察 SoC 内部的实时核(通常是 Cortex-R52 或 R5F)是否拥有独立的电源、时钟和复位电路。如果大核挂了,安全岛必须能独立存活。

-

ASIL 级别能力: SoC 整体可能只支持 ASIL-B,但其内部的实时子系统(Real-time Subsystem)必须支持 ASIL-D。

-

诊断覆盖率 (Diagnostic Coverage): 关注 SoC 是否支持锁步核(Lock-step)、硬件 ECC(内存纠错)以及 BIST(内置自检)功能。

2. 实时性与确定性 (Real-time & Determinism)

MCU 的强项是"言出必行"。在 SoC 中模拟 MCU 时,必须关注延迟。

-

中断响应延迟 (Interrupt Latency): MCU 级别的响应通常在微秒(µs)级。在 MCUless 方案中,需要评估从 CAN 信号到达引脚到实时核处理完毕的端到端时延。

-

核间通信 (IPC) 效率: 如果 Linux 大核需要调用安全岛的功能,IPC 的带宽和确定性至关重要。关注是否有硬件信箱(Mailbox)或共享内存的硬件同步机制。

-

抖动 (Jitter): 评估在 SoC 满负荷运转(大核在跑 AI 模型或图形渲染)时,实时核的性能是否受影响(即 FFI:Freedom from Interference)。

3. 电源管理与功耗 (Power Management) ------ 最大的"坑"

这是很多 MCUless 设计失败的原因。传统 MCU 的待机功耗是微安(µA)级的,而 SoC 哪怕是待机通常也是毫安(mA)级。

-

静态功耗 (Quiescent Current): 车辆熄火后,TBox 或网关必须保持极低功耗。MCUless 方案中,如何只唤醒 SoC 的一小部分(Safety Island)而让其他部分彻底断电?

-

唤醒时间 (Wake-up Time):

-

CAN 响应速度: 汽车要求冷启动后 100ms-200ms 内必须响应 CAN 信号。

-

倒车影像显示: 通常要求 2 秒内出图像。MCUless 方案必须支持快启(Fast Boot)或 STR(Suspend to RAM)。

-

-

电源域划分: 评估 SoC 是否支持颗粒度极细的电源域控制(Power Gating)。

4. I/O 资源与外设集成度

MCU 以前是连结各种传感器的桥梁。MCUless 要求 SoC 本身具备极强的物理连接能力。

| 指标 | 关注重点 |

|---|---|

| CAN-FD/LIN 数量 | 至少需要 4-8 路 CAN-FD,且硬件缓存要够大,防止丢包。 |

| ADC/PWM 精度 | 用于电池电压采样或电机控制,看 SoC 的模拟外设是否达到了车载级精度。 |

| 硬件加密引擎 (HSM) | 必须支持国产或国际标准的加密算法(SM2/3/4 或 AES),且要在安全岛内独立运行,用于 Secure Boot。 |

| 引脚复用 (Mux) 灵活性 | SoC 引脚复杂,需确保高带宽接口(如 PCIe/以太网)不与实时控制引脚冲突。 |

5. 成本与供应链稳定性 (BOM & Supply Chain)

虽然 MCUless 减少了一颗芯片,但整体成本不一定降低。

-

BOM 简化程度: 评估是否因为 MCU 的移除而增加了外围复杂的电源管理芯片(PMIC)或更昂贵的板材(SoC 通常需要更多层数的 PCB)。

-

软件复杂度溢价: 开发一套基于 SoC 内部实时核的 RTOS + Linux 的混合系统,研发成本和测试周期远高于传统"MCU + SoC"的解耦方案。

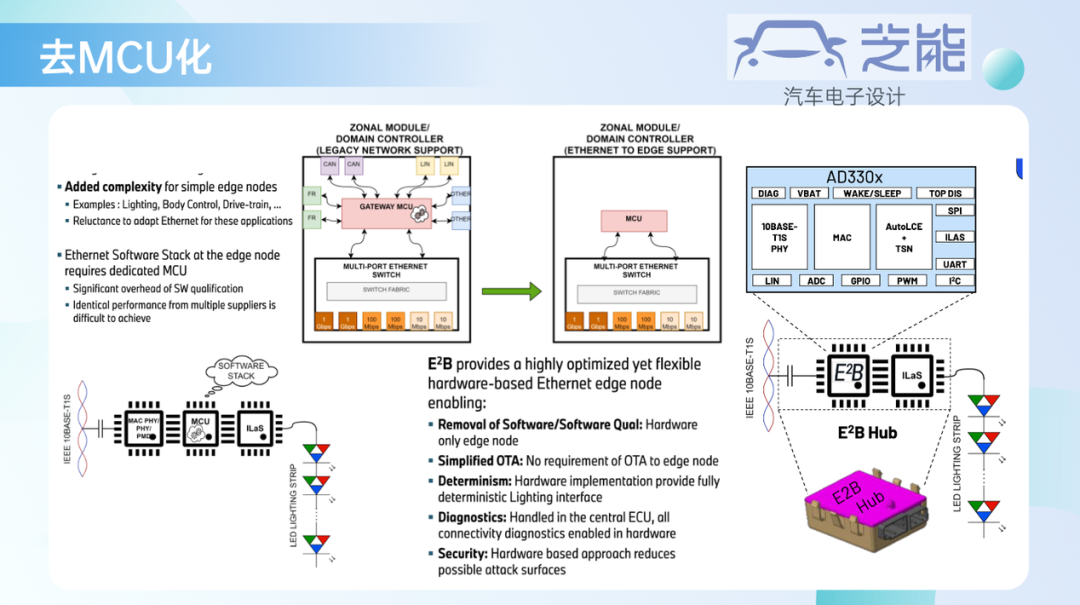

在 2026 年的车载电子架构演进中,"边缘去微控制器化"(MCUless at the Edge) 已从技术概念转变为量产实战。其核心逻辑是将原本分散在成百上千个末端节点(传感器、执行器)中的软件逻辑剥离,收回到中央计算单元或区域控制器(ZCU)中。

以下是针对 E2B、10BASE-T1S、GPAN 以及传统 CAN 方案的深度综合对比与设计指南。

1. 四大边缘连接技术综合对比表

| 特性 | CAN / CAN FD | 10BASE-T1S | E2B (ADI) | GPAN |

|---|---|---|---|---|

| 技术本质 | 传统信号总线 | 工业标准以太网 | 硬件加速以太网透传 | 协议隧道 (Tunneling) |

| MCU 依赖 | 必须有 MCU | 通常需要极小 MCU | 完全无需 MCU | 完全无需 MCU |

| 带宽能力 | 1 - 8Mbps | 10Mbps | 10Mbps | 100Mbps - 1Gbps |

| 通信拓扑 | 总线型 (Bus) | 总线型 (Multidrop) | 总线型 / 树状 | 点对多点 (Star/Tree) |

| 核心优势 | 成本极低、生态成熟 | 全栈 IP、标准统一 | 零软件、高同步 | 多协议融合、高带宽 |

| 典型应用 | 车窗、后视镜 | 动力/底盘基础通信 | BMS 采样、氛围灯、音频 | 智驾传感器、复杂 IO 扩展 |

2. 核心技术方案详述

A. 传统派:CAN / CAN FD (被革命者)

在 MCUless 架构中,CAN 是主要被替代的对象。

- 局限性: 每个 CAN 节点都必须有一个 MCU 来运行协议栈。这导致了严重的"软件碎片化"------你需要为全车几十个不同的 MCU 维护固件、处理 OTA,复杂度极高。

B. 标准派:10BASE-T1S (以太网延伸)

这是 IEEE 802.3cg 定义的标准,旨在实现"全车一网"。

-

PLCA 机制: 通过物理层冲突避免(PLCA)技术,它解决了传统以太网在总线模式下的碰撞问题,保证了确定的时延(通常在 ms 级)。

-

MCUless 潜力: 虽然标准允许硬件直控,但目前大多数 10BASE-T1S 节点仍保留了一个极简 MCU 用于处理 MAC 层的握手。

C. 激进派:E2B (Ethernet to the Edge)

ADI 基于 10BASE-T1S 物理层开发的专有技术,是目前 MCUless 的标杆。

-

硬件状态机: E2B 节点内部没有 CPU,只有硬件逻辑。中央控制器通过 RCP(远程控制协议) 直接像操作本地寄存器一样开关边缘节点的 GPIO、PWM。

-

零软件开销: 边缘节点无需固件升级,不存在"变砖"风险,显著降低了功能安全(ASIL)的认证难度。

D. 高能派:GPAN (General Purpose Automotive Network)

GPAN 是为了解决"高带宽需求"下的 MCUless 需求。

-

协议隧道: 它像一条高速公路,把 GPIO、I2C、SPI、甚至 CAN 信号打包进 1Gbps 的大包里传输。

-

全能适配: 你可以只用一根线,就把车门上所有的按键、电机驱动、传感器数据全部透传到中央 SoC,而车门内不再需要任何处理器。

3. MCUless 方案选型与设计核心指标

在设计这些方案时,除了带宽,你必须在 VS Code 开发环境和硬件选型中关注以下四点:

-

静态功耗 (Quiescent Current):

-

痛点: SoC 的实时域功耗通常远高于分立 MCU。

-

指标: 需确保方案支持 冷启动唤醒 (Cold Boot) 且在休眠状态下整车电流 \< 10mA。E2B 由于硬件化程度高,在此项表现最优。

-

-

启动时序 (Boot Sequence):

-

要求: 汽车要求在点火启动后 100ms - 200ms 内发出第一条 CAN/以太网消息。

-

挑战: SoC 启动慢,因此 MCUless 方案需要 SoC 内部的 Safety Island (R52/R5F 核) 具备极速自启动能力,在 Linux 系统加载前就接管边缘通信。

-

-

确定性与同步性:

- 指标: 关注是否支持 gPTP (IEEE 802.1AS)。对于主动降噪(ANC)或动力电池采样,同步误差需控制在 \\mu s 级。

-

核间通信 (IPC) 与隔离:

- 软件架构: 在 SoC 内部,你需要配置共享内存机制,让负责逻辑的应用核(A 核)与负责 IO 的实时核(R 核)高效交换数据。