在SystemVerilog中always块细分为:always_ff、always_comb、always_latch三种,分别用于描述时序逻辑、组合逻辑、锁存器,与Verilog中的一个always替代所有不同,SystemVerilog的描述更加的精确细分。在实际编程中使用always_ff、always_comb可以通杀所有,但如果对自己有更高的要求,可以对三种形式进行区分对应使用。Verilog使用always@(*)描述组合逻辑。

1 always_ff块用法

1.1 always_ff块语法

always_ff块用于描述时序逻辑,其后需要跟敏感信号列表,并且敏感信号列表必须为边沿敏感型。

- 语法格式:

python

always_ff @ (sensitive signal list)

begin

statement1;

statement2;

............

end- 常用形式为:

always_ff @ (posedge <时钟信号>, negedge <复位信号>)

begin

语句块;

end

如:

python

always_ff@(posedge clk, negedge reset_n)

if(!reset_n)

time_send_en <= 1'b0;

else if(time_cnt[31:0] >= 32'd100)

time_send_en <= 1'b1;

else

time_send_en <= 1'b0;

always_ff@(posedge clk, negedge reset_n)

if(!reset_n)

sum <= 8'd0;

else if(sum_en)

sum <= a + b;

else

sum <= sum; // hold old value1.2 always_ff语法总结

(1) always_ff@后必须跟敏感信号列表,且敏感信号列表必须为边沿敏感型,可以是posedge、negedge,由于FPGA的结构,在使用时不能使用edge;

(2) always_ff与Verilog中的always一样,依然支持异步复位(negedge reset_n / posedge reset);

(3) 在always_ff中被赋值的变量,必须使用reg、logic型,不能使用wire型;

(4) always_ff中使用非阻塞赋值"<="给变量赋值;

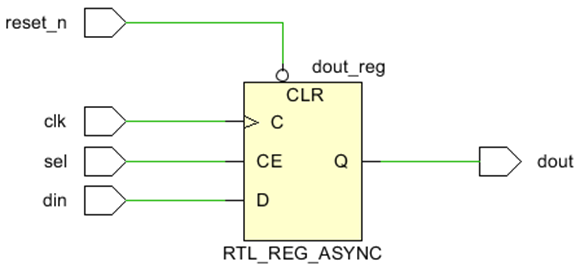

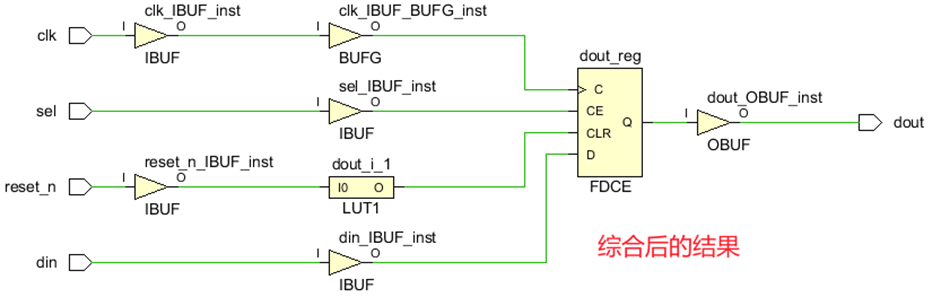

(5) always_ff中使用的条件控制语句(if、case),建议使用完整的条件分支语句,如果使用不完整的条件分支语句,则在综合的过程中,会产生带CE(clock enable)的寄存器,用于实现变量数值保持的功能,换而言之:也就是将自己的值赋值给本身,并不会生成Latch;如下代码以及综合后的结果:

python

always_ff@(posedge clk, negedge reset_n)

begin

if(!reset_n)

dout <= 4'd0;

else if(sel)

dout <= din;

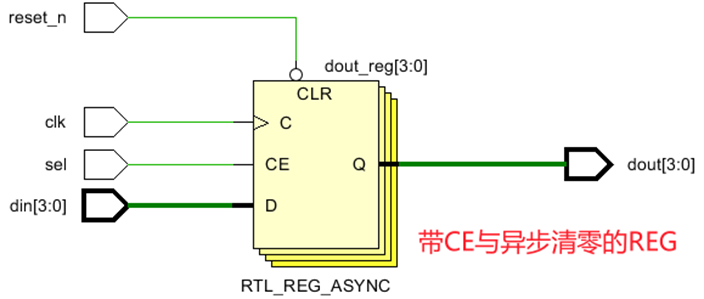

end(6) always_ff中允许使用将一个变量的值赋值给自己的写法,这种写法与不完全的条件分支综合后的效果是一样的,产生带时钟使能CE的寄存器,虽然综合后的效果是一样的,但是推荐在书写条件分支,一定要使用完整的分支语句。如下所示的代码与对应的综合、实现阶段的Schematic。

python

always_ff@(posedge clk, negedge reset_n)

begin

if(!reset_n)

dout <= 4'd0;

else if(sel)

dout <= din;

else

dout <= dout; // allow use hold language style

end对应的RTL分析、综合后的Schematic如下图所示:

!](https://i-blog.csdnimg.cn/direct/ea0e87e5aa414f44bff68ec55eaa30ef.png)