02计算机组成原理-Cache的替换算法及性能评估

前言

前两节我们讲了Cache的地址映射有关的内容,这节博客来讲述Cache的替换算法。

1.常见替换算法

在采用全相联映射或组相联映射方式时,从主存向Cache传送一 个新块,当Cache或Cache组中的空间已被占满时,就需要使用替换算法置换Cache行。

而采用直接映射时,一个给定的主存块只能放到唯一的固定Cache行中,所以在对应Cache行已有一个主存块的情况下,新的主存块毫无选择地把原先已有的那个主存块替换掉,因而无须考虑替换算法。

常用的替换算法有随机(RAND)算法、先进先出(FIFO)算法、近期最少使用(LRU)算法等等。其中最常用的是LRU算法。

1)随机算法:随机地确定替换的Cache行。它的实现比较简单,但未依据程序访问的局部性原理,因此可能命中率较低。

2)先进先出算法:选择最早调入的Cache 行进行替换。它比较容易实现,但也未依据程序访问的局部性原理,因为最早进入的主存块也可能是目前经常要用的。

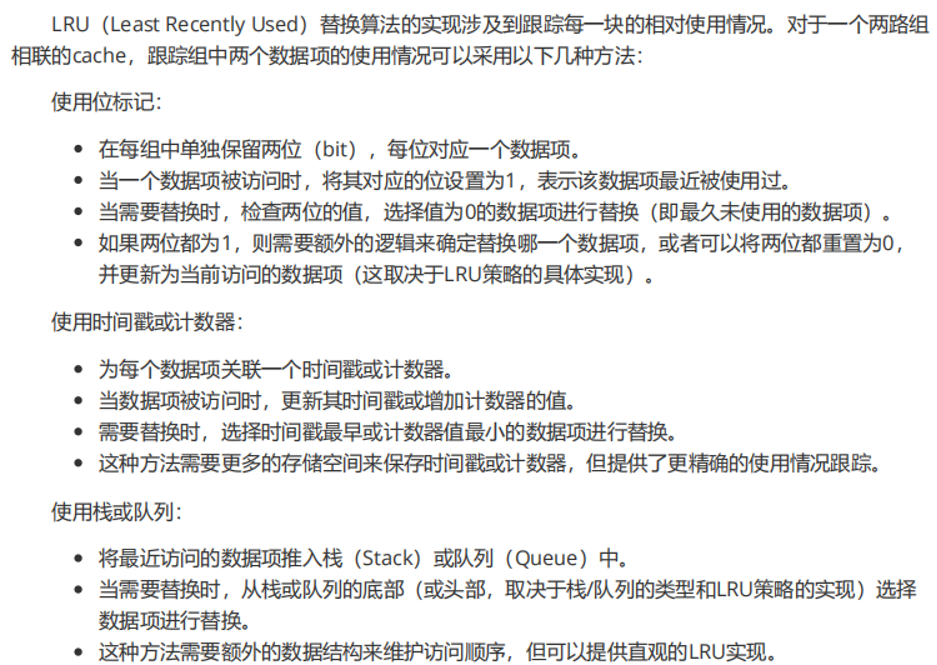

3)近期最少使用算法( LRU):依据程序访问的局部性原理,选择近期内长久未访问过的Cache行进行替换,是堆栈类算法。

2.LRU算法

这里就讲一下位标记了,因为408考这个。

LRU 是一种广泛使用的缓存替换策略,它基于这样的假设:最近最少使用的数据块在未来被再次使用的可能性最小。因此,当需要替换一个块时,LRU 策略会选择最久没有被访问过的块进行替换。

为每一个Cache行增加一个标记项,这个标记项叫LRU控制位,包含若干位,具体的位数取决于路数。(因为全相联也可以看成组相联)比如2n路组相联,LRU控制位有n位。

计数器变化规则:

(1)命中时,命中行的计数器清0,比命中行计数器值小的Cache行的计数器+1

(2)未命中时,Cache中有可以放入的空闲行,该空闲行放入新块,该行计数器置0,其他行计数器+1

(3)未命中时,Cache中没有可以放入的空闲行,选择计数器最大的行进行替换。替换后该行计数器置0,其他行计数器+1。

具体例子大家可以去网上寻找,我这里因为时间关系就不写例子了。

3.评估和分析Cache的性能

评估和分析 Cache 性能的方法:

1.缺失率(Miss Rate):缺失率是衡量cache性能的关键指标。它表示处理器尝试从cache中读取或写入数据时,由于数据不在cache中而导致的缺失次数与总访问次数的比率。缺失率越低,cache的性能越好。

2.缺失代价(Miss Penalty):缺失代价是指当cache缺失时,从主存中加载数据到cache所需的时间。这个时间包括等待主存响应的时间、数据传输时间和可能的cache更新时间。降低缺失代价是提高cache性能的重要手段。

3.命中率(Hit Rate):命中率是cache命中的次数与总访问次数的比率。命中率与缺失率之和为1。命中率越高,cache的性能越好。

4.平均访问时间(Average Access Time):平均访问时间是指处理器从cache或主存中获取数据所需的平均时间。它可以通过以下公式计算: 平均访问时间 = 命中率 × cache访问时间 + 缺失率 ×(cache访问时间 + 缺失代价) 。

两种改进cache性能的不同技术:降低缺失率

一些降低缺失率的技术:

1.增加cache容量:增加cache的容量可以存储更多的数据块,从而降低缺失率。但是,增加容量也会增加硬件成本和功耗。

2.改进替换策略:选择合适的替换策略,如最近最少使用(LRU)或最不经常使用(LFU),这两者都体现了局部性思想。可以提高cache的利用率和命中率。

3.增加关联度:提高cache的关联度(如从直接映射到组相联再到全相联)可以减少不同数据块争用同一cache位置的概率,从而降低缺失率。

4.预取技术:通过分析程序的行为,预测未来可能需要的数据块,并提前将其加载到cache中,以减少未来的缺失。

两种改进cache性能的不同技术:多级高速缓存

多级高速缓存通过在存储器层次结构中额外增加一层或多层来减少缺失代价。每一级cache都比下一级更快但容量更小。当数据在某一级cache中缺失时,处理器会尝试从下一级cache中获取数据。这种层次结构可以有效地减少缺失代价,因为较快的cache层级可以快速地响应缺失并提供数据。

多级高速缓存通常包括以下几级:

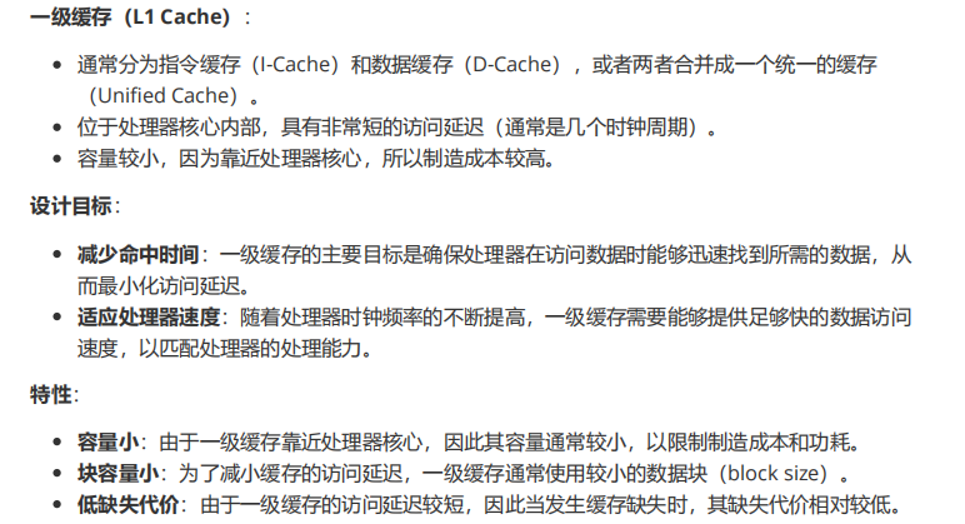

1.一级缓存(L1 Cache):最接近处理器的缓存层级,通常分为数据缓存(D-Cache)和指令缓存(I-Cache)。一级缓存的访问速度非常快,但容量有限。

2.二级缓存(L2 Cache):位于一级缓存和主存之间的缓存层级。二级缓存的容量通常比一级缓存大,但访问速度稍慢。

3.三级缓存(L3 Cache):在一些高性能处理器中,可能存在三级缓存。三级缓存的容量更大,但访问速度更慢。

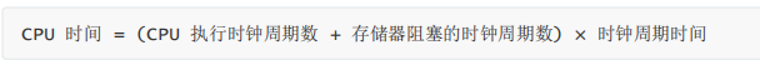

CPU 的时间可以被大致划分为两部分:一部分是 CPU 实际执行指令所花费的时钟周期数,另一部分是 CPU 等待存储系统(如 cache 或主存)响应所花费的时钟周期数。在评估系统性能时,理解并量化这两部分时间是非常重要的。

在理想情况下,我们假设 cache 访问命中的开销是 CPU 正常执行周期的一部分,这意味着当 CPU从 cache 中读取或写入数据时,其执行速度几乎与从寄存器中读写一样快。然而,当 cache 缺失时,CPU 必须等待从下一级存储层次(如主存)中检索数据,这通常会导致 CPU 阻塞(stall)或暂停执行,直到所需的数据到达 cache。

在简化的存储系统模型中,我们可以将 CPU 时间表示为:

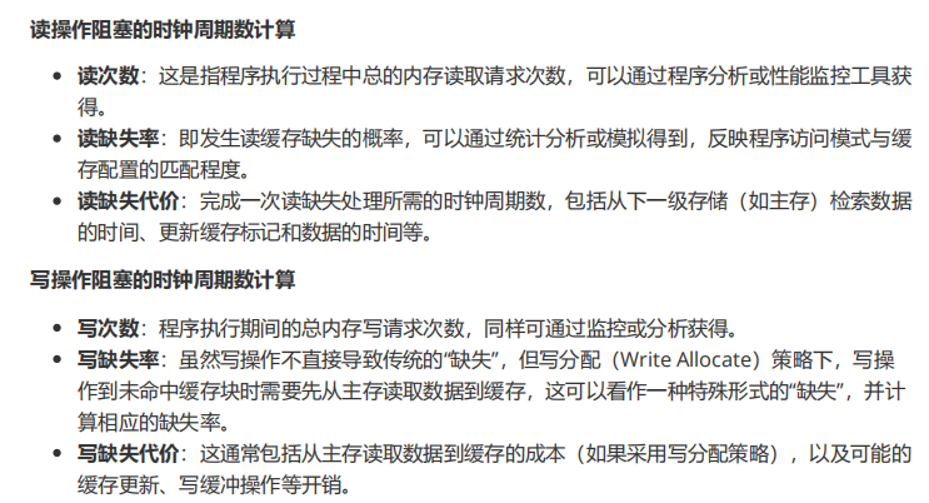

但在许多情况下,cache 缺失是存储器层次结构中导致 CPU 阻塞的主要因素。存储器阻塞的时钟周期数是由读操作和写操作两部分组成,而计算读操作阻塞时钟周期数的公式也很好地体现了性能分析中的关键参数。为了进一步完整理解,我们可以将读写操作的阻塞时钟周期数也纳入进来,形成一个全面的性能评估框架。

综合计算存储器阻塞的时钟周期数

平均一个程序存储器阻塞的时钟周期数

= 读操作阻塞的时钟周期数 + 写操作阻塞的时钟周期数

= [(读次数/程序数) × 读缺失率 × 读缺失代价] + [(写次数/程序数) × 写缺失相关成本]

请注意,这里的"写缺失相关成本"是一个更宽泛的概念,包括了写操作引起的各种延迟,比如在写回缓存中更新脏位、写缓冲的管理开销、以及实际写操作到主存的代价(尤其在写直达策略下)

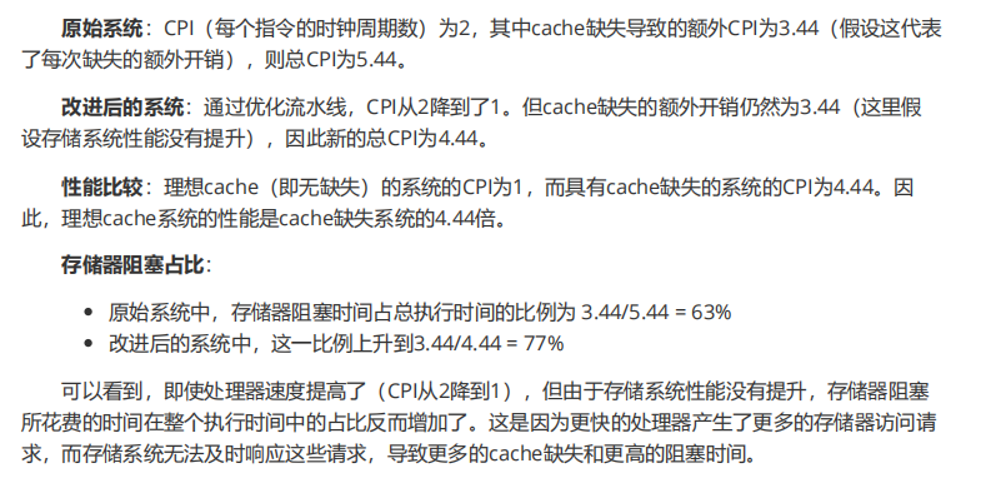

那如果处理器速度很快,而存储系统却不快,又会发生什么?

通过Amdahl定律的视角来观察这一问题。当处理器速度提升,而存储系统速度没有相应提升时,存储器访问延迟(尤其是缓存缺失导致的延迟)对系统性能的影响会更加显著。

Amdahl定律是由计算机科学家Gene Amdahl在1967年提出的,它是一个用于衡量并行计算效率的数学模型。该定律的核心思想是:在一个计算任务中,如果有一部分是无法并行化的,那么无论我们如何增加并行计算的资源,整个计算任务的加速比都会受到这部分无法并行化的限制。

我们来看一个例子:

可以看到,主要的原因为:

1、加速不均衡:处理器速度的提升减少了每条指令的执行时间(CPI降低),但没有缩短存储器访问时间。这意味着在程序执行过程中,存储器访问(特别是缓存缺失)所占的时间比例显著增加,成为更大的性能瓶颈。

2、性能提升受限:即使处理器性能大幅提升,如果存储系统未能跟上,整体性能提升将受到极大限制。即使CPI从2降到了1,但由于缓存缺失率和缺失代价没有改善,系统性能的绝对提升并不显著,理想缓存配置与非理想配置的性能差距依然保持在4.44倍,但存储器阻塞时间占比却从63%增加到了77%。

3、频率提升的局限性:单纯提高处理器时钟频率而不改善存储系统性能,实际上可能加剧这一问题。更高的频率意味着处理器在单位时间内发出的存储请求更多,如果存储系统响应速度不变,缓存缺失率可能因此增加,进一步拉低整体性能提升的效率。

综上所述,处理器与存储系统的协同进化是提升系统整体性能的关键,特别是在高性能计算和大数据处理领域,存储系统的发展不应滞后于处理器的进步。

前面的例子和等式是建立在命中时间不计入计算 cache 性能的假设之上。如果命中时间增加,那么从存储系统中存取一个字的总时间也会增加,继而导致处理器时钟周期的增加。

为了更准确地评估cache设计的性能,设计人员会使用平均存储器访问时间(AMAT)这一指标。AMAT综合考虑了命中、缺失以及不同访问的频率,能够更全面地反映cache设计的实际效果。

AMAT的计算公式为:AMAT = 命中时间 + 缺失率 × 缺失代价。其中,命中时间是从cache中读取数据所需的时间,缺失率是数据在cache中未命中的概率,缺失代价是当数据在cache中未命中时从主存中读取数据所需的时间。

大家复习408的话主要看替换策略和记那个平均访问时间的公式就行了。其余可以了解。

4.多级Cache的设计

现代计算机系统中广泛使用多级缓存结构来减少处理器和主存(通常是DRAM)之间的性能差距。随着处理器时钟频率的不断提高和DRAM访问延迟的相对增加,这种差距变得越来越大。为了缓解这个问题,大多数现代微处理器都采用了多级缓存架构。

多级缓存的工作原理:

- 当处理器需要读取或写入数据时,它首先会在L1 Cache中查找。

- 如果L1 Cache中找到了所需的数据(缓存命中),则处理器会立即使用该数据,从而避免了访问主存的延迟。

- 如果L1 Cache中没有找到所需的数据(缓存缺失),处理器会检查L2 Cache。

- 如果L2 Cache中找到了数据(二级缓存命中),则处理器会使用该数据,但访问延迟会比L1Cache稍长。

- 如果L2 Cache中也没有找到数据(二级缓存缺失),则处理器必须访问主存(DRAM),这会产生更大的延迟。

缓存的替换策略:

当新的数据需要被缓存,而缓存已满时,就需要使用某种替换策略来决定哪些数据应该被替换出去。LRU(最近最少使用)替换策略是一种常用的方法。后续操作系统课会讲。

缓存的影响:

多级缓存结构可以显著提高处理器的性能,因为它减少了处理器等待数据从主存中加载的时间。然而,缓存的引入也增加了系统的复杂性和成本,因为需要额外的硬件来存储和管理缓存数据。

5.分块算法

这个408不考,大家可以当科普理解一下就可以了。

分块算法(Blocking or Tiling)是一种有效的软件优化技术,尤其适用于处理多维数组,如在科学计算、图像处理和矩阵运算等领域。该技术通过改变数据访问模式,提高了缓存的利用效率,从而显著提升了程序性能。下面是分块算法的基本思想及其如何提升缓存性能的详细解释:

通常应用于行列混合访问。

对于那些既要按行访问又要按列访问的多数组操作,传统的按行或按列存储方式往往不能充分利用缓存,因为每次访问可能跨越多个缓存行,导致频繁的缓存缺失。分块算法通过以下方式解决这一问题:

交错访问:通过将数据组织成块,可以在一个循环迭代中集中访问一个块内的行数据,下一个迭代则集中访问同一块内的列数据,或者交错访问不同块的行/列数据,从而在缓存中形成连续的访问模式。

预取策略:结合预取技术,可以在处理当前块的同时,预取下一个即将访问的块到缓存中,进一步减少等待时间。

Cache到这就结束了,下节博客讲主存储器。Cache这里需要掌握,基本原理,数据查找,地址映射,替换策略和写入策略。大概先写这些吧,今天的博客就先写到这,谢谢您的观看。