Cadence Allegro 17.4的neck模式走线

- [Chapter1 Cadence Allegro 17.4的neck模式(瓶颈模式)走线](#Chapter1 Cadence Allegro 17.4的neck模式(瓶颈模式)走线)

Chapter1 Cadence Allegro 17.4的neck模式(瓶颈模式)走线

原文链接:https://blog.csdn.net/weixin_44479192/article/details/132427406

在某些场景下,LQFP/BGA封装下密度比较大,走线的线宽可能不一致,当我们只设置另外一种走线线宽时,出现更细的走线会报错,而大多出的走线都是粗一些的,那么可以利用allegro的瓶颈走线模式来走线。

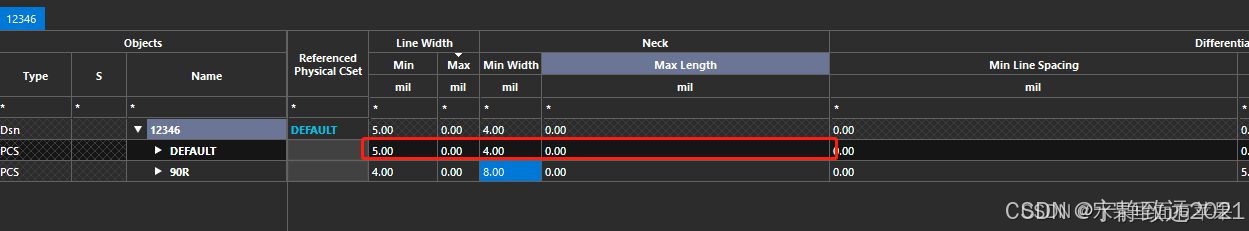

首先打开规则管理器的物理规则设置,设置线宽最小是5mil ,第二线宽时4mil。

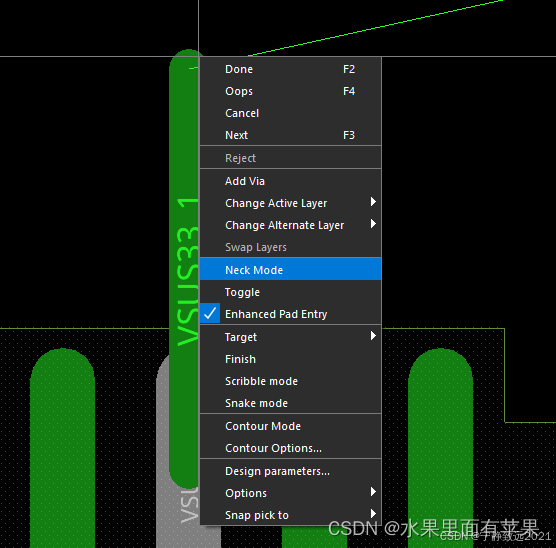

回到PCB设计界面,当走线走到需要缩小线宽的地方时,选择Neck Mode模式走线即可。

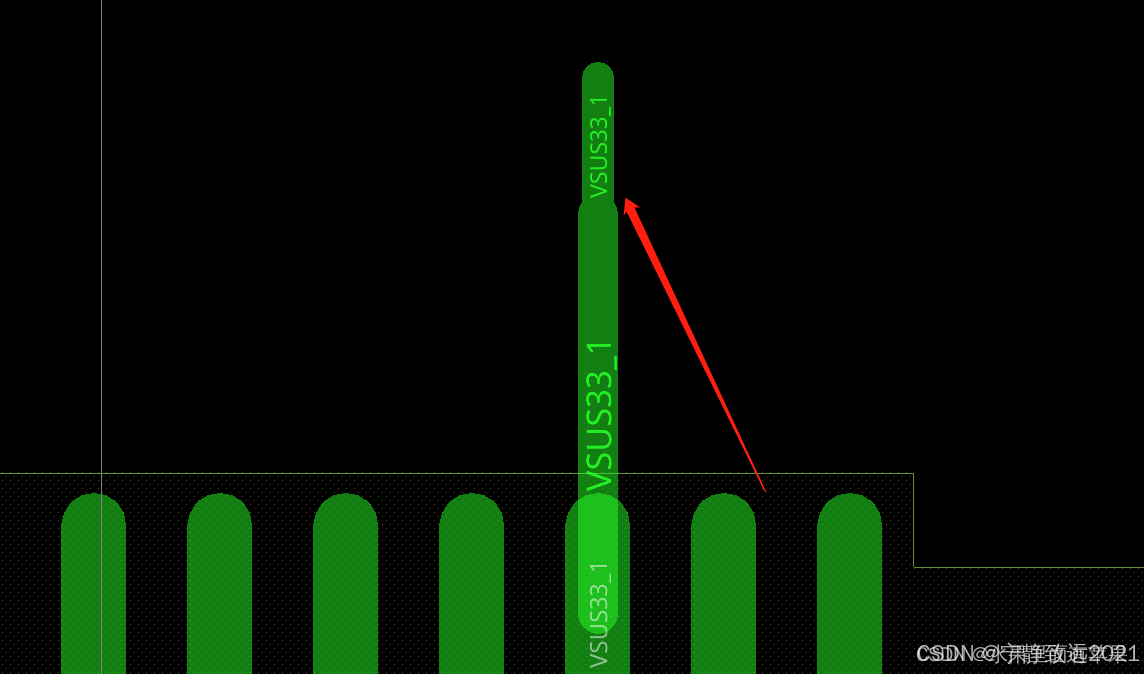

效果图如下

在Cadence Allegro 17.4中,neck模式(颈缩模式)是一种重要的高速布线功能,专门用于解决高密度PCB设计中的空间限制问题。

一、Neck模式的核心含义

Neck模式是一种走线临时变细的控制模式,允许在受限区域(如焊盘、BGA、过孔之间)通过狭窄通道出线,同时不破坏整体规则体系。它本质上是在特定区域临时采用比常规更细的线宽,以绕过障碍物或完成扇出操作。

二、关键参数设置详解

- 单端线Neck参数

在Physical Constraint Set中设置:

Neck Width:neck模式下的最小线宽(如从5mil临时变为4mil)

Max Neck Length:允许neck走线的最大长度,防止过长的窄线段影响信号质量

- 差分对Neck相关参数(在Electrical Constraint Set中)

Primary Gap:差分对两根线之间的默认间距(边到边间距)

Neck Gap:neck mode模式下差分线的间距,用于布线密集区域

Neck Width:neck模式下的差分线宽

Min Line Spacing:差分对内两线的最小间距,此值要比neck gap小

Tolerance:允许的间距偏差,确保实际走线时不会因微小偏差而报DRC错误

三、具体操作设置步骤

- 规则设置阶段

打开约束管理器:Setup → Constraints → Constraints Manager

进入Physical Constraint Set → All layers

在Neck列设置:最小neck线宽和最大neck长度

对于差分线:进入Electrical Constraint Set → Differential Pair,设置Neck Width和Neck Gap等参数

- 布线操作阶段

在PCB设计界面开始布线(Add Connect)

当走到需要缩小线宽的区域时,点击鼠标右键 → 选择Neck Mode

线宽会自动切换到预设的neck宽度

通过狭窄区域后,再次右键取消Neck Mode,恢复常规线宽

- 快捷键设置(可选)

在env文件中添加:funckey n pop neck,这样在走线时按n键即可快速切换neck模式。

四、主要应用场景

- BGA封装高密度区域

BGA芯片下方引脚密集,正常线宽无法通过焊盘间隙时,使用neck模式临时缩小线宽完成扇出。

- 差分线换层过渡

当差分对需要换层连接不同层的引脚时,在换层区域使用neck模式缩小线宽,便于放置过孔并保持信号连续性。

- 焊盘连接优化

连接焊盘时采用neck走线减小线宽,可以降低热容量,避免焊接时出现虚焊或冷焊现象。

- 阻抗匹配调整

在高速信号线路中,通过精心设计的neck区域可以实现局部阻抗匹配,减少阻抗不连续性带来的反射和干扰。

- 过孔阵列穿越

在密集的过孔阵列中,正常线宽无法通过时,使用neck模式临时变细以穿越狭窄通道。

五、注意事项

长度控制:neck区域应尽量缩短,通常建议小于100mil,以减小阻抗变化的影响

阻抗连续性:neck模式会改变阻抗,需通过仿真工具(如SigXplorer)验证阻抗变化是否可接受

渐变过渡:在进入和退出neck区域时建议进行渐变过渡,避免阻抗突变

DRC协调:确保Min Line Spacing ≤ Neck Gap - Tolerance,避免不必要的DRC报错

neck模式特别适合处理局部、临时性的空间限制问题,而区域规则更适合大面积、固定区域的差异化约束。

通过合理使用neck模式,可以在不牺牲信号完整性的前提下,有效解决高密度PCB设计中的布线难题,特别是在现代高速电路设计中具有重要实用价值。