文章目录

- 一、串口功能框图

- 二、功能引脚

-

- [ 1、引脚说明](# 1、引脚说明)

- [ 2、STM32F103ZET6芯片具体分布](# 2、STM32F103ZET6芯片具体分布)

- 三、数据寄存器

-

- [ 1、数据长度](# 1、数据长度)

- [ 2、接收数据寄存器、发送数据寄存器](# 2、接收数据寄存器、发送数据寄存器)

- [ 3、移位寄存器](# 3、移位寄存器)

- 四、控制器

-

- [ 1、控制器](# 1、控制器)

- [ 2、发送器](# 2、发送器)

- [ 3、接收器](# 3、接收器)

- 五、波特率

- 六、校验控制

- 七、中断控制

- 八、USART相关结构体详解

-

- [ 1、USART初始化结构体](# 1、USART初始化结构体)

- [ 2、USART时钟初始化结构体](# 2、USART时钟初始化结构体)

- [ 3、编程时需要用到的固件库函数](# 3、编程时需要用到的固件库函数)

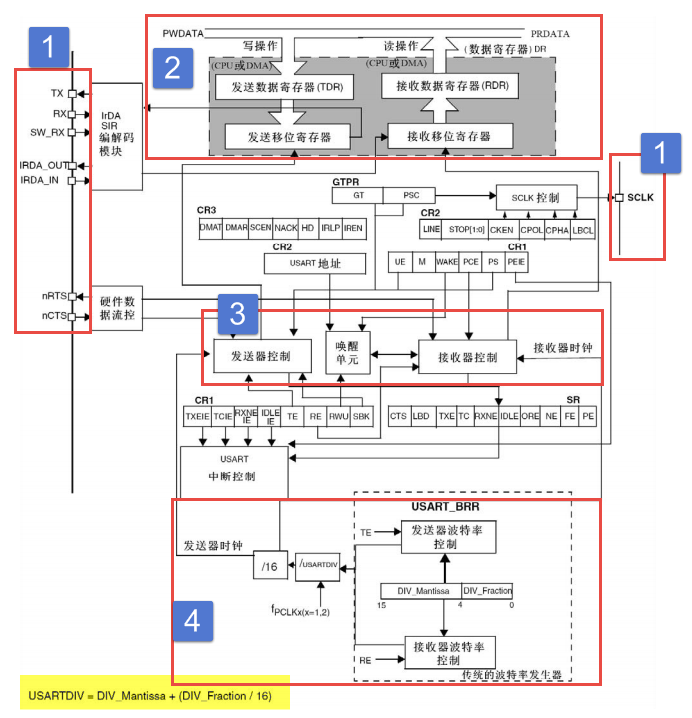

一、串口功能框图

通用同步异步收发器(Universal Synchronous Asynchronous Receiver and Transmitter)是一个串行通信设备, 可以灵活地与外部设备进行全双工数据交换。

二、功能引脚

1、引脚说明

TX: 发送数据输出引脚。

RX: 接收数据输入引脚。

SW_RX: 数据接收引脚,只用于单线和智能卡模式,属于内部引脚,没有具体外部引脚。

nRTS: 请求以发送(Request To Send),n表示低电平有效。如果使能RTS流控制,当USART接收器准备好接收新数据时就会将nRTS变成低电平; 当接收寄存器已满时,nRTS将被设置为高电平。该引脚只适用于硬件流控制。

nCTS: 清除以发送(Clear To Send),n表示低电平有效。如果使能CTS流控制,发送器在发送下一帧数据之前会检测nCTS引脚, 如果为低电平,表示可以发送数据,如果为高电平则在发送完当前数据帧之后停止发送。该引脚只适用于硬件流控制。

SCLK: 发送器时钟输出引脚。这个引脚仅适用于同步模式。

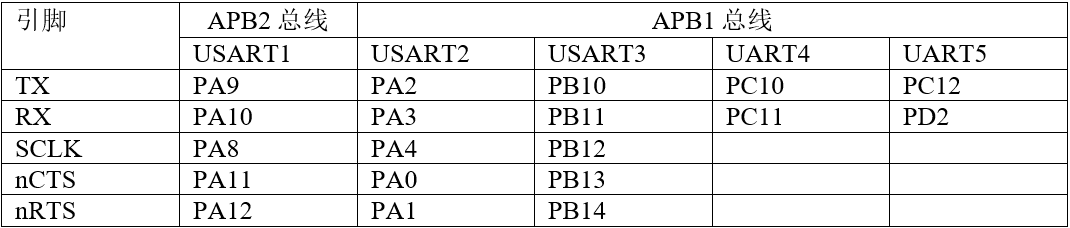

2、STM32F103ZET6芯片具体分布

其中USART1和时钟来源于APB2总线时钟,其最大频率为72MHz, 其他四个的时钟来源于APB1总线时钟,其最大频率为36MHz。编程时注意。

三、数据寄存器

1、数据长度

USART数据寄存器(USART_DR)只有低9位有效,并且第9位数据是否有效要取决于USART控制寄存器1(USART_CR1)的M位设置, 当M位为0时表示8位数据字长,当M位为1表示9位数据字长,我们一般使用8位数据字长。

2、接收数据寄存器、发送数据寄存器

USART_DR包含了已发送的数据或者接收到的数据。

USART_DR实际是包含了两个寄存器,一个专门用于发送的可写TDR, 一个专门用于接收的可读RDR。

当进行发送操作时,往USART_DR写入数据会自动存储在TDR内;

当进行读取操作时,向USART_DR读取数据会自动提取RDR数据。

3、移位寄存器

TDR和RDR都是介于系统总线和移位寄存器之间。

串行通信是一个位一个位传输的。

发送时把TDR内容转移到发送移位寄存器, 然后把移位寄存器数据每一位发送出去;

接收时把接收到的每一位顺序保存在接收移位寄存器内然后才转移到RDR。

四、控制器

1、控制器

USART有专门控制发送的发送器、控制接收的接收器,还有唤醒单元、中断控制等等。

使用USART之前需要向USART_CR1寄存器的UE位置1使能USART,UE位用来开启供给给串口的时钟。

发送或者接收数据字长可选8位或9位,由USART_CR1的M位控制。

2、发送器

当USART_CR1寄存器的发送使能位TE置1时,启动数据发送,发送移位寄存器的数据会在TX引脚输出, 低位在前,高位在后。如果是同步模式SCLK也输出时钟信号。

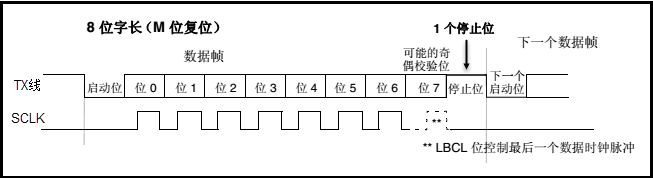

一个字符帧发送需要三个部分:起始位+数据帧+停止位。起始位是一个位周期的低电平,位周期就是每一位占用的时间; 数据帧就是我们要发送的8位或9位数据,数据是从最低位开始传输的;停止位是一定时间周期的高电平。

停止位时间长短是可以通过USART控制寄存器2(USART_CR2)的STOP[1:0]位控制,可选0.5个、1个、1.5个和2个停止位。 默认使用1个停止位。2个停止位适用于正常USART模式、单线模式和调制解调器模式。0.5个和1.5个停止位用于智能卡模式。

当选择8位字长,使用1个停止位时,字符发送时序图:

当发送使能位TE置1之后,发送器开始会先发送一个空闲帧(一个数据帧长度的高电平),接下来就可以往USART_DR寄存器写入要发送的数据。

在写入最后一个数据后,需要等待USART状态寄存器(USART_SR)的TC位为1,表示数据传输完成,如果USART_CR1寄存器的TCIE位置1,将产生中断。

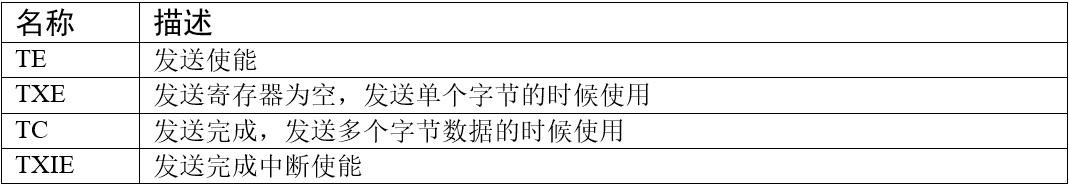

发送数据时,重要标志位总结:

3、接收器

将USART_CR1寄存器的RE位置1,使能USART接收,使得接收器在RX线开始搜索起始位。

在确定到起始位后就根据RX线电平状态把数据存放在接收移位寄存器内。

接收完成后就把接收移位寄存器数据移到RDR内, 并把USART_SR寄存器的RXNE位置1,同时如果USART_CR2寄存器的RXNEIE置1的话可以产生中断。

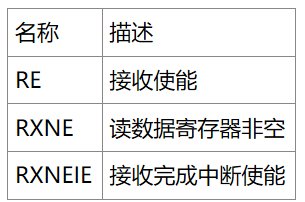

接收数据时,重要标志位总结:

五、波特率

波特率指数据信号对载波的调制速率,它用单位时间内载波调制状态改变次数来表示,单位为波特。

比特率指单位时间内传输的比特数,单位bit/s(bps)。

波特率越大,传输速率越快。

USART的发送器和接收器使用相同的波特率。

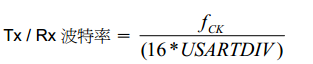

计算公式如下:

其中,fPLCK为USART时钟, USARTDIV是一个存放在波特率寄存器(USART_BRR)的一个无符号定点数。

其中DIV_Mantissa[11:0]位定义USARTDIV的整数部分,DIV_Fraction[3:0]位定义USARTDIV的小数部分。

六、校验控制

STM32F103系列控制器USART支持奇偶校验。

当使用校验位时,串口传输的长度将是8位的数据帧加上1位的校验位总共9位,

此时USART_CR1寄存器的M位需要设置为1,即9数据位。

将USART_CR1寄存器的PCE位置1就可以启动奇偶校验控制, 奇偶校验由硬件自动完成。

启动了奇偶校验控制之后,在发送数据帧时会自动添加校验位,接收数据时自动验证校验位。

接收数据时如果出现奇偶校验位验证失败,会见USART_SR寄存器的PE位置1,并可以产生奇偶校验中断。

使能了奇偶校验控制后,每个字符帧的格式将变成:起始位+数据帧+校验位+停止位。

七、中断控制

USART有多个中断请求事件。

八、USART相关结构体详解

1、USART初始化结构体

c

typedef struct {

uint32_t USART_BaudRate; // 波特率

uint16_t USART_WordLength; // 字长

uint16_t USART_StopBits; // 停止位

uint16_t USART_Parity; // 校验位

uint16_t USART_Mode; // USART模式

uint16_t USART_HardwareFlowControl; // 硬件流控制

} USART_InitTypeDef;1) USART_BaudRate:

波特率设置。一般设置为2400、9600、19200、115200。标准库函数会根据设定值计算得到USARTDIV值,从而设置USART_BRR寄存器值。

2) USART_WordLength:

数据帧字长,可选8位或9位。它设定USART_CR1寄存器的M位的值。如果没有使能奇偶校验控制,一般使用8数据位;如果使能了奇偶校验则一般设置为9数据位。

3) USART_StopBits:

停止位设置,可选0.5个、1个、1.5个和2个停止位,它设定USART_CR2寄存器的STOP[1:0]位的值,一般我们选择1个停止位。

4) USART_Parity:

奇偶校验控制选择,可选USART_Parity_No(无校验)、USART_Parity_Even(偶校验)以及USART_Parity_Odd(奇校验),它设定USART_CR1寄存器的PCE位和PS位的值。

5) USART_Mode:

USART模式选择,有USART_Mode_Rx和USART_Mode_Tx,允许使用逻辑或运算选择两个,它设定USART_CR1寄存器的RE位和TE位。

6) USART_HardwareFlowControl:

硬件流控制选择,只有在硬件流控制模式才有效,可选有使能RTS、使能CTS、同时使能RTS和CTS、不使能硬件流。

当使用同步模式时需要配置SCLK引脚输出脉冲的属性,标准库使用一个时钟初始化结构体USART_ClockInitTypeDef来设置,该结构体内容也只有在同步模式才需要设置。

2、USART时钟初始化结构体

c

typedef struct {

uint16_t USART_Clock; // 时钟使能控制

uint16_t USART_CPOL; // 时钟极性

uint16_t USART_CPHA; // 时钟相位

uint16_t USART_LastBit; // 最尾位时钟脉冲

} USART_ClockInitTypeDef;1) USART_Clock:

同步模式下SCLK引脚上时钟输出使能控制,可选禁止时钟输出(USART_Clock_Disable)或开启时钟输出(USART_Clock_Enable);如果使用同步模式发送,一般都需要开启时钟。它设定USART_CR2寄存器的CLKEN位的值。

2) USART_CPOL:

同步模式下SCLK引脚上输出时钟极性设置,可设置在空闲时SCLK引脚为低电平(USART_CPOL_Low)或高电平(USART_CPOL_High)。它设定USART_CR2寄存器的CPOL位的值。

3) USART_CPHA:

同步模式下SCLK引脚上输出时钟相位设置,可设置在时钟第一个变化沿捕获数据(USART_CPHA_1Edge)或在时钟第二个变化沿捕获数据。它设定USART_CR2寄存器的CPHA位的值。USART_CPHA与USART_CPOL配合使用可以获得多种模式时钟关系。

4) USART_LastBit:

选择在发送最后一个数据位的时候时钟脉冲是否在SCLK引脚输出,可以是不输出脉冲(USART_LastBit_Disable)、输出脉冲(USART_LastBit_Enable)。它设定USART_CR2寄存器的LBCL位的值。

3、编程时需要用到的固件库函数

1) 串口初始化函数

void USART_Init(USART_TypeDef* USARTx, USART_InitTypeDef* USART_InitStruct)

2) 中断配置函数

void USART_ITConfig(USART_TypeDef* USARTx, uint16_t USART_IT, FunctionalState NewState)

3) 串口使能函数

void USART_Cmd(USART_TypeDef* USARTx, FunctionalState NewState)

4) 数据发送函数

void USART_SendData(USART_TypeDef* USARTx, uint16_t Data)

5) 数据接收函数

uint16_t USART_ReceiveData(USART_TypeDef* USARTx)

6) 中断状态位获取函数

ITStatus USART_GetITStatus(USART_TypeDef* USARTx, uint16_t USART_IT)