MPU简介

-

MPU 是 Memory Protection Unit (内存保护单元)是现代微控制器(如 STM32H7 的 Cortex-M7 内核)中内置的一个硬件模块,主要作用是监控和管理 CPU 对内存的访问行为 :

- 防止程序"越界" (Access Violation):CPU 尝试写入的瞬间,MPU 发现地址越界,立即阻断操作 并触发

MemManage Fault。程序立刻停在出错的那一行,开发者可以马上知道哪里错了。 - 隔离用户模式与特权模式 (Privilege Levels):操作系统内核(特权模式)和应用程序任务(用户模式)。MPU 可以配置某些关键区域(如内核堆栈、外设寄存器)只允许特权模式访问。如果用户模式的代码试图修改这些区域,MPU 会直接报错。这防止了劣质应用搞崩整个系统。

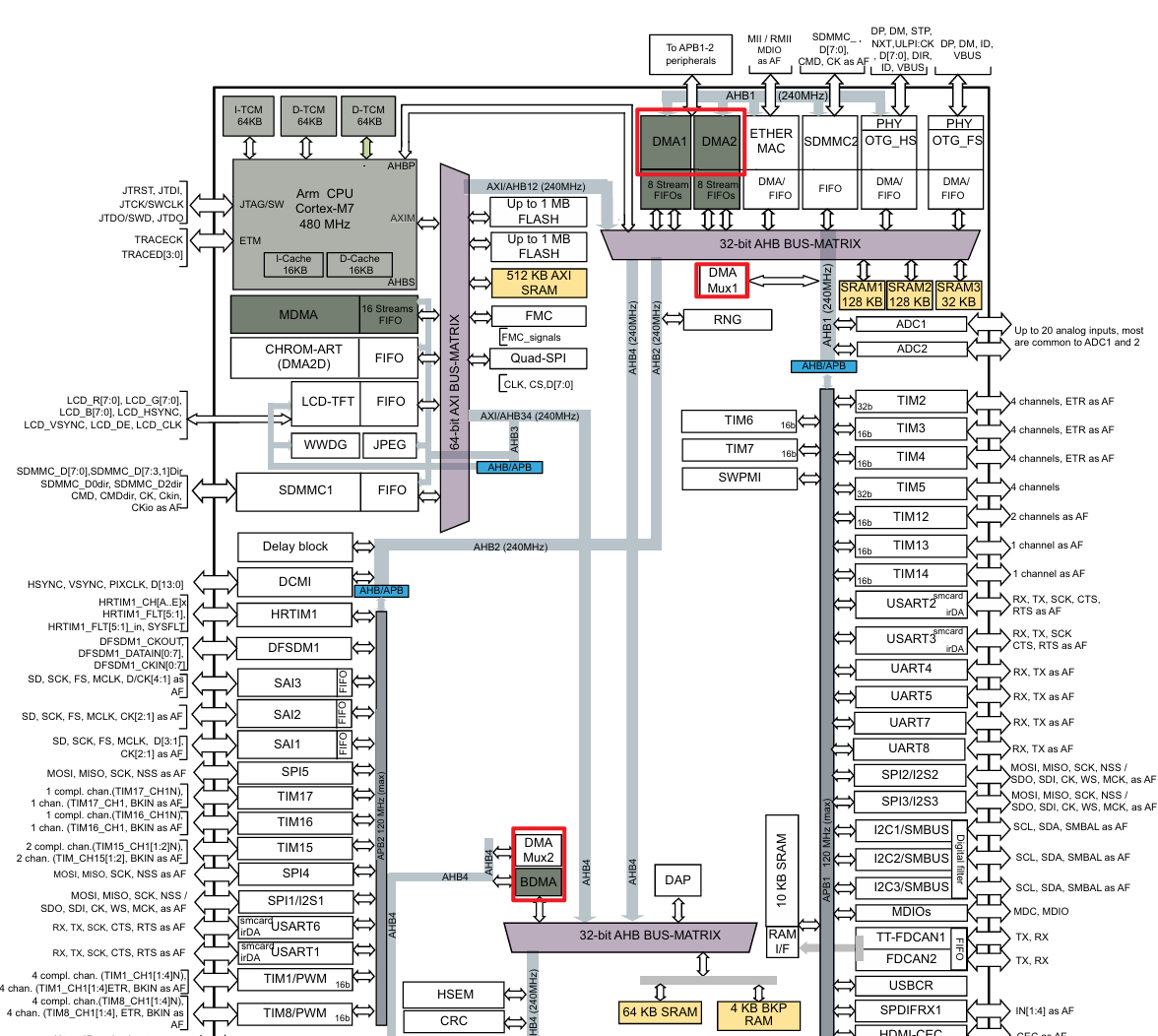

- 控制缓存策略 (Cache Control) :DMA 控制器直接向内存写数据(如 ADC 采样值),而 CPU 开启了 Cache。CPU 可能从 Cache 里读到旧数据,因为 DMA 绕过了 Cache 直接改了内存。通过配置 MPU,可以将 DMA 使用的缓冲区标记为 "不可缓存 (Non-Cachable)"。这样 CPU 访问该区域时会强制绕过 Cache,直接读物理内存,保证数据一致性,无需软件手动刷新 Cache。

- 定义内存属性 (Memory Attributes):MPU 可以告诉 CPU 某块内存是什么类型的: Normal Memory 、 Device Memory 、 Strongly Ordered。

- 防止程序"越界" (Access Violation):CPU 尝试写入的瞬间,MPU 发现地址越界,立即阻断操作 并触发

M7内核上的数据缓存结构

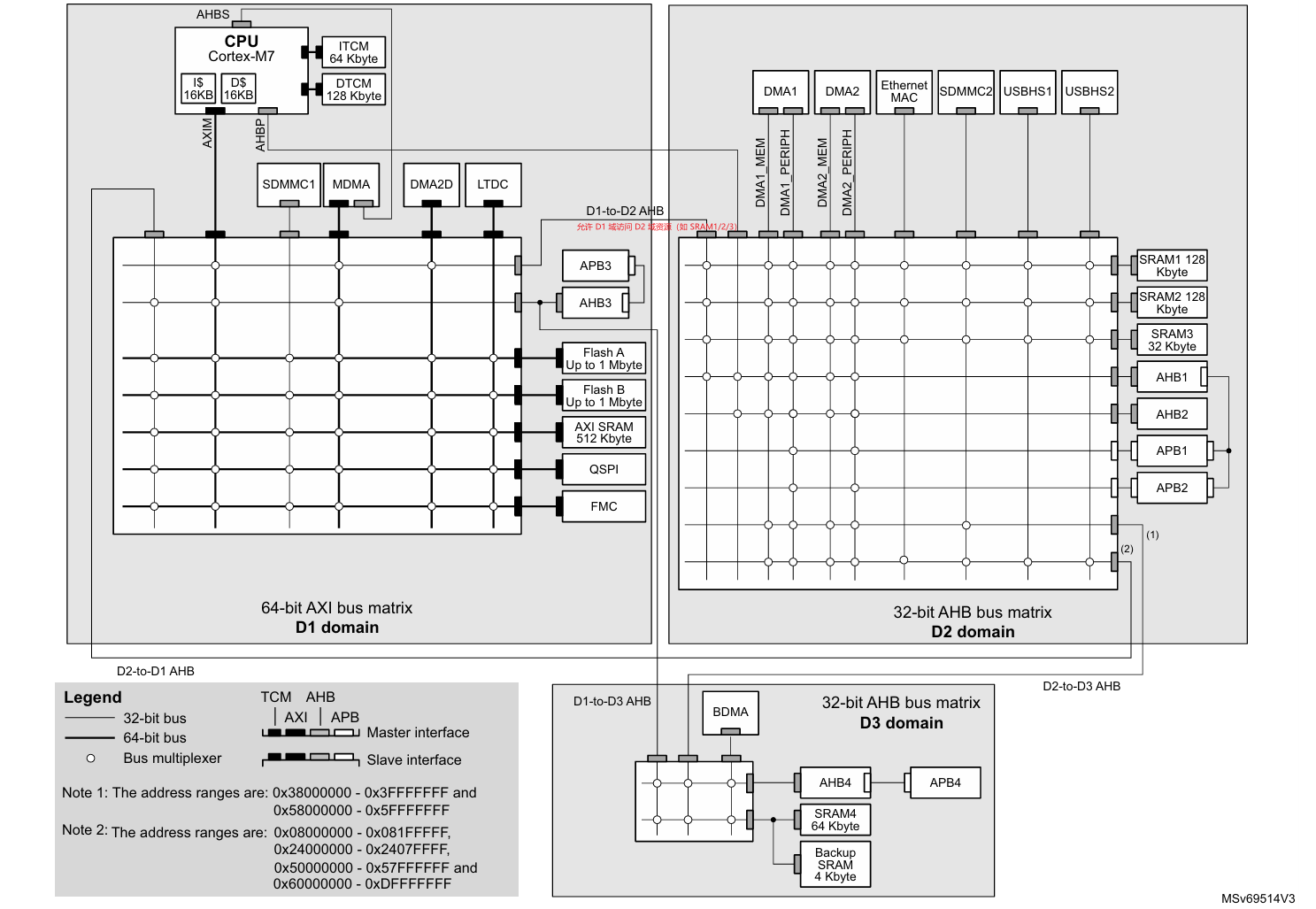

- DMA与DTCM总线拓扑隔离(物理上不链接):

- 哈佛架构的极致化:Cortex-M7 采用改进的哈佛架构。ITCM 和 DTCM 是通过 CPU 内部的专用端口(Private Ports)直接连接的,不经过片上总线矩阵(Bus Matrix)。是直接挂在CPU上的高速内存不经过 Cache访问速度接近单周期,访问时间固定。

- 零等待周期(0 Wait State):为了让 CPU 在每个时钟周期都能确定性地读写数据,TCM 必须避开总线仲裁、冲突和延迟。如果允许 DMA 访问,就需要引入复杂的仲裁机制,这会破坏 TCM 的"确定性"和"高速"特性。

- DMA 的路径 :DMA 控制器是挂在 AXI 或 AHB 总线上的主设备(Master)。它只能看到挂载在这些总线上的从设备(Slave),比如 SRAM1/2/3、AXI SRAM、Flash 等。TCM 不在这些总线的地址映射范围内。

- D-Cache 需要重点管理(涉及数据一致性) ,I-Cache 多用于加速,一般较少手动干预 。DMA 写不了 DTCM 是因为路不通 (硬件架构限制);需要维护 Cache 是因为信息不同步 (DMA 直接改内存,得通知 CPU 刷新)。

简化结构

CPU

Cache

SRAM

DMA

结构 + 操作融合

Enable

Disable

Clean 写回

Invalidate 失效

CPU

Cache

SRAM

DMA

Cache 四种基本操作

| 操作 | 作用 | 影响对象 | 是否影响内存 | 典型使用场景 | 关键特点 |

|---|---|---|---|---|---|

| 使能(Enable) | 打开 Cache 功能 | I-Cache / D-Cache | 否 | 系统初始化时开启 | 提升访问速度 |

| 禁止(Disable) | 关闭 Cache 功能 | I-Cache / D-Cache | 否 | 调试 / 特殊一致性需求 | 简单但性能下降 |

| 清空(Clean) | 将缓存中的脏数据写回内存 | 仅 D-Cache | 是(写回) | CPU写数据 → DMA读取前 | 保证内存数据最新 |

| 无效化(Invalidate) | 丢弃缓存中的数据 | I-Cache / D-Cache | 否 | DMA写数据 → CPU读取前 | 强制重新从内存读取 |

- Clean ≈ 同步数据到内存(写回)

- Invalidate ≈ 丢掉缓存重新读取

Cache&DMA 时序图

DMA SRAM Cache CPU DMA SRAM Cache CPU 可能读到旧数据,需要 Clean ---------------------------- Cache未更新,需要 Invalidate 写数据 未及时写回 读取数据 写数据 读取数据 返回旧数据