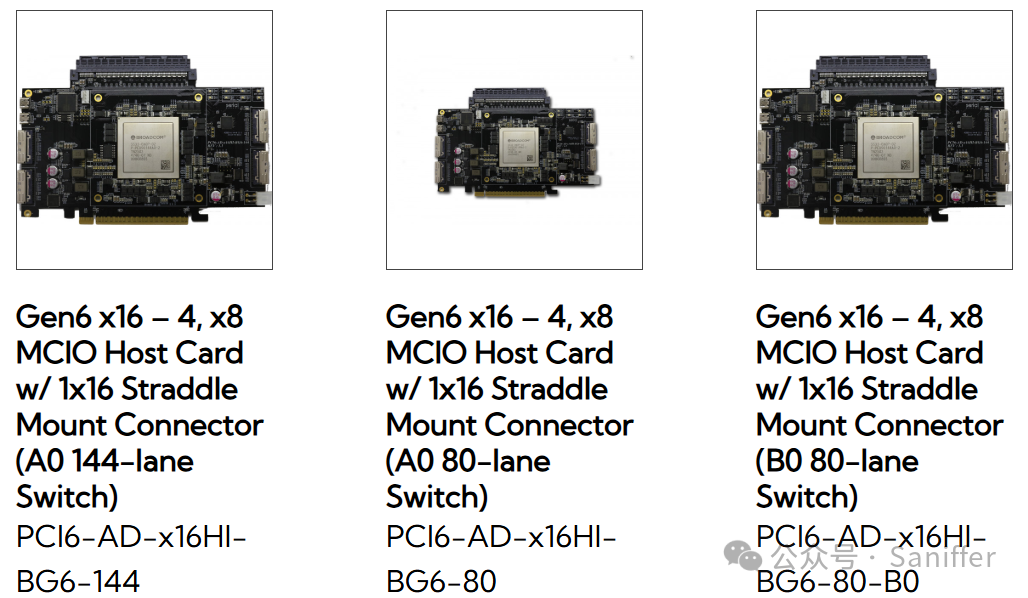

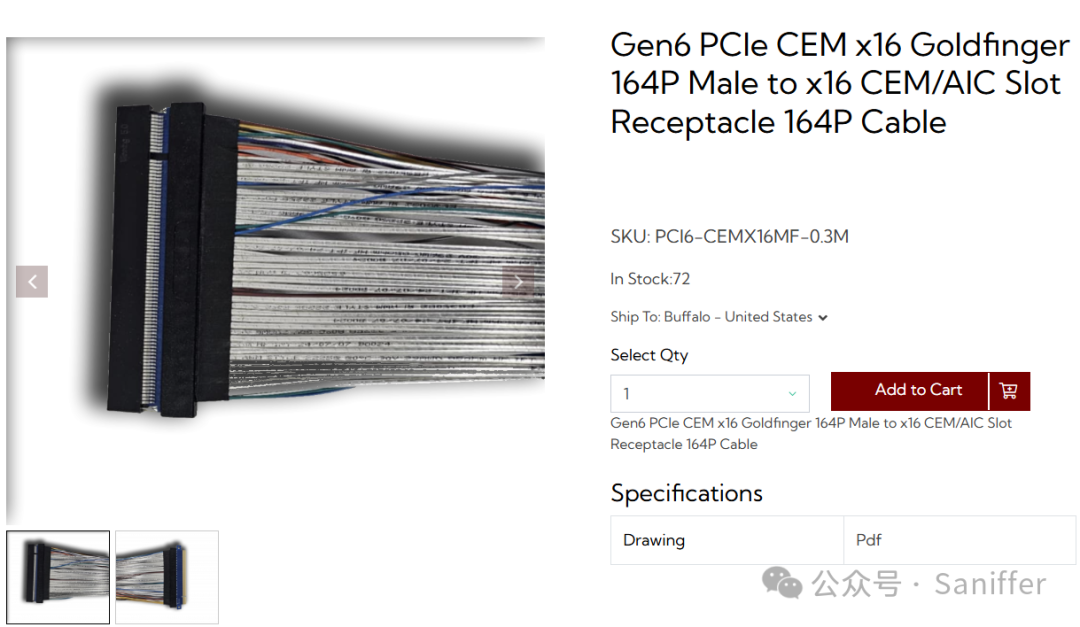

我们知道,在未来1-2年还是无法拿到任何PCIe 6.0的服务器和工作站,那么在实验室搭建PCIe 6.0测试环境测试各类PCIe 6.0 EP (end point)的过程中,一方面处于模拟一个PCIe 6.0 CPU (RC - root complex)我们需要PCIe 6.0 switch卡,我们这方面在saniffer 公号拍摄了大量高清视频做了演示,可以加 saniffer 公号后查询关键词"PCIe 6.0 switch"即可,也需要具备PCIe 6.0 信号品质的延长线,参见下面的图片,我们也在saniffer 公号做了两个Gen6 switch卡之间串接这根0.3米延长线的演示。但是有的时候需要延长更长距离,例如1米或者2米,但是又不希望信号出现大的问题,咋办呢?这个就是今天我们的主题,来介绍一下我们即将发布的基于业内主流芯片,包括Credo和Marvell的PCIe 6.0 retimer卡。

PCIe 6.0 switch卡和延长线,0.3米

【高清视频】实验室搭建PCIe 6.0测试环境需要的retimer卡介绍

下面是针对上述视频的一个文字总结,供快速阅读使用。

一、演示系统结构与验证目标

视频展示的是一个典型的PCIe 6.0链路验证环境,其整体结构如下:

-

• 主机侧:PCIe Gen5 主板 (**目前没有PCIe 6.0主板)

-

• 中间层:Gen5 → Gen6 Switch

-

• 信号调理:PCIe Gen6 Retimer

-

• 传输介质:约2米高速线缆

-

• 终端设备:Micron PCIe Gen6 SSD

该架构的核心意义在于:

-

- 在当前尚未全面普及Gen6 Root Complex的情况下,通过Switch实现代际过渡(Gen5主机驱动Gen6设备)

-

- 验证在较长物理距离(2米)下,Gen6链路的可行性

-

- 展示Retimer在PAM4高速信号中的必要性

从系统搭建角度来看,这是一个典型的"过渡期验证平台",用于实验室环境或早期客户验证。

二、视频中体现的关键功能

根据字幕内容,视频主要体现了以下几个核心能力:

1. Gen6链路建立与带宽验证

系统已经完成从主机到SSD的完整链路训练,并能够进行数据读写。

实测性能约为:

- • 顺序带宽:约26 GB/s

该数值与PCIe 6.0 x4理论带宽(约32 GB/s)基本一致,考虑协议开销后属于合理范围,说明:

-

• 链路训练成功

-

• FEC机制正常工作

-

• PAM4信号质量在可接受范围内

这一点是整个演示中最核心的验证结果。

2. Retimer的调试与观测能力

视频中通过GUI界面展示了Retimer的多个功能,包括:

-

• Eye monitor(眼图监测)

-

• PRBS(伪随机码误码测试)

这说明该Retimer不仅承担信号重定时功能,还具备较强的调试能力,包括:

-

• 实时链路质量监测

-

• 误码率评估

-

• 信号裕量分析

在PCIe 6.0环境下,这类能力非常关键,因为:

-

• PAM4信号对噪声极为敏感

-

• 传统示波器调试成本高且不适合在线系统

-

• 系统级调试越来越依赖器件内部Telemetry

3. 长距离高速链路验证

视频明确指出使用了约2米线缆。

在PCIe 6.0条件下,这一点尤为重要:

-

• 64 GT/s PAM4信号损耗极大

-

• 单纯依赖PCB走线基本无法实现此距离

-

• 必须通过Retimer进行信号恢复

因此该演示实际上验证了:

-

• Retimer + Cable 的组合可以支持远距离Gen6链路

-

• 系统级部署具备现实可行性

三、SerialCables PCIe 6.0 Switch 的作用 (**查阅Saniffer公众之前拍摄的大量高清视频)

视频中提到的"Gen5 to Gen6 switch"承担了几个关键角色:

1. 代际桥接

在当前阶段,大量平台仍停留在PCIe Gen5:

-

• Switch作为中间层,实现Gen5 Host与Gen6设备互通

-

• 对系统开发和早期验证非常关键

2. 拓扑扩展能力

虽然视频中只展示单链路,但这类Switch通常具备:

-

• 多端口扩展能力

-

• Lane分配与重组

-

• 多设备挂载能力

在实际应用中,可用于:

-

• 多SSD测试平台

-

• AI服务器中GPU/SSD扩展

3. 面向验证平台的设计特点

相比传统数据中心Switch芯片,这类平台通常具备:

-

• 更灵活的拓扑配置

-

• 更容易插入测试设备(Analyzer、PAM等)

-

• 支持不同代际混合

因此更接近"验证平台级Switch",而不是单纯量产交换芯片。

四、Marvell Gen6 Retimer 的功能定位

结合视频内容以及当前主流Gen6 Retimer能力,可以总结其核心作用:

1. 信号完整性保障

在PCIe 6.0中:

-

• 使用PAM4编码

-

• 信号裕量显著下降

Retimer的作用包括:

-

• 重定时(Clock Data Recovery)

-

• 均衡(EQ)

-

• 抖动清理

这是保证链路稳定的基础。

2. 支持FEC链路

PCIe 6.0引入FEC(Forward Error Correction):

-

• Retimer需要与FEC机制协同工作

-

• 保证误码率在可纠正范围内

3. 调试与可观测能力(视频重点)

视频中展示的功能说明该Retimer具备:

-

• 内建眼图监测

-

• PRBS测试能力

-

• GUI可视化调试接口

这类能力在当前趋势下越来越重要,因为:

-

• 系统调试从"示波器驱动"转向"器件内观测"

-

• 可以在线分析链路质量

4. 在系统架构中的位置

在实际系统中,Retimer通常部署在:

-

• 主板边缘

-

• 线缆连接点

-

• Backplane中间节点

并且在Gen6系统中往往不是单颗,而是多级级联。

五、系统级意义

从整个演示来看,可以得出几个明确结论:

1. PCIe 6.0已经具备工程可用性

-

• 链路可稳定建立

-

• 带宽接近理论值

-

• 长距离传输可实现

说明技术已经从标准阶段进入系统验证阶段。

2. Retimer成为必选器件

在Gen5时代:

- • Retimer是"视情况使用"

在Gen6时代:

- • Retimer几乎是必须组件

尤其在以下场景:

-

• 线缆连接

-

• 多板卡系统

-

• AI服务器复杂拓扑

3. Switch + Retimer + Cable成为基础组合

该视频实际展示的是一个典型组合:

-

• Switch:负责拓扑与协议桥接

-

• Retimer:负责信号恢复

-

• Cable:实现物理扩展

这一组合将成为未来PCIe 6.0系统的基础结构。

六、对实际应用的启示

结合当前AI服务器和存储系统的发展,这类架构已经开始对应到真实需求:

-

• GPU服务器中远距离PCIe连接

-

• NVMe SSD外扩系统

-

• CXL相关内存扩展(未来)

-

• 高速测试与验证平台

对测试和分析工具厂商来说,重点关注对象将从单一设备转向:

-

• 整条链路(Link-level)

-

• 多器件协同(Switch + Retimer)

-

• 信号与协议联合分析

总结

该视频的核心并不在展示某一个器件,而是在验证一条完整的PCIe 6.0系统链路:

-

• 在Gen5主机条件下,通过Switch实现Gen6扩展

-

• 通过Retimer保证PAM4信号质量

-

• 在2米线缆条件下稳定运行Gen6 SSD

-

• 实测带宽达到约26 GB/s

这表明,PCIe 6.0已经具备进入系统级部署和应用验证的基础条件,同时也明确了未来系统设计中几个关键器件的角色分工。