计算机体系结构之存储系统详解:读懂计算机的"数据仓库"设计

存储系统是计算机体系结构的核心组成部分,承担着程序和数据的存储、读取、写入 核心功能,是CPU与外部设备之间的"数据仓库"。从高速的CPU寄存器到低速的磁盘阵列,存储系统通过层次化设计 ,兼顾了存取速度、存储容量、成本价格三大核心指标,让计算机在高效运行的同时,实现海量数据的持久化存储。

本文将按照「存储层次结构→存储器分类→核心存储部件→高级存储方案→校验技术→专用处理器」的逻辑,全面解析存储系统的设计原理、核心部件和实际应用,对应计算机体系结构存储系统知识点。

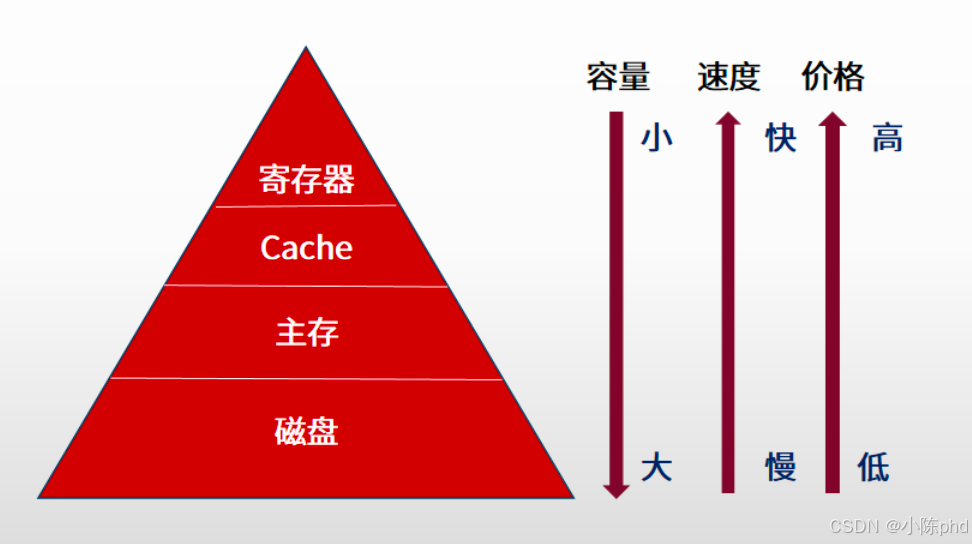

1 存储系统的核心设计思想:层次化结构

计算机的存储需求存在天然矛盾:速度越快的存储介质,成本越高、容量越小;容量越大的存储介质,速度越慢、成本越低 。为了解决这一矛盾,存储系统采用金字塔式的层次化结构 ,从CPU核心到外部设备,按速度由快到慢、容量由小到大、成本由高到低依次分层,各层协同工作,让整个存储系统在速度、容量、成本之间达到最优平衡。

1.1 存储层次的核心分层(从上层到下层)

存储层次的每一层都有明确的功能定位,且相邻层级之间通过数据缓存/调度机制 实现数据交互,核心分层及特点如下:

- 寄存器:位于CPU内部,是速度最快的存储介质,容量极小(通常以字节/千字节为单位),用于临时存放CPU运算的操作数、中间结果和指令地址,由硬件直接控制,无软件访问接口;

- 高速缓存(Cache):分为片上缓存(L1/L2,集成在CPU芯片内)和片外缓存(L3,位于CPU与主存之间),速度仅次于寄存器,容量较小(几MB到上百MB),用于缓存CPU近期可能频繁访问的指令和数据,减少CPU与主存之间的访问次数;

- 主存储器(主存/内存) :计算机的核心内存,速度中等,容量较大(几GB到上百GB),用于存放计算机运行期间正在使用的程序和数据,CPU可直接随机读写,是存储系统的核心层;

- 辅助存储器(辅存/外存) :如硬盘、U盘、光盘、闪存等,速度较慢,容量极大(几百GB到数TB),成本极低,用于存放暂时不用的程序和数据,实现数据的持久化存储,CPU无法直接访问,需先将数据调入主存后再处理。

1.2 层次化结构的核心优势

- 速度优化:CPU优先访问上层高速存储(寄存器/Cache),大幅减少对低速存储的访问,让整体存取速度接近上层高速介质;

- 容量优化:下层低速存储提供海量容量,让整个存储系统的实际容量接近下层大容量介质;

- 成本优化:仅上层核心区域使用高价高速介质,下层大部分区域使用低价低速介质,让整体存储成本接近下层低价介质。

简单来说,存储层次化结构的核心是**"用高速介质提升速度,用低速介质扩容降本"**,是现代计算机存储系统的基础设计原则。

2 存储器的核心分类方式

存储器的分类维度多样,核心分为按硬件结构分类 和按与处理器的物理距离分类两种,两种分类方式相互交叉,覆盖所有存储介质,是理解不同存储器特性的基础。

2.1 按硬件结构分类

根据存储介质的物理特性、工作原理,存储器可分为以下几类,各类型有明确的速度、容量、应用场景差异:

- SRAM(静态随机存取存储器) :采用双稳态触发器存储数据,速度极快、功耗较高、成本高、容量小,主要用于CPU片上Cache(L1/L2)、片外Cache(L3);

- DRAM(动态随机存取存储器) :采用电容存储数据,需定期刷新,速度比SRAM慢、功耗较低、成本低、容量大,主要用于计算机主存(内存条);

- NVRAM(非易失性随机存取存储器) :断电后数据不丢失,结合了SRAM的速度和闪存的非易失性,成本极高,主要用于工业控制、高端服务器;

- Flash(闪存) :断电后数据不丢失,速度中等、容量大、成本低,主要用于固态硬盘(SSD)、U盘、手机内存;

- EPROM/EEPROM(可编程只读存储器) :断电后数据不丢失,可多次擦写,速度较慢,主要用于单片机、嵌入式设备的程序存储;

- Disk(磁盘) :包括机械硬盘(HDD)、光盘等,速度慢、容量极大、成本极低,主要用于海量数据的持久化存储。

2.2 按与处理器的物理距离分类

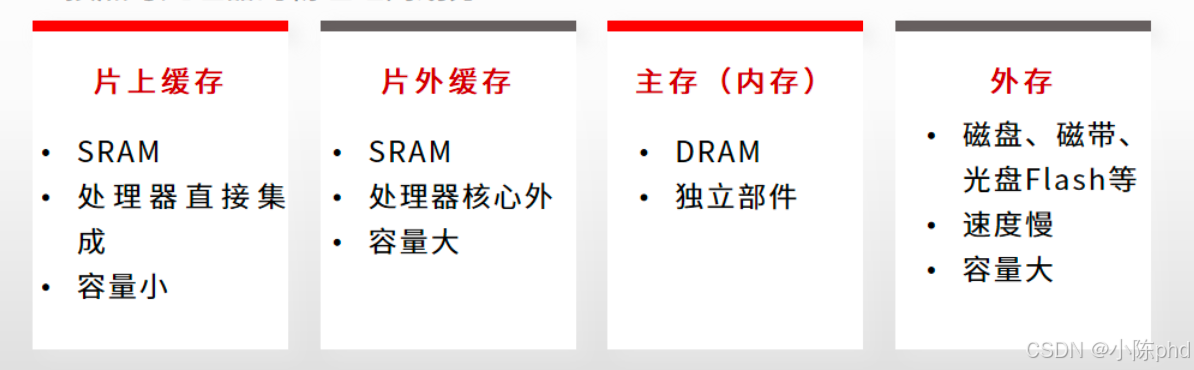

根据与CPU的物理位置关系,存储器可分为四层,与存储层次化结构一一对应,核心关注CPU的访问方式 和存储介质的集成位置:

- 片上缓存 :直接集成在CPU芯片内部,如L1/L2 Cache,CPU可直接访问,速度最快,介质为SRAM,容量小;

- 片外缓存 :位于CPU芯片外部、主存之前,如L3 Cache,CPU通过专用总线访问,速度次之,介质为SRAM,容量比片上缓存大;

- 主存(内存) :作为独立部件连接在主板上,CPU通过系统总线访问,速度中等,介质为DRAM,容量大;

- 外存 :作为独立设备连接在主板的接口上(如SATA/USB接口),CPU无法直接访问,速度最慢,介质为磁盘、闪存等,容量极大。

3 存储系统的核心部件:主存储器

主存储器(简称主存,又称内存)是存储系统的核心中间层 ,是CPU与外存之间的桥梁,也是计算机运行的"核心数据区"------所有运行中的程序和数据,必须先调入主存,才能被CPU处理 。理解主存的工作原理,是掌握存储系统的关键。主存用来存放计算机运行期间所需要的程序和数据,CPU可直接随机地进行读/写。

3.1 主存的核心特性

- 随机存取:CPU可直接访问主存中的任意一个存储单元,访问速度与存储单元的位置无关;

- 易失性:断电后主存中的数据会全部丢失,无法实现持久化存储;

- 高速访问:访问速度远快于外存,远慢于Cache/寄存器,是平衡速度和容量的核心层;

- 容量适中:容量远大于Cache/寄存器,远小于外存,通常为8GB、16GB、32GB、64GB等。

3.2 主存的基本构成与访问方式

3.2.1 基本构成:存储单元+地址编码

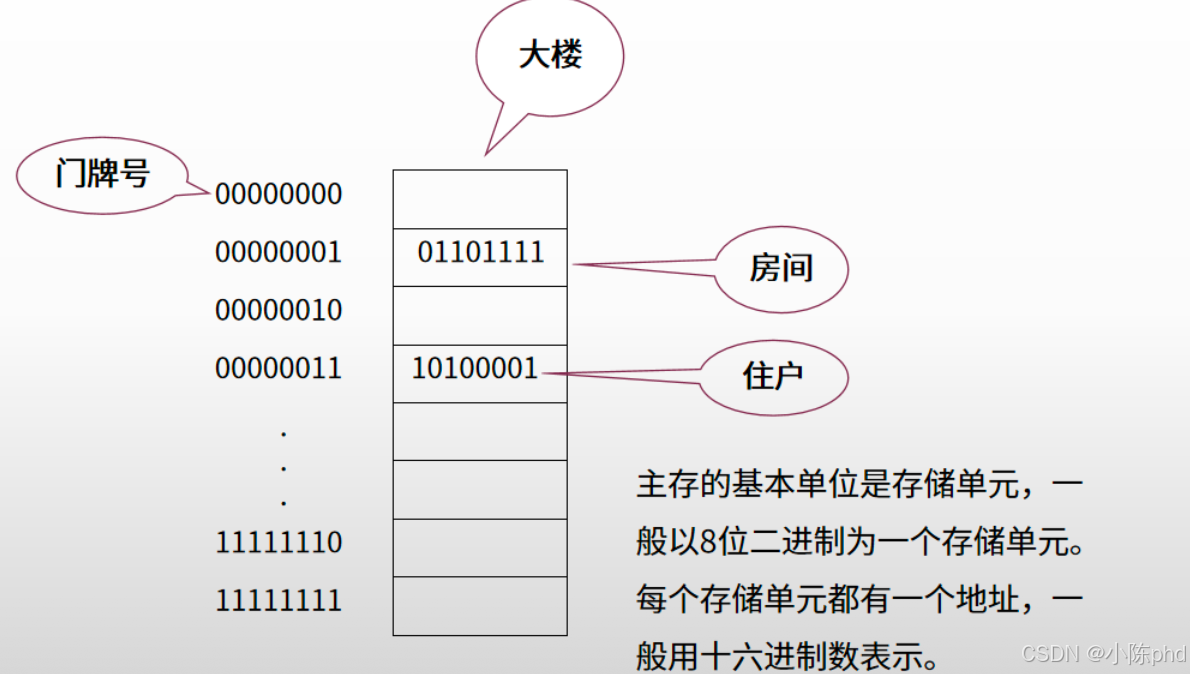

主存的基本组成单位是存储单元 ,以8位二进制(1个字节)为一个基本存储单元 ,每个存储单元都有一个唯一的地址 (通常用十六进制数表示),地址从0开始连续编码,形成主存的地址空间。

可以将主存类比为"一栋大楼":存储单元是大楼的房间,地址是房间的门牌号,CPU通过"门牌号"精准找到对应的"房间",实现数据的读写。

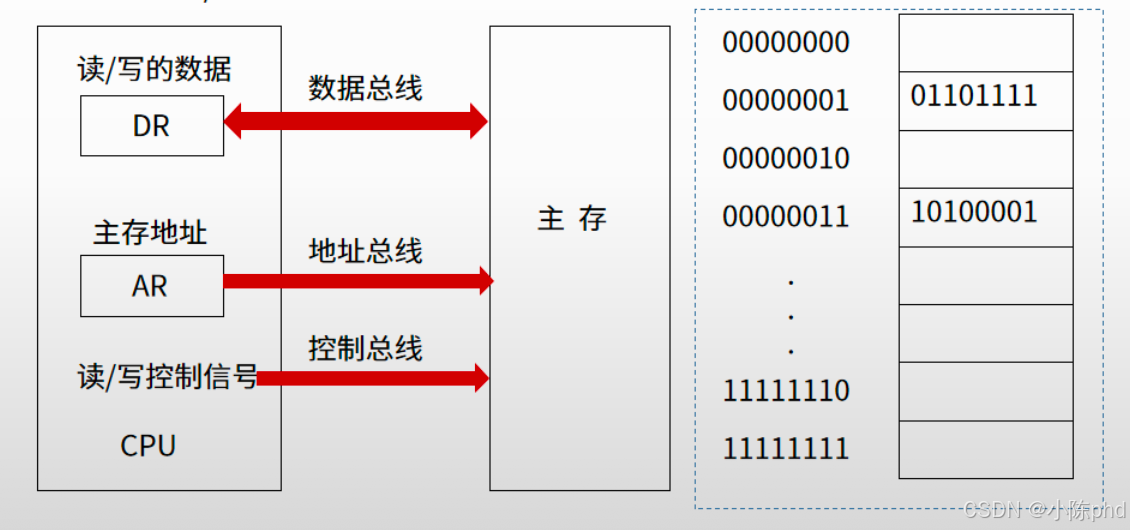

3.2.2 CPU访问主存的三大总线

CPU与主存之间的信息交互,通过三大系统总线完成,三者分工明确,共同实现数据的地址传递、数据传输和控制信号传递:

- 地址总线(AB) :CPU将需要访问的主存单元地址,通过地址总线传递给主存的地址寄存器(AR/MAR) ,主存根据该地址定位存储单元,地址总线的位数决定了主存的最大寻址空间(如32位地址总线可寻址2322^{32}232个存储单元,即4GB);

- 数据总线(DB) :CPU与主存之间的实际数据传输通道,读操作时,主存将数据通过数据总线传递给CPU的数据缓冲寄存器(DR/MDR);写操作时,CPU将数据通过数据总线传递给主存的存储单元,数据总线的位数决定了一次可传输的数据量(如64位数据总线一次可传输8个字节);

- 控制总线(CB) :CPU通过控制总线向主存发出读/写控制信号,主存根据控制信号执行对应的操作(读数据或写数据),同时主存也会通过控制总线向CPU反馈操作状态(如是否读写成功)。

3.3 主存容量计算(经典考点)

主存按字节编址(即每个地址对应1个字节的存储单元),已知主存的起始地址和结束地址,主存容量 = 结束地址 - 起始地址 + 1 ,计算结果需转换为常用单位(KB/MB/GB,1KB=1024B1KB=1024B1KB=1024B,1MB=1024KB1MB=1024KB1MB=1024KB,1GB=1024MB1GB=1024MB1GB=1024MB)。

经典真题计算示例

题目 :内存按字节编址,地址从A4000H到CBFFFH,共有多少个字节?若用存储容量为32K×8bit的存储芯片构成该内存,至少需要多少片?

解题步骤:

- 计算地址总数:CBFFFH−A4000H+1=CC000H−A4000H=28000HCBFFFH - A4000H + 1 = CC000H - A4000H = 28000HCBFFFH−A4000H+1=CC000H−A4000H=28000H(十六进制);

- 十六进制转十进制:28000H=2×164+8×163=131072+32768=163840B=160×1024B=160KB28000H = 2×16^4 + 8×16^3 = 131072 + 32768 = 163840B = 160×1024B = 160KB28000H=2×164+8×163=131072+32768=163840B=160×1024B=160KB;

- 计算芯片数量:存储芯片容量为32K×8bit(即32KB),160KB÷32KB=5160KB ÷ 32KB = 5160KB÷32KB=5片。

答案:160KB,5片。

4 高级存储方案:磁盘阵列(RAID)

随着计算机对存储速度、容量、可靠性 的要求不断提升,单一磁盘已无法满足需求,因此出现了磁盘阵列(RAID)技术------将多台磁盘存储器通过硬件/软件方式组合成一个整体,形成一个快速、大容量、高可靠的外存子系统 ,核心采用分块技术、交叉技术、重聚技术 ,目前主流为廉价冗余磁盘阵列(Redundant Array of Independent Disk,RAID),分为8个核心级别,各级别适配不同的应用场景。

4.1 RAID的核心设计目标

- 提升存取速度:多磁盘并行读写,大幅提高数据传输速率;

- 扩大存储容量:多磁盘容量叠加,实现海量存储;

- 提高可靠性:通过冗余校验、数据镜像等方式,实现数据容错,避免单磁盘故障导致的数据丢失。

4.2 主流RAID级别及核心特点

RAID各等级的设计思路差异较大,核心分为无冗余级别、镜像冗余级别、校验冗余级别,以下为最常用的6个级别,也是考试和实际应用的核心重点:

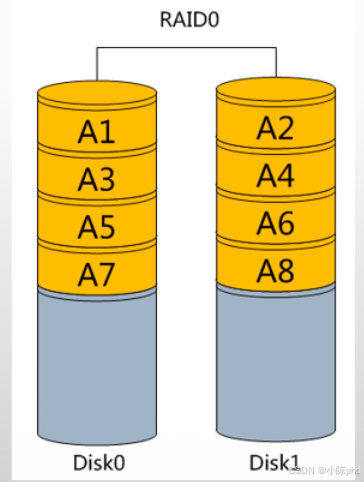

4.2.1 RAID 0(无冗余和无校验的数据分块)

- 核心原理:将数据平均分成若干块,分散存储在多块磁盘上,无数据冗余和校验;

- 特点 :最高的I/O性能、最高的磁盘空间利用率(100%) ,易管理;但系统故障率高,无容错能力,单磁盘故障会导致所有数据丢失;

- 适用场景 :关注性能、容量和价格,不要求可靠性的场景,如视频编辑、临时数据存储。

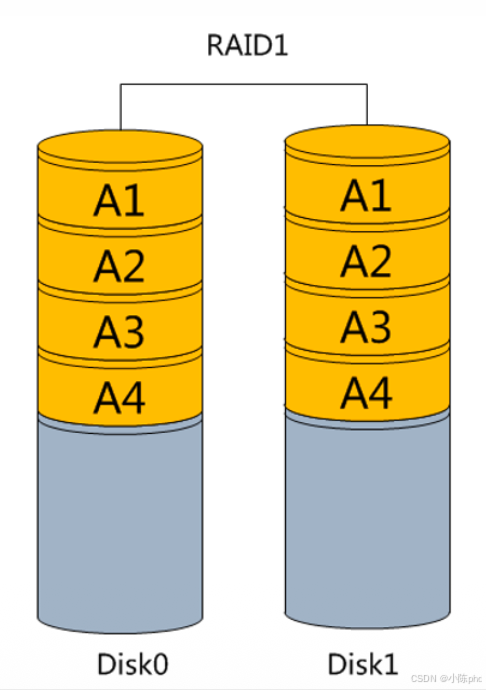

4.2.2 RAID 1(磁盘镜像阵列)

- 核心原理 :由磁盘对组成,每一个工作盘都有对应的镜像盘,工作盘与镜像盘存储完全相同的数据拷贝;

- 特点 :最高的安全性和容错能力 ,单磁盘故障时,镜像盘可直接替代,数据无丢失;但磁盘空间利用率仅50%,成本高,性能提升有限;

- 适用场景 :存放系统软件、核心数据、重要文件,如服务器系统盘、金融核心数据存储。

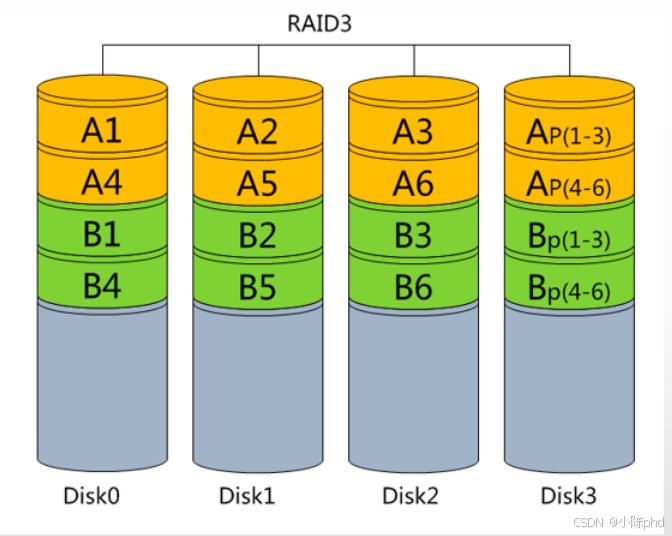

4.2.3 RAID 3/RAID 4(采用奇偶校验码的磁盘阵列)

- 核心原理 :将数据分块存储在多块数据盘上,将奇偶校验码集中存储在一块独立的校验盘上 ,RAID 3为位交叉奇偶校验 ,RAID 4为块交叉奇偶校验;

- 特点 :读数据速度快,单数据盘故障时,可通过校验盘的校验码恢复数据;但写数据速度慢(每次写数据都需重新计算并更新校验码),校验盘为单点故障;

- 适用场景 :RAID 3适用于大型文件且I/O需求不频繁的场景,RAID 4适用于大型文件的读取场景。

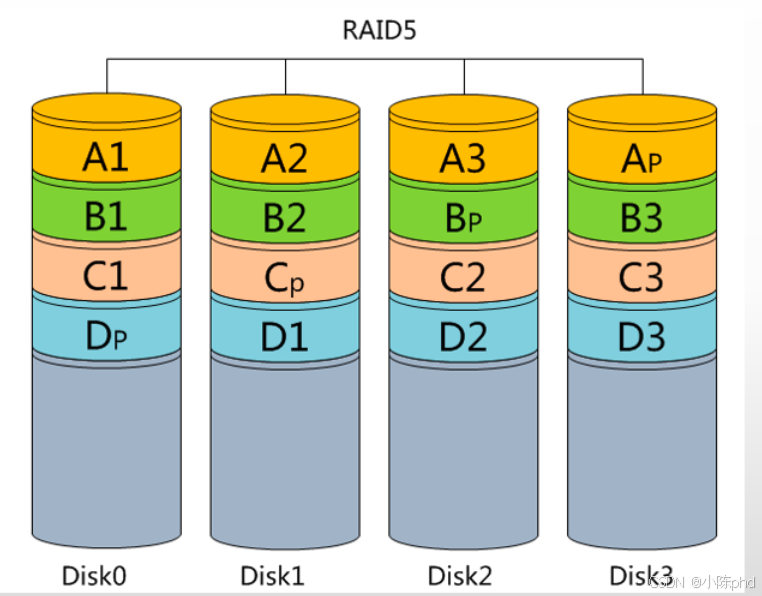

4.2.4 RAID 5(无独立校验盘的奇偶校验码磁盘阵列)

- 核心原理 :将数据分块存储在多块磁盘上,校验信息分散存储在所有磁盘上,无独立校验盘;

- 特点 :大批量和小批量数据的读写性能都优秀 ,磁盘空间利用率为N−1N-1N−1(N为磁盘数量),单磁盘故障时可通过其他磁盘的校验信息恢复数据,容错能力强;

- 适用场景 :I/O需求频繁的场景,如银行、金融、股市的大型数据处理中心,是目前应用最广泛的RAID级别 。

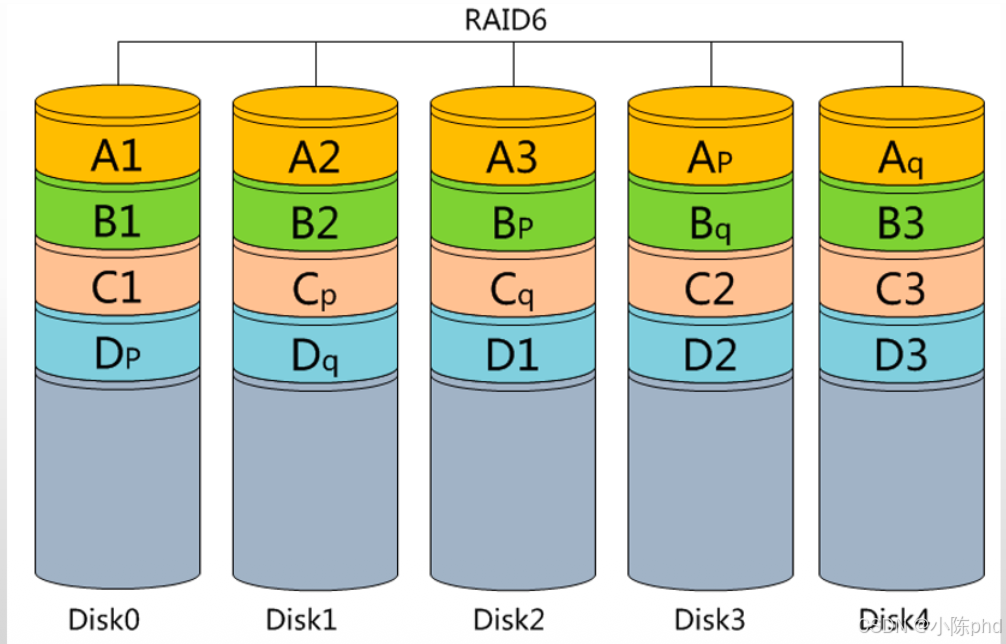

4.2.5 RAID 6(双分布式校验的磁盘阵列)

- 核心原理 :在RAID 5的基础上,增加第二组独立的分布式校验码,实现双校验;

- 特点 :容错能力更强 ,可容忍两块磁盘同时故障 ,数据不丢失;但性能略有下降,成本更高 ,磁盘空间利用率为N−2N-2N−2;

- 适用场景 :对数据可靠性要求极高的核心业务场景,如金融交易、医疗数据存储。

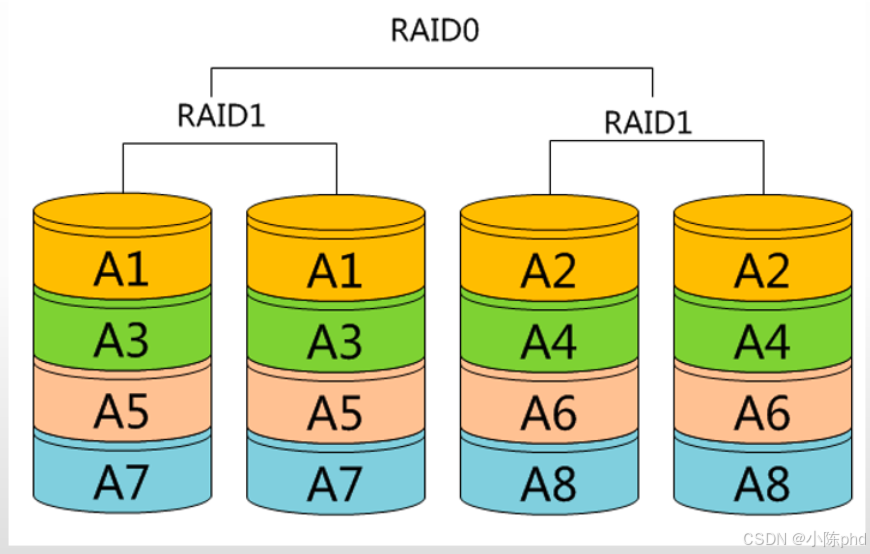

4.2.6 RAID 10(RAID 0+1,高可靠性与高性能的组合)

- 核心原理:结合RAID 0和RAID 1的特点,先将磁盘分为多组,每组做RAID 0(提升性能),再将各组做RAID 1(实现镜像冗余);

- 特点 :兼顾RAID 0的高速读写和RAID 1的高可靠性 ,容错能力强,单磁盘故障不影响整体性能;但磁盘空间利用率仅50%,成本高;

- 适用场景 :对性能和可靠性都有高要求的场景,如高端服务器、数据库核心存储。

4.3 主流RAID级别核心参数对比

| RAID级别 | 磁盘空间利用率 | 容错能力 | 读写性能 | 核心特点 | 典型适用场景 |

|---|---|---|---|---|---|

| RAID 0 | 100% | 无 | 最高 | 高速扩容,无冗余 | 视频编辑、临时存储 |

| RAID 1 | 50% | 单盘故障 | 读快写一般 | 镜像冗余,高安全 | 系统盘、核心数据存储 |

| RAID 5 | N-1 | 单盘故障 | 读写均优 | 分布式校验,性价比高 | 金融、电商、通用服务器 |

| RAID 6 | N-2 | 双盘故障 | 读写略低于RAID5 | 双分布式校验,超高安全 | 核心金融、医疗数据存储 |

| RAID 10 | 50% | 单盘故障(每组) | 接近RAID0 | 性能+安全兼顾 | 高端数据库、大型服务器 |

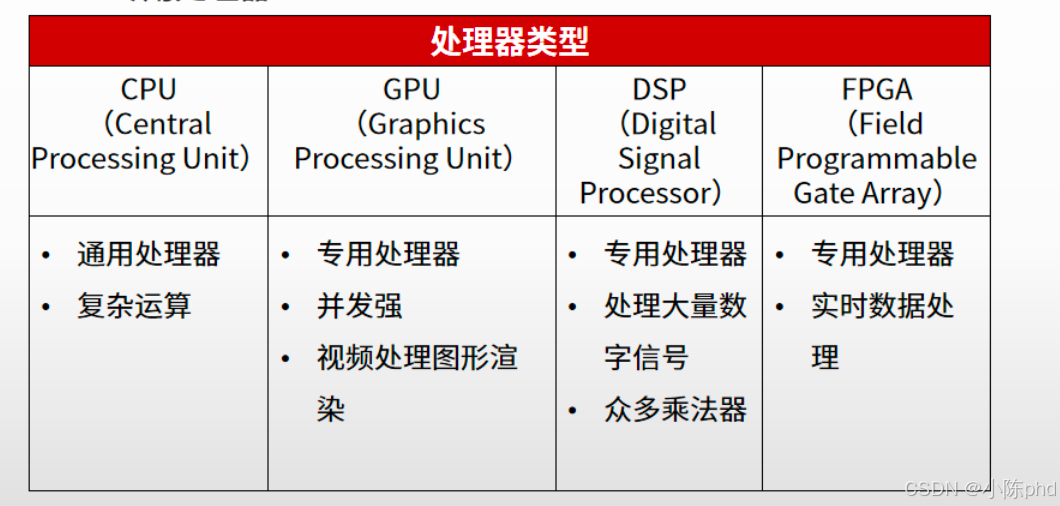

5 存储系统的高效运行支撑:专用处理器

存储系统的高效运行,除了依赖层次化结构和核心介质,还需要专用处理器 的支撑------专用处理器针对存储操作进行硬件级优化,大幅提升数据的读写、调度、校验效率,与通用CPU(中央处理器)协同工作,构成计算机的处理器体系。

5.1 专用处理器的核心定义与设计初衷

专用处理器是针对某一类特定任务、特定应用场景进行硬件架构和指令集优化的处理器,其设计摒弃了通用CPU"全场景适配"的特点,聚焦于单一/一类任务的高效执行,在特定场景下的处理效率、功耗控制远优于通用CPU。

在存储系统中,专用处理器主要承担存储数据的处理、存储设备的控制、存储任务的调度等工作,核心目的是弥补通用CPU在存储专用任务上的效率短板,将通用CPU从繁琐的专用任务中解放,专注于核心运算和控制。

5.2 存储系统中主流的专用处理器类型及核心功能

5.2.1 DSP(数字信号处理器):存储数据的高速信号处理核心

- 核心硬件特点 :内置大量专用乘法器和加法器,采用流水线式信号处理架构,高效完成乘法-累加运算,运算速度是同主频通用CPU的数十倍甚至上百倍。

- 存储系统应用:负责数据压缩/解压缩、加密/解密、存储信号滤波降噪、数据格式转换(模拟→数字),提升存储数据的处理和传输效率。

- 典型场景:高端存储服务器、工业级存储设备、固态硬盘。

5.2.2 FPGA(现场可编程门阵列):存储任务的可编程硬件执行核心

- 核心硬件特点:无固定硬件架构和指令集,由可编程逻辑单元、互连资源、I/O口组成,可通过硬件描述语言(Verilog/VHDL)定制专属硬件逻辑,实现**"硬件按需定制"**,灵活性高、执行速度快、延迟低。

- 存储系统应用:完成RAID校验码的硬件计算、存储数据的分块/重聚、存储设备接口适配、存储任务实时调度,适配复杂存储场景(如磁盘阵列、云存储)。

- 典型场景:企业级磁盘阵列、云存储服务器、高性能计算存储节点。

5.2.3 存储控制器:存储设备与CPU的专用控制核心

- 核心硬件特点:针对存储设备控制、数据传输设计的专用集成电路(ASIC),集成地址映射单元、数据缓存单元、接口控制单元、读写控制单元,指令集仅聚焦于存储设备控制和数据传输,是存储介质与通用CPU/系统总线之间的**"专属桥梁"**。

- 存储系统应用:实现逻辑地址→物理地址映射、数据缓存与传输、存储设备读写控制、存储介质状态管理、多存储设备并行控制,是所有存储设备的核心组成部分。

- 分类与场景:分为内存控制器(控制DRAM主存)、硬盘控制器(控制磁盘/闪存)、外部存储控制器(控制U盘/移动硬盘),应用于内存条、固态硬盘、主板等存储硬件。

5.3 专用处理器与通用CPU的协同工作逻辑

在计算机整体硬件架构中,专用处理器与通用CPU形成**"主从分工、协同执行"的关系:通用CPU负责全局控制和核心运算,专用处理器负责专属存储任务。以主存读数据**流程为例:

- 通用CPU向内存控制器(专用处理器)发出读数据指令和逻辑地址;

- 内存控制器完成地址映射,向主存发出读控制信号,控制数据读取和缓存;

- 若数据为加密/压缩格式,内存控制器将数据传输给DSP(专用处理器),完成解密/解压缩;

- 处理后的数据通过系统总线传回通用CPU,供运算器使用。

整个过程中,通用CPU仅负责发出指令和最终运算,地址映射、硬件控制、数据处理等专用任务均由专用处理器完成,大幅提升了存储系统和计算机的整体运行效率。

5.4 国产专用处理器(存储相关)现状

国内已实现多款存储相关专用处理器的自主研发和量产,核心代表有:

- 国产DSP:华睿(中国电科)、翔腾微,应用于国产存储服务器、工业级存储设备;

- 国产FPGA:紫光同创、复旦微电、安路科技,适配国产磁盘阵列、云存储服务器的RAID校验和存储逻辑定制;

- 国产存储控制器:国微、国芯、兆芯,实现内存控制器、硬盘控制器的国产化替代,应用于国产内存条、固态硬盘;

- 综合类专用处理器:景嘉微,其图形处理和存储控制一体化芯片适配嵌入式、军工级存储系统。

这些国产专用处理器打破了国外技术垄断,实现了国产计算机存储系统从存储介质 到控制核心的全链条自主可控。

总结

存储系统是计算机的"数据仓库",其核心设计思想是层次化结构,通过寄存器、Cache、主存、外存的分层设计,解决了速度、容量、成本的天然矛盾;主存储器是存储系统的核心中间层,CPU通过地址、数据、控制三大总线实现对主存的随机读写,容量计算是核心考点;磁盘阵列(RAID)是高级外存方案,通过多磁盘组合实现速度、容量、可靠性的提升,RAID 5是应用最广泛的级别;校验码(如CRC)是存储系统的可靠性保障,通过编码检测数据错误;专用处理器(DSP/FPGA/存储控制器)则与通用CPU协同,将存储专用任务硬件化,大幅提升存储系统的运行效率,是现代大容量、高速率、高可靠性存储系统的核心支撑。

存储系统与CPU、指令系统共同构成计算机的硬件核心,三者的协同工作是计算机高效运行的基础:CPU负责运算和控制,指令系统是CPU的操作语言,存储系统是数据和程序的载体。理解存储系统的设计原理,不仅能掌握计算机的底层工作逻辑,还能为实际应用中的存储方案选型(如服务器RAID配置、内存扩容、缓存优化)提供理论支撑,是计算机体系结构的核心知识点之一。