基于Siwave的PCB EMMC信号波形与眼图仿真

本次Siwave工程下载:基于Siwave的PCB EMMC信号波形与眼图仿真工程文件

0、前言

最近对信号完整性(SI)、功率完整性(PI)比较感兴趣,博主六年前上本科时也是一个画板子好手,平时用AD软件搞点FR4的简单嵌入式的电路板子玩玩,几十兆的时钟玩得不亦乐乎,放在现在真的是out了。

现在像模像样的高大上的板子基本时钟频率非常高 ,板子上CPU和高速内存对电源、信号线有许多的要求,在实际投板前需要进行信号完整性(SI)、功率完整性(PI)的仿真,因此来学习一下下。学习资料是于博士的书籍《信号完整性揭秘》,还有配套的视频啥的,非常好用,简单开坑记录下。

Siwave是Ansys旗下的软件,专门用于SI和PI的仿真,之前用它家的HFSS非常多,这次也来尝尝鲜。软件的下载可以去老吴那边下载:Ansys EM 2025 R2 电磁仿真安装包已发布。

目录

- [基于Siwave的PCB EMMC信号波形与眼图仿真](#基于Siwave的PCB EMMC信号波形与眼图仿真)

1、导入IBIS模型

1.1、IBIS模型库设置

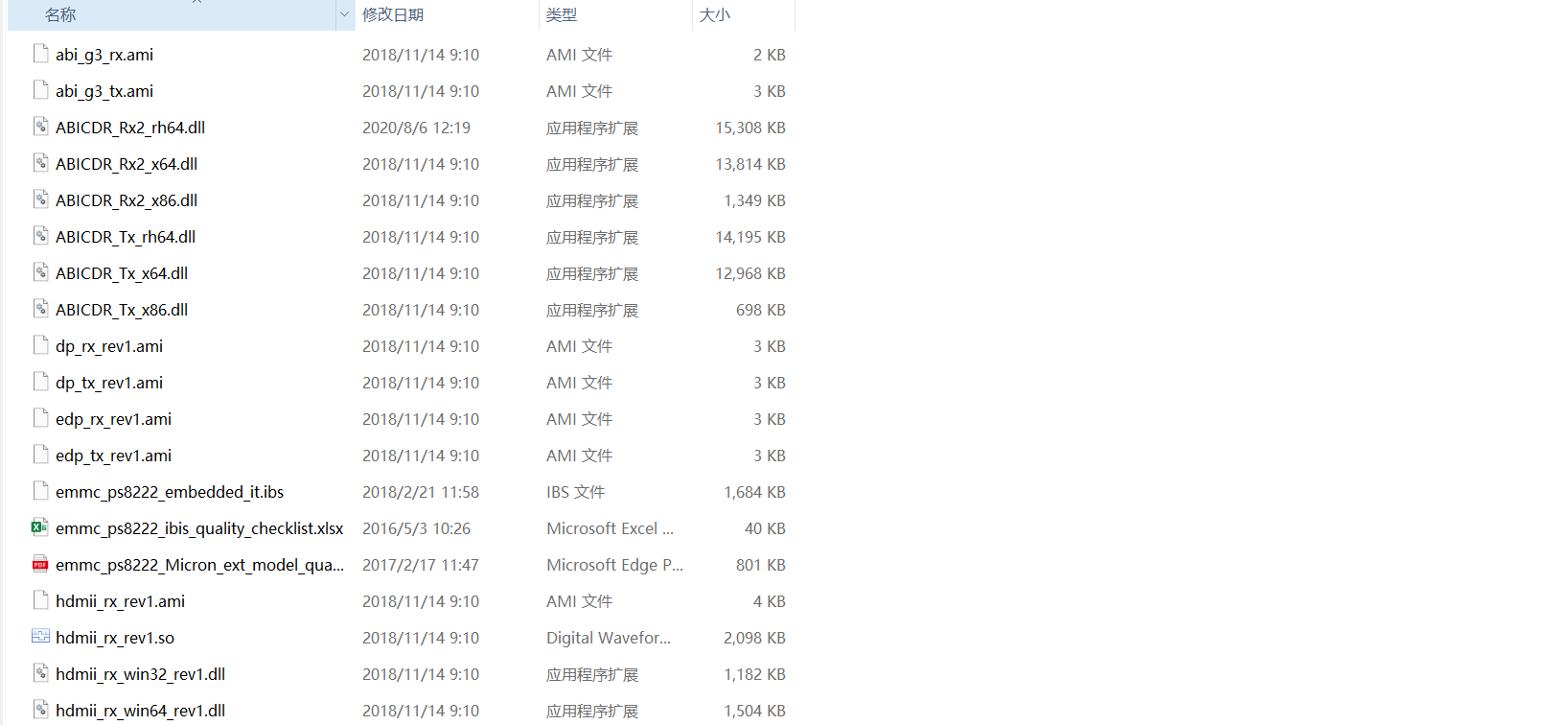

把用到的所有的ibis模型都放到一个文件夹里面,好作为库一起添加:

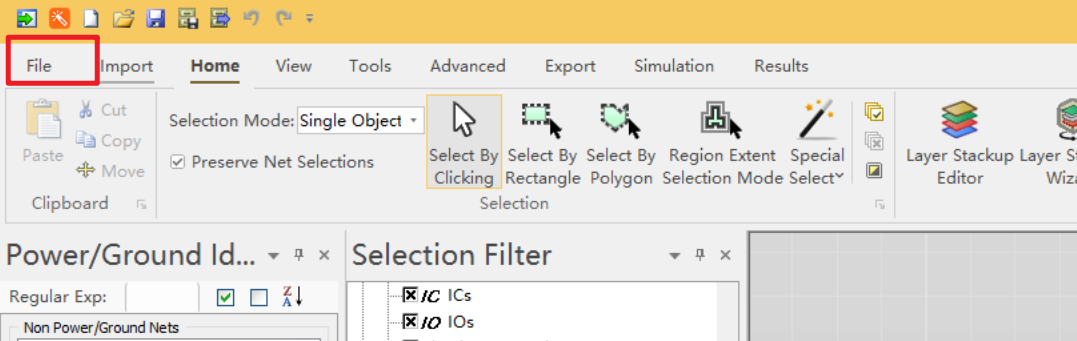

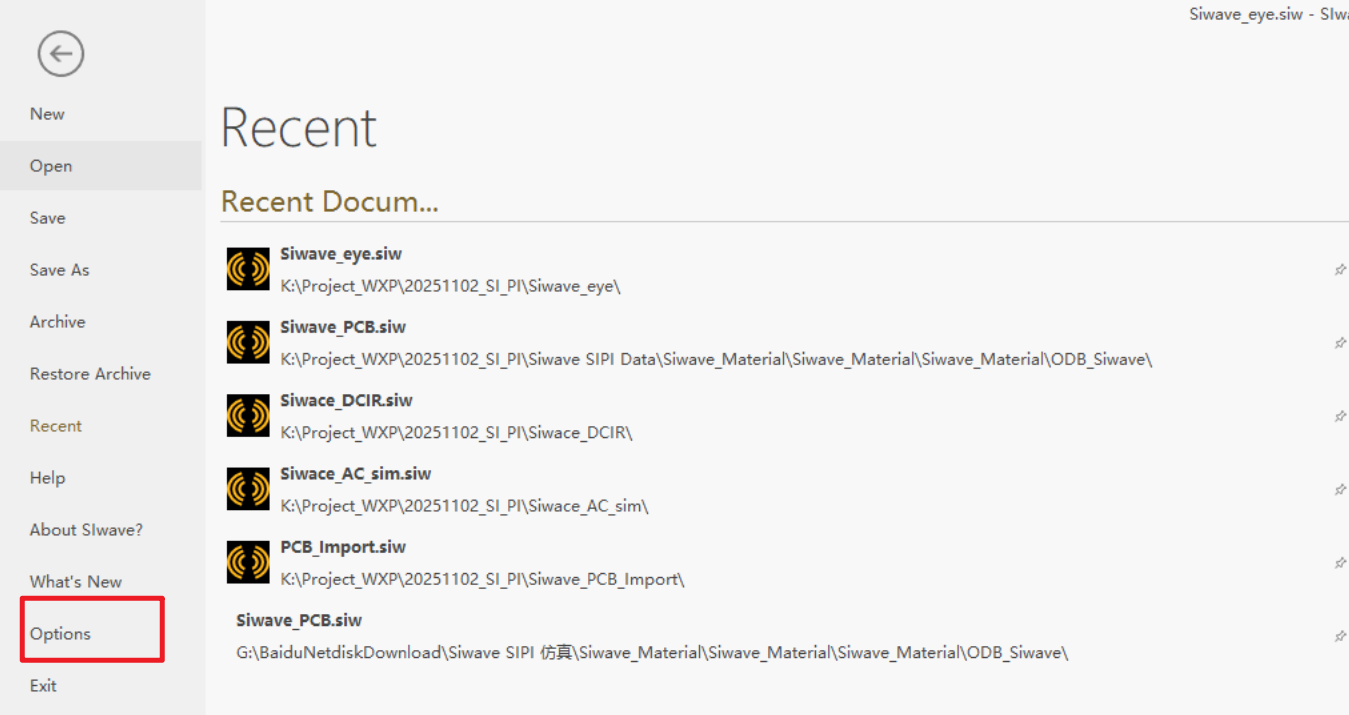

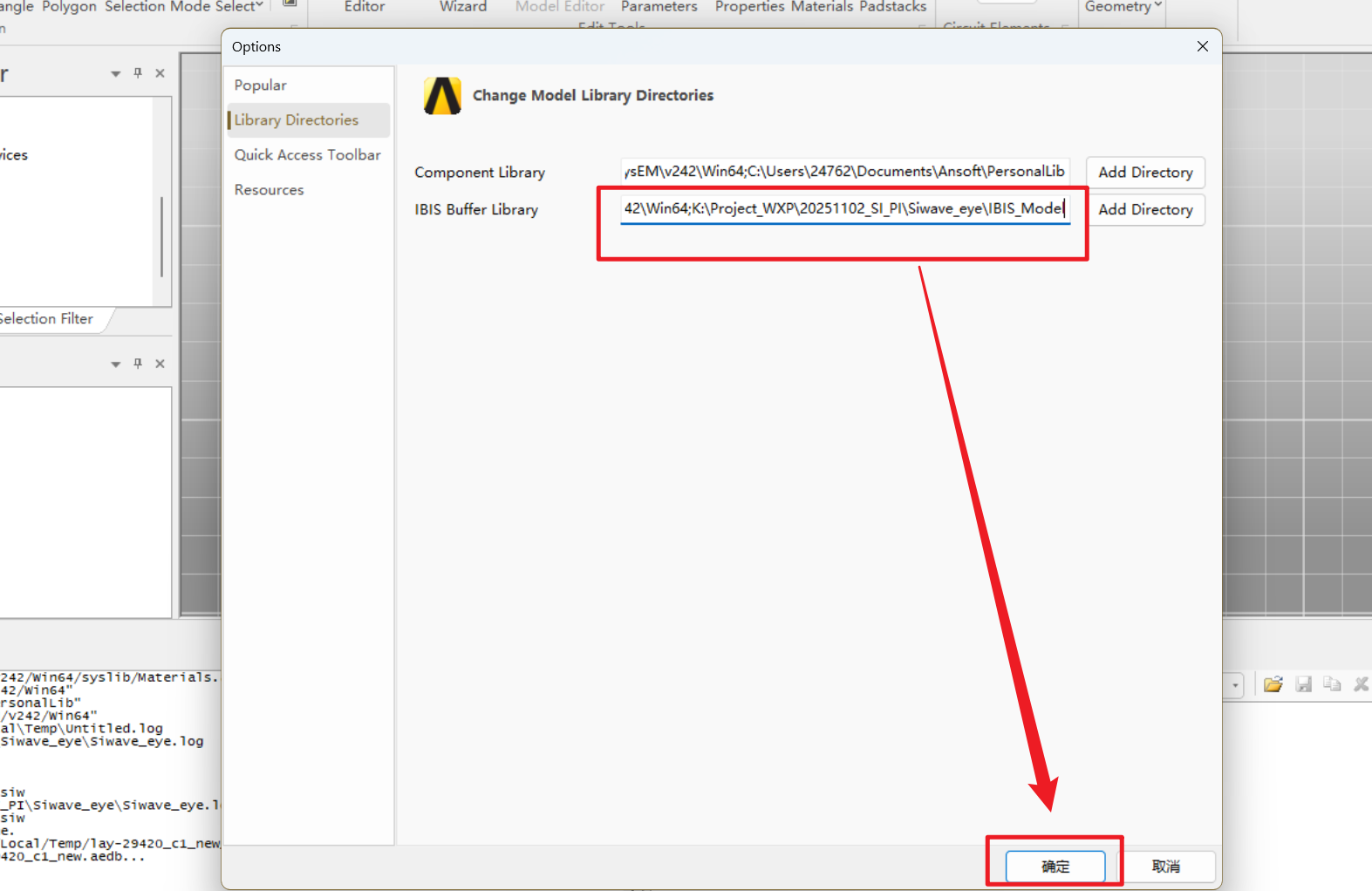

按照下面步骤添加该文件夹为ibis库路径:

路径间使用分号隔开,添加刚刚的路径地址,设置完成后点击确定即可:

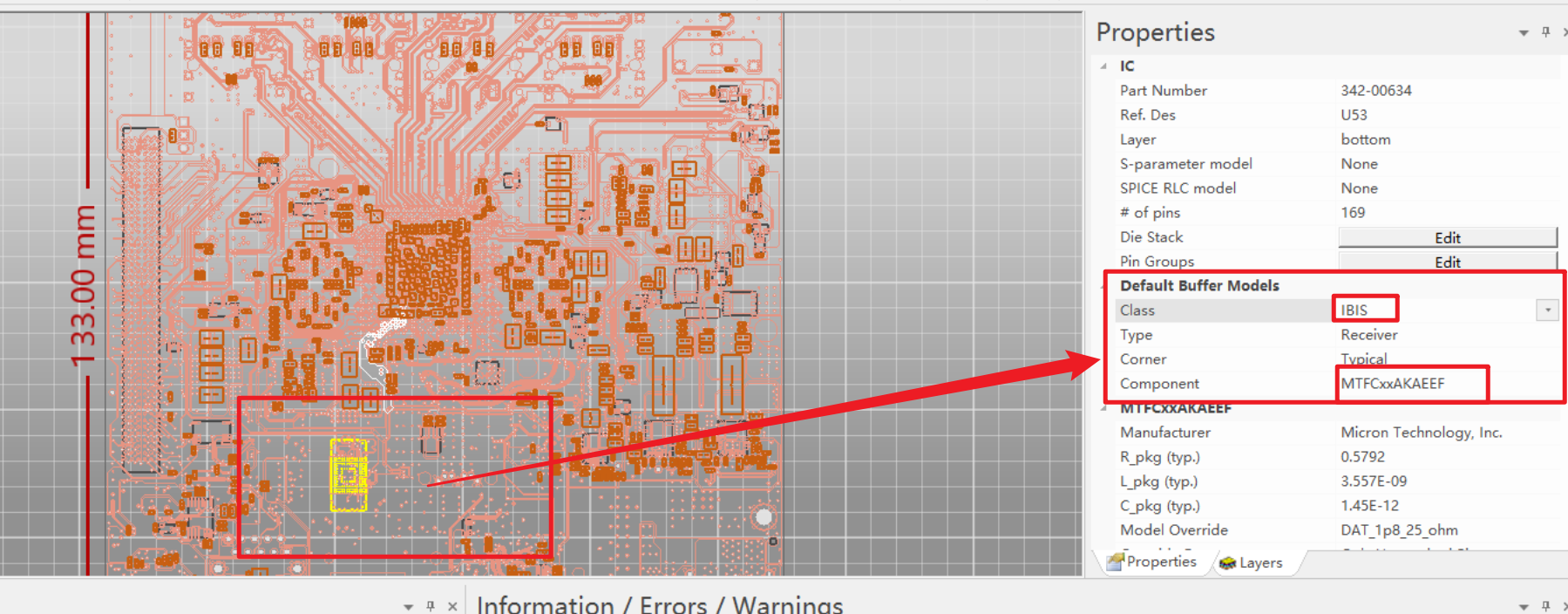

1.2、设置器件的IBIS模型

选择EMMC器件,设置对应的IBIS模型:

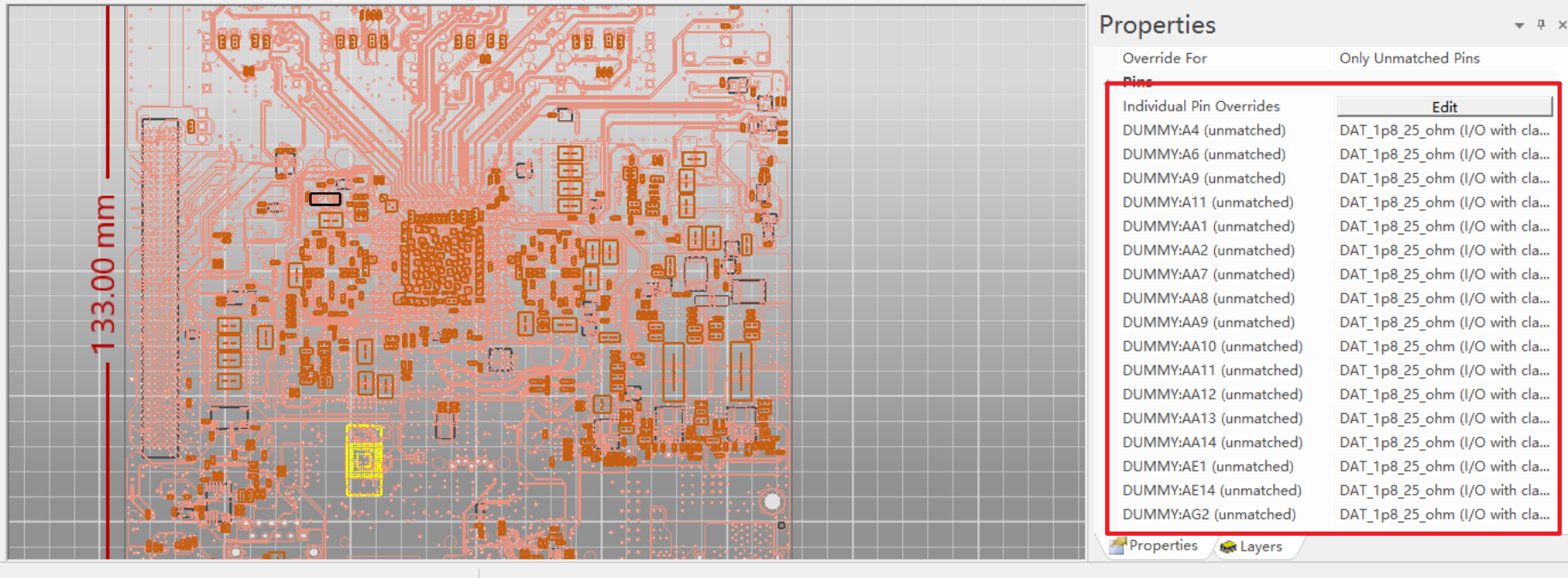

绑定模型后,器件引脚会被自动设置:

2、仿真步骤

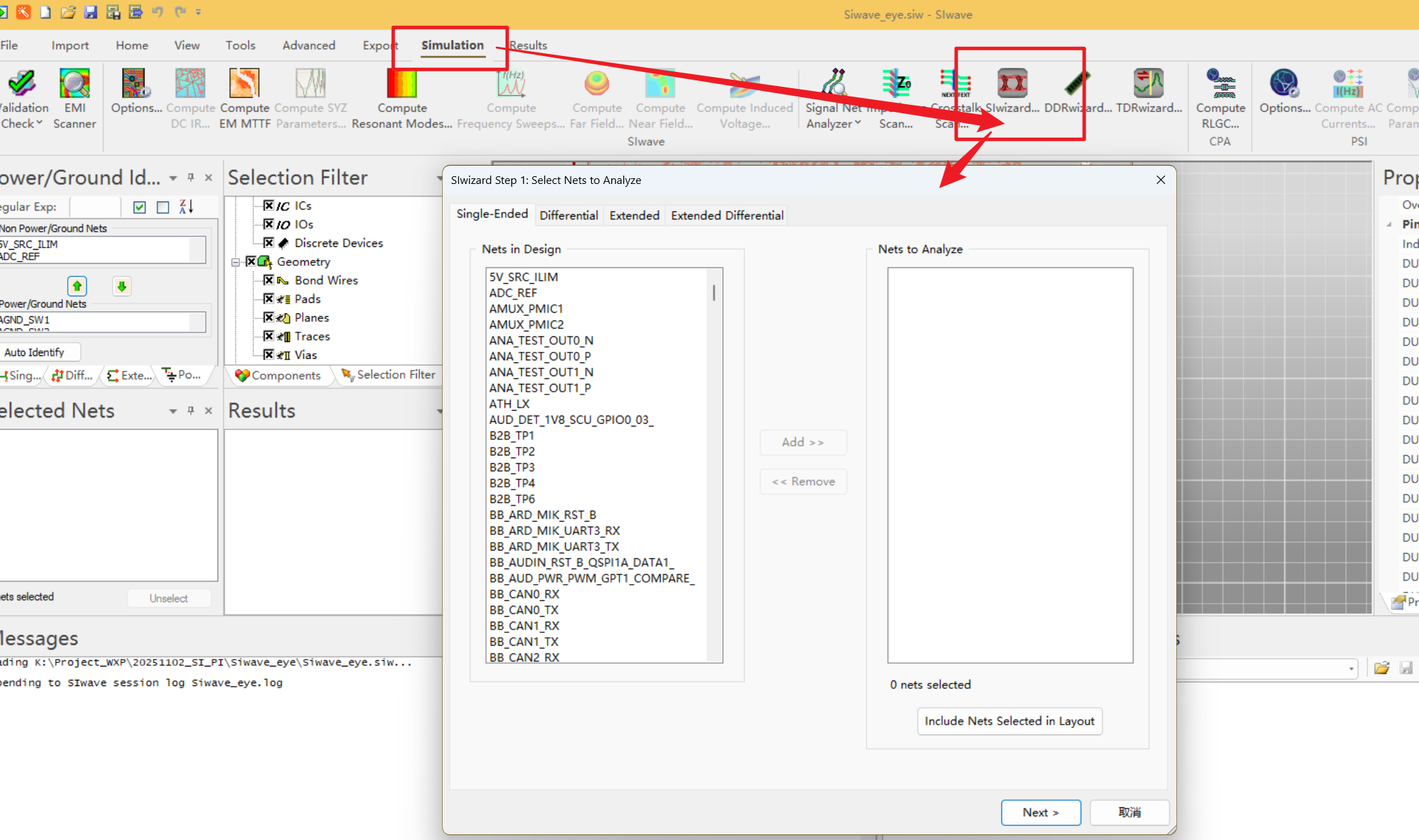

2.1、启用仿真向导

找到并启动仿真向导:

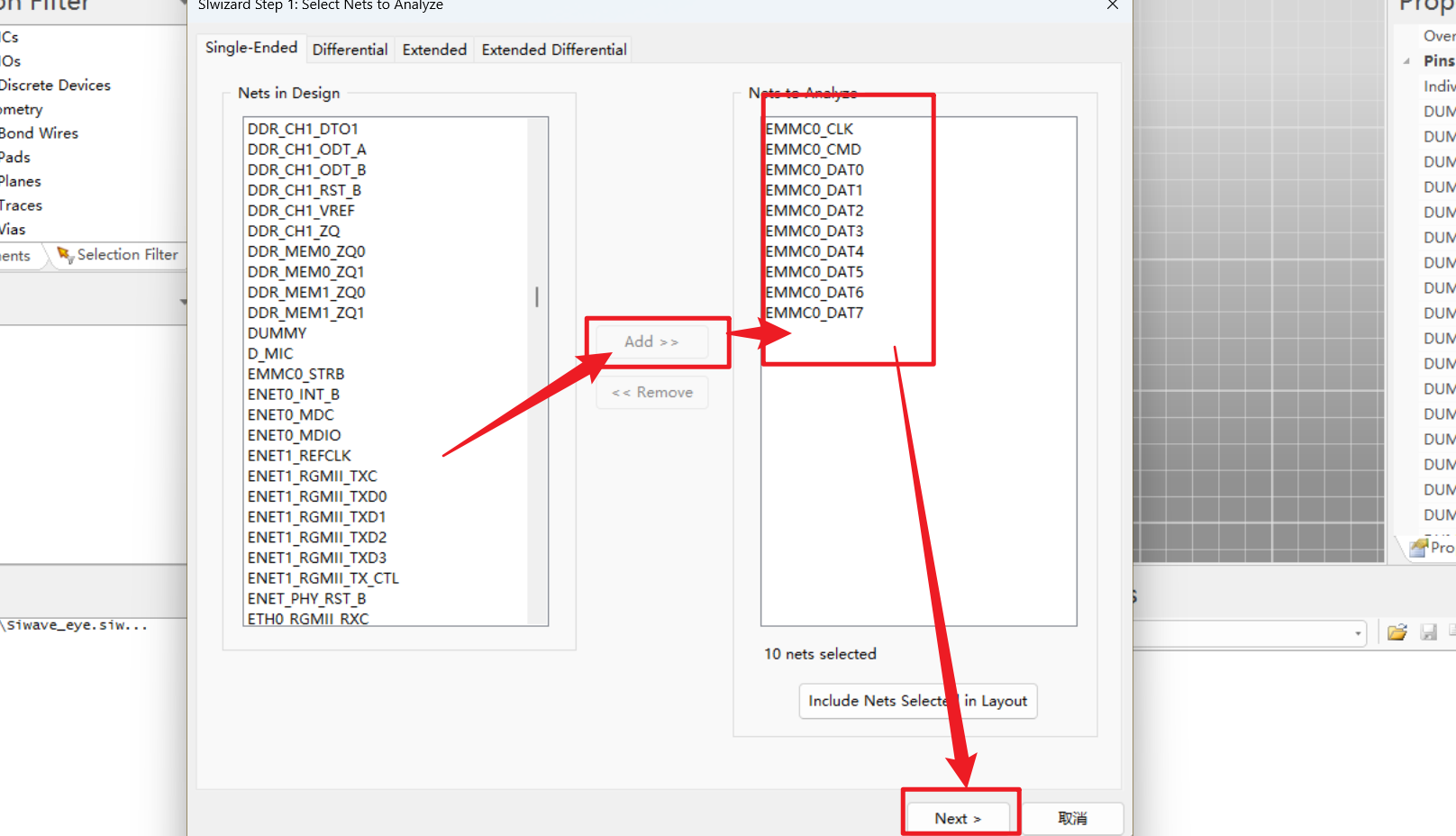

找到所需的网络名称,Add到右侧即可,设置完成点击下一步:

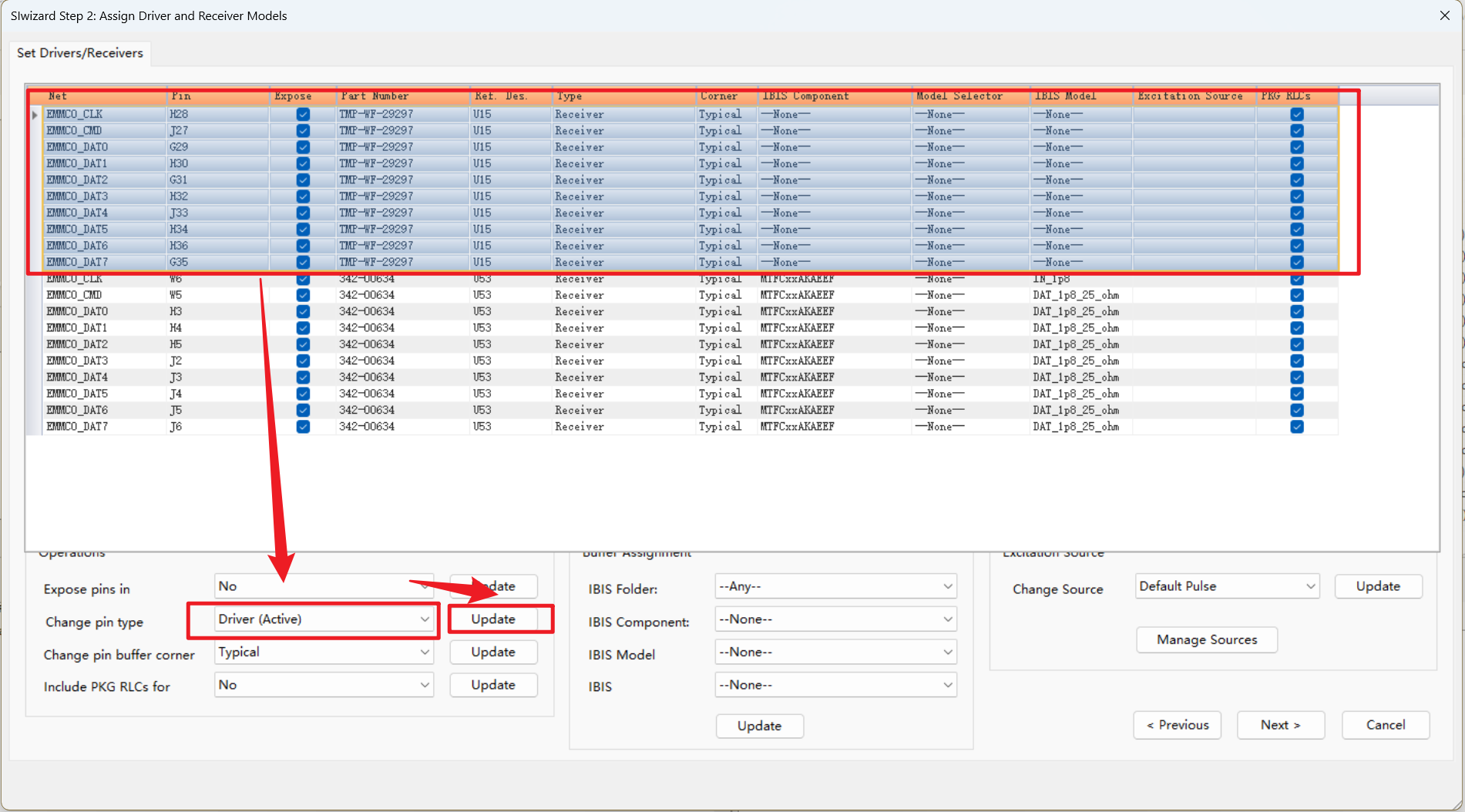

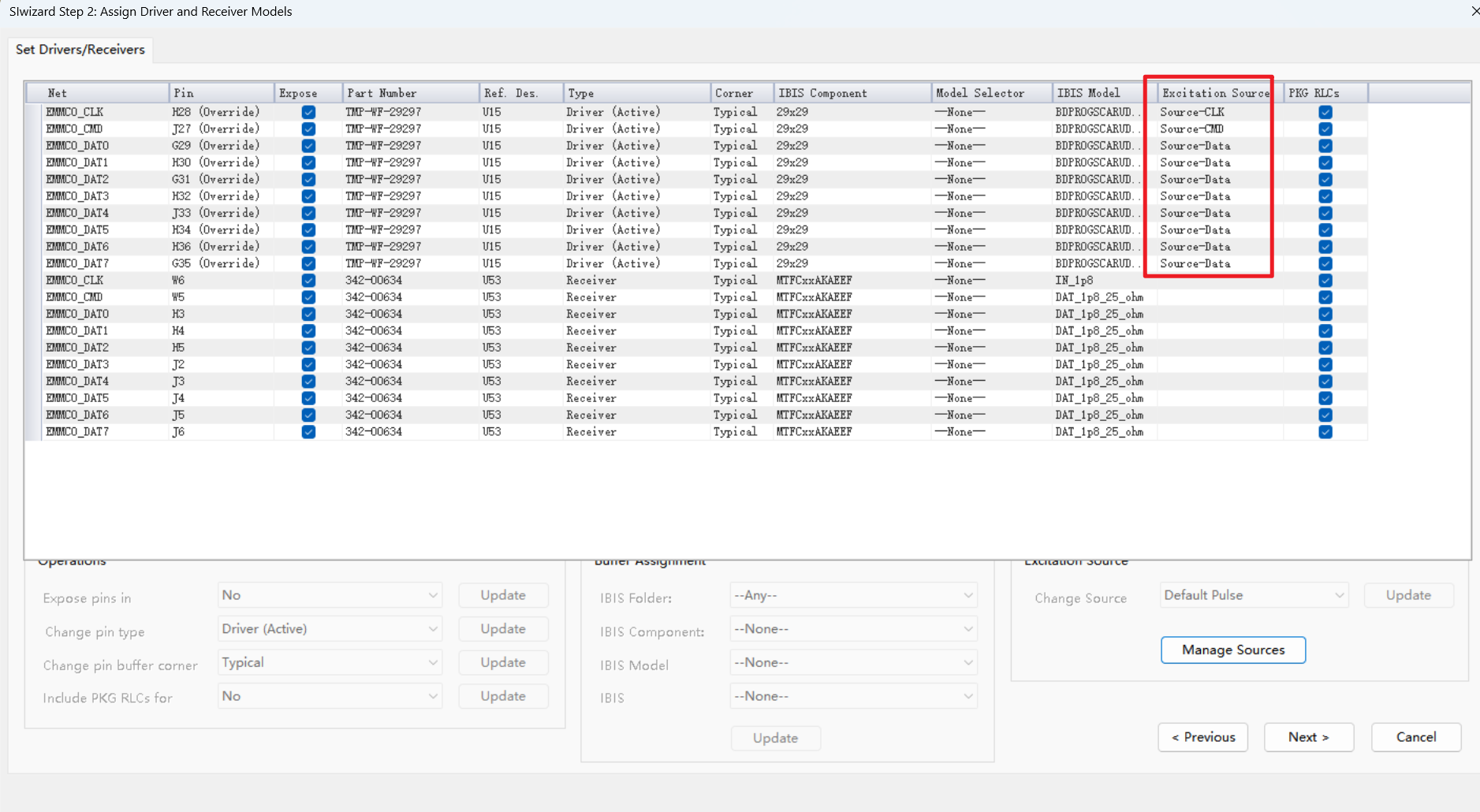

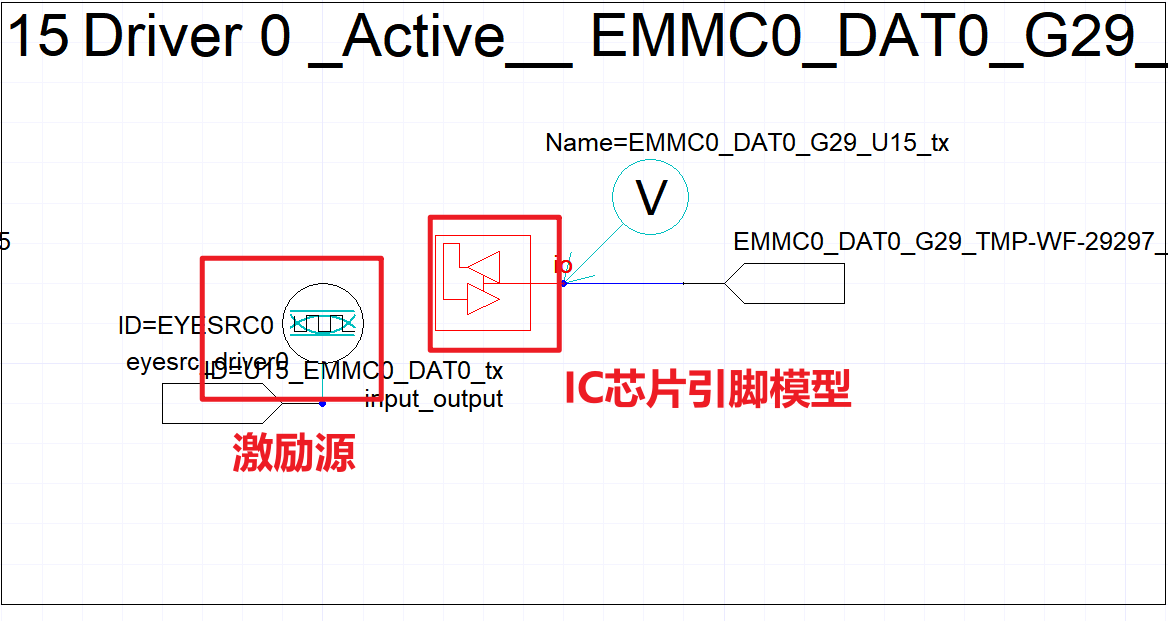

此处,需要仿真的内容是主芯片发送数据,EMMC芯片接收数据,因此需要设置主芯片(U15)侧的引脚为发送:

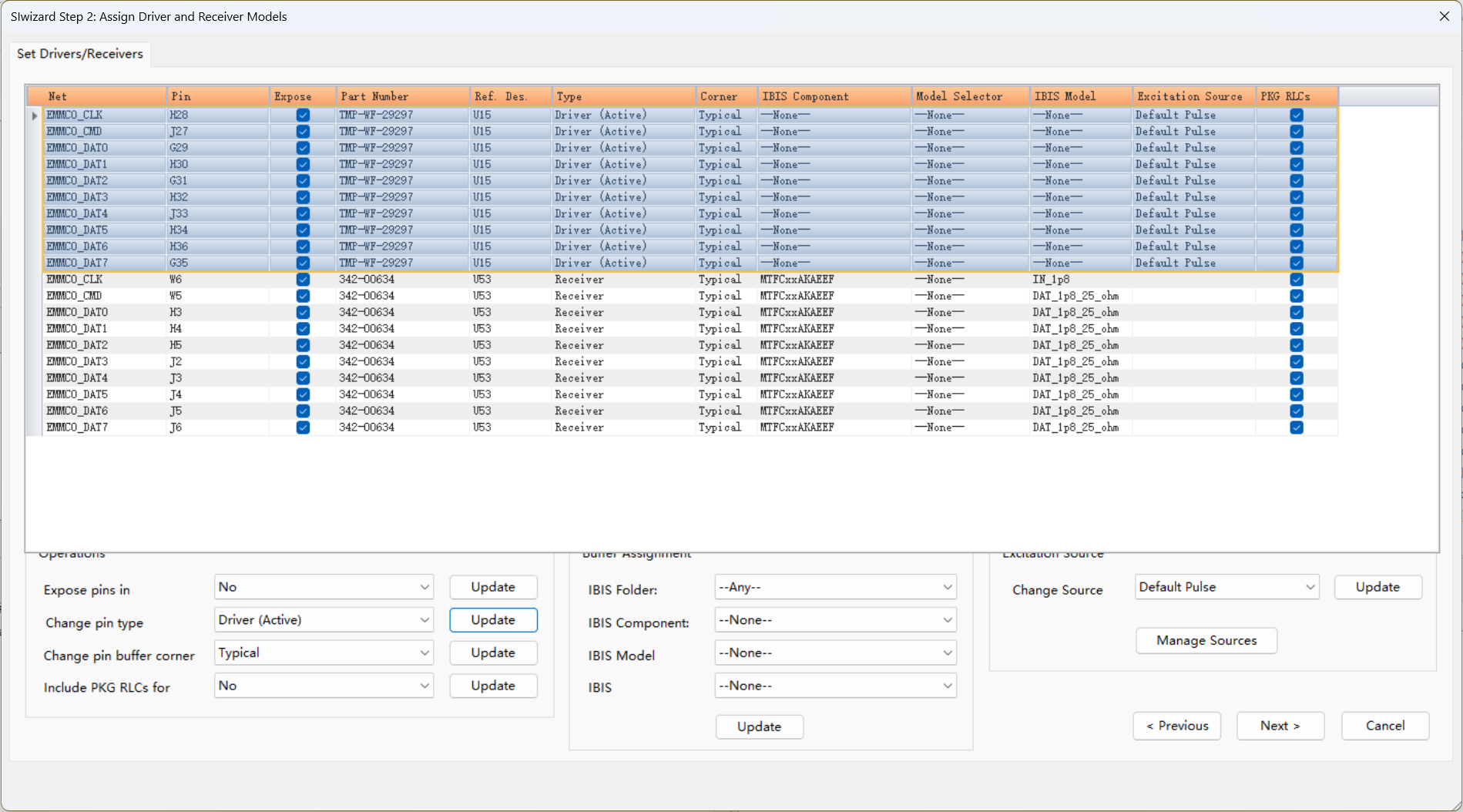

设置完成后如下所示:

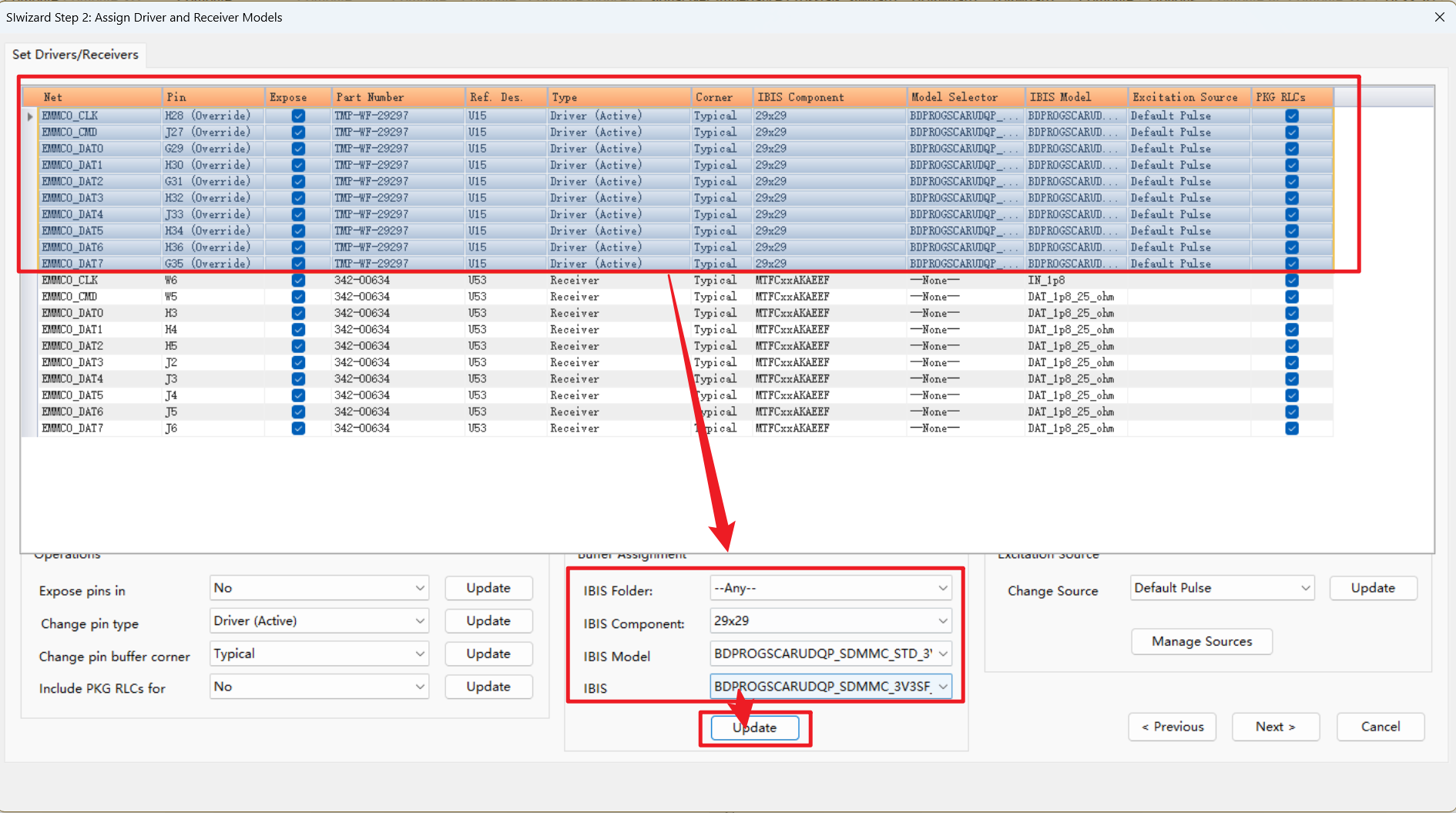

再配置好IBIS Model,设置为EMMC的:

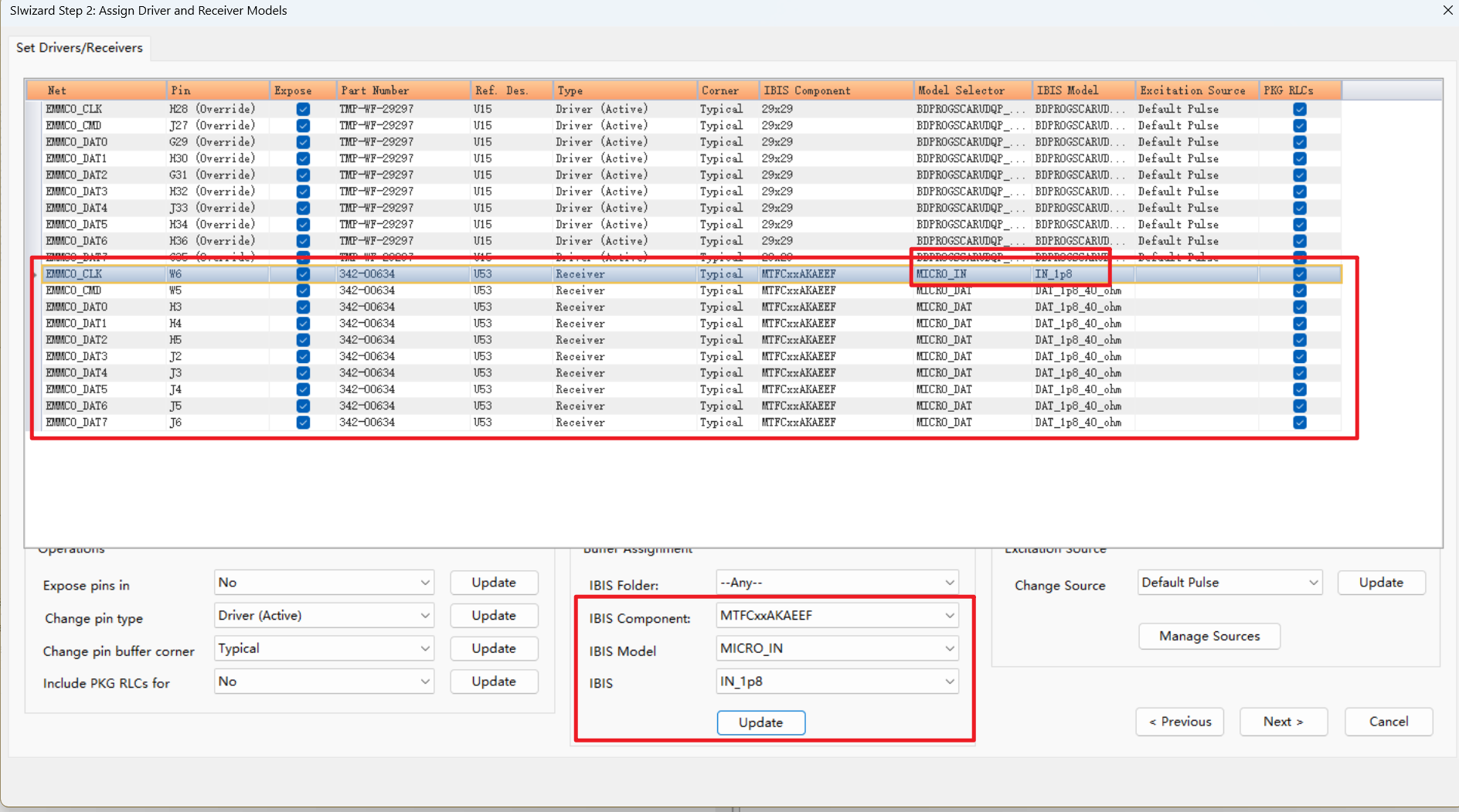

接下来设置好EMMC的模型,注意好时钟信号的设置和数据信号的设置存在差异的:

2.2、信号设置

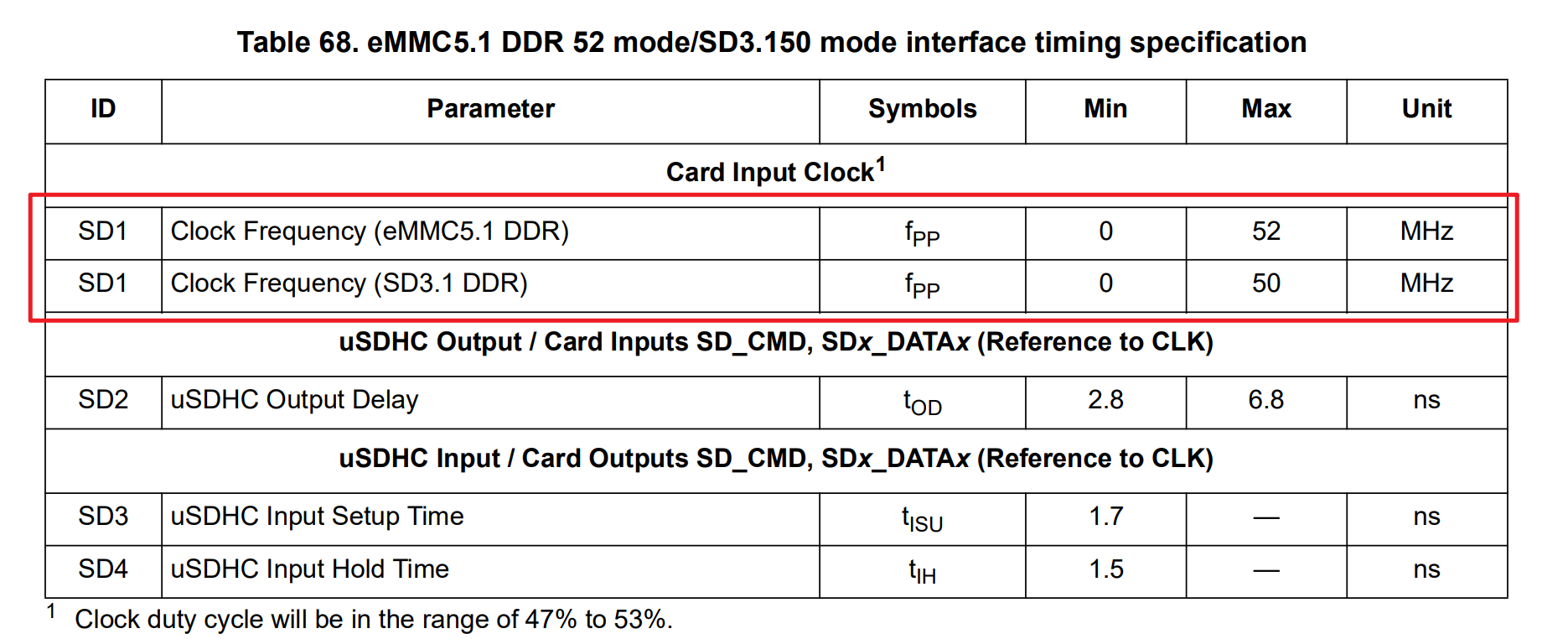

数字信号就是方波信号,需要在向导内设置合理的时钟频率,依据数据手册的内容,此处采用50MHz的时钟信号:

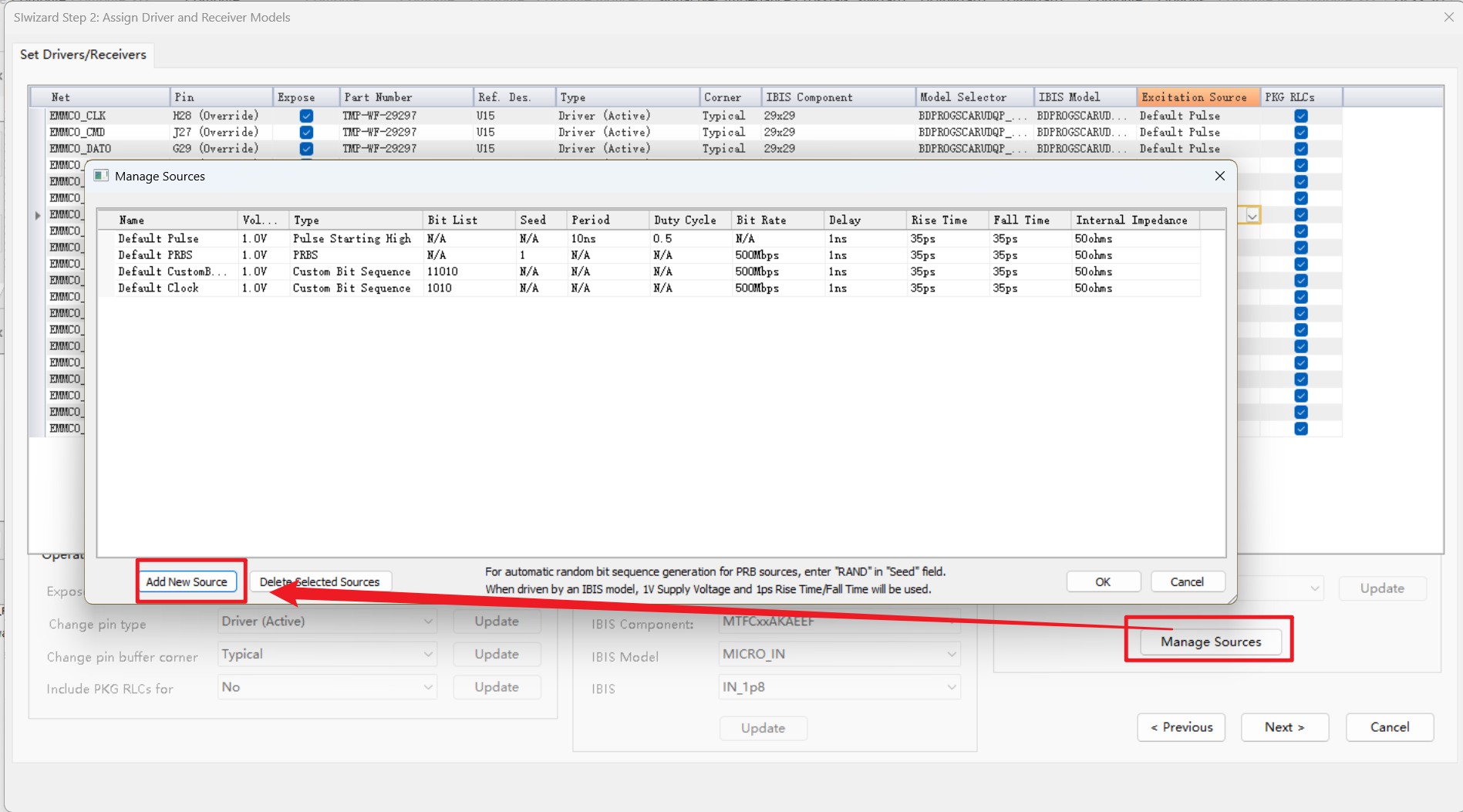

点击Manage Sources按钮进行源的添加与设置:

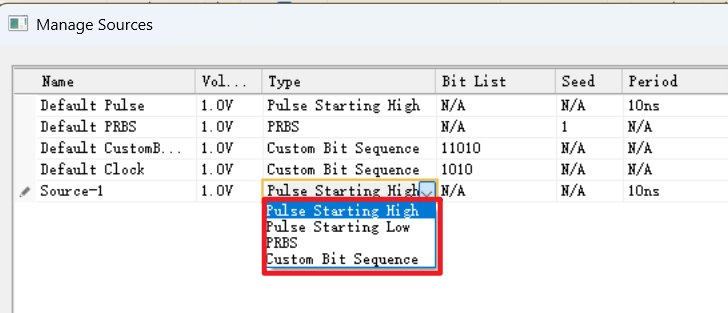

激励有如下的类型:

解释如下:

| 激励类型 | 信号特征 | 典型用途 | 关键作用 |

|---|---|---|---|

| Pulse Starting Low | 从低电平开始的单脉冲 | TDR、反射分析 | 观察阻抗不连续 |

| Pulse Starting High | 从高电平开始的单脉冲 | 边沿对称性分析 | 对比上/下降沿响应 |

| PRBS | 伪随机比特序列 | 眼图、BER、高速链路分析 | 模拟真实数据传输 |

| Custom Bit Sequence | 自定义比特序列 | worst-case、协议验证 | 分析特定模式下的信号完整性 |

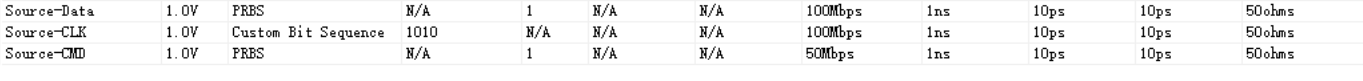

添加完成的激励源如下:

| 项目 | 设置值 | 原理说明 |

|---|---|---|

| Source-Data | PRBS | 数据线用伪随机序列,模拟真实DDR数据流,用于评估ISI、串扰和眼图 |

| Source-CLK | Custom Bit 1010 | 时钟用固定交替序列(1010),形成稳定周期方波,保证参考时序 |

| Source-CMD | PRBS | 命令线为单边信号况 |

基于上述添加的激励设置,给主芯片附加信号,随后点击下一步:

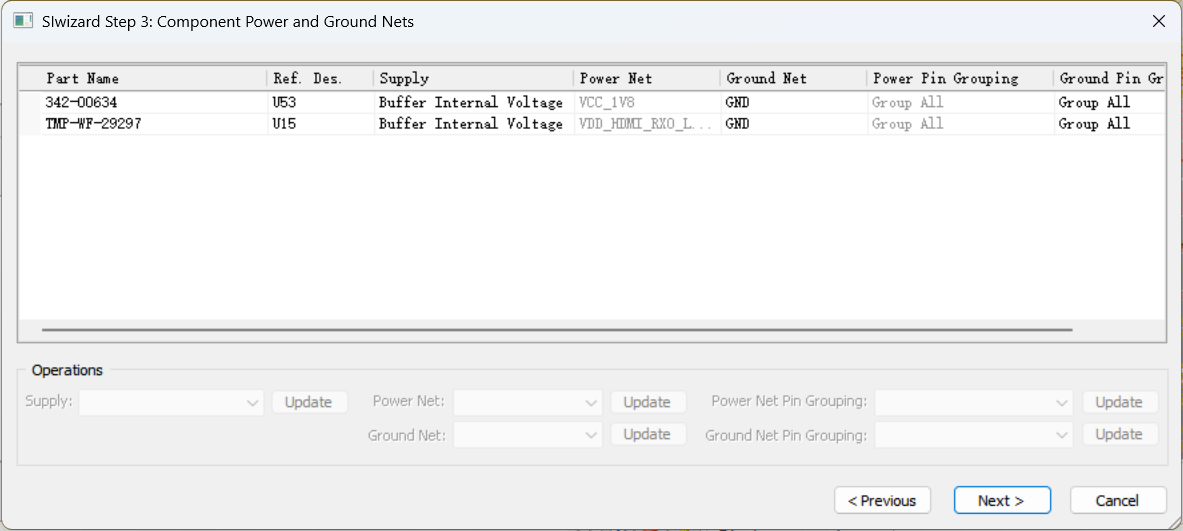

这一步无需更改,直接下一步即可:

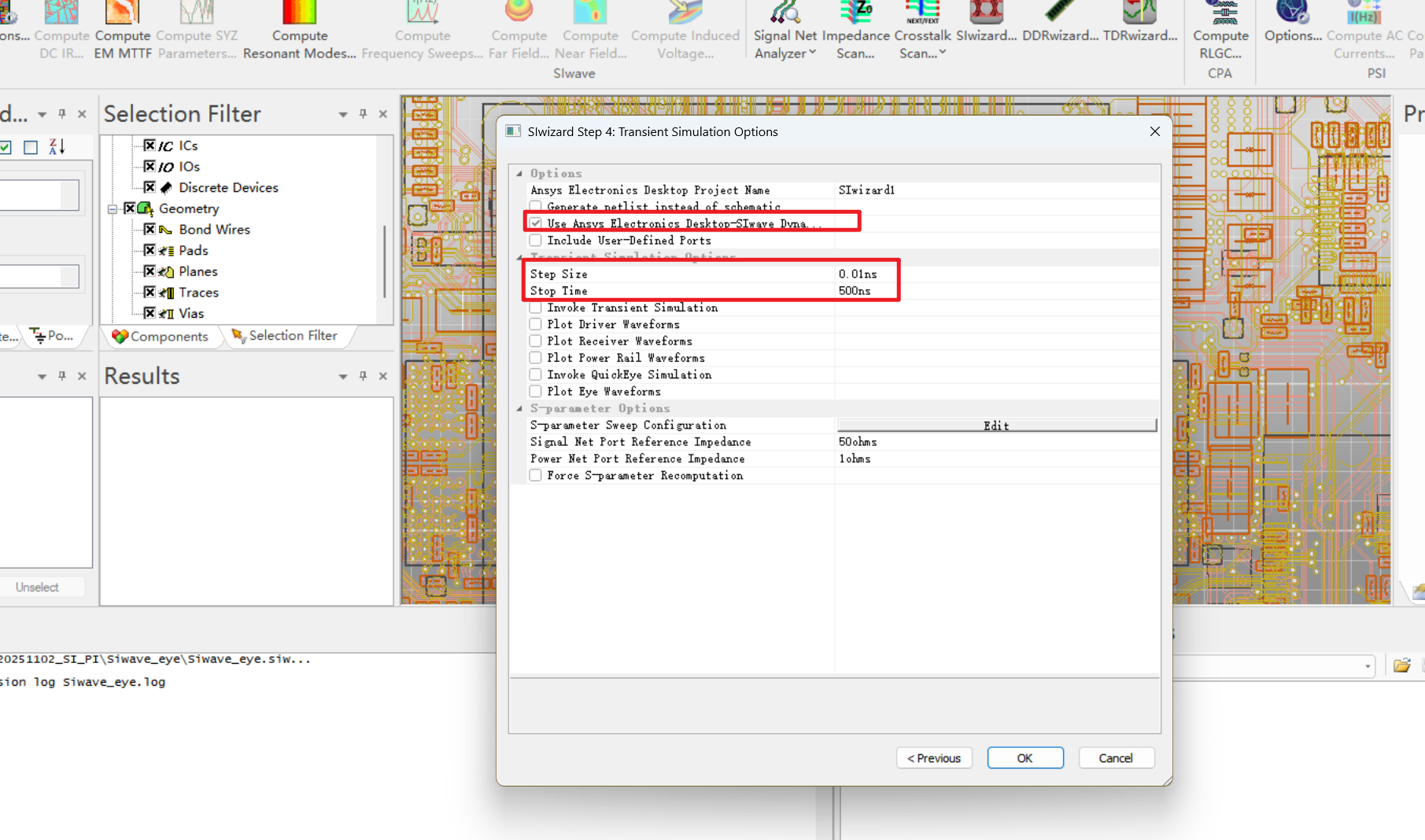

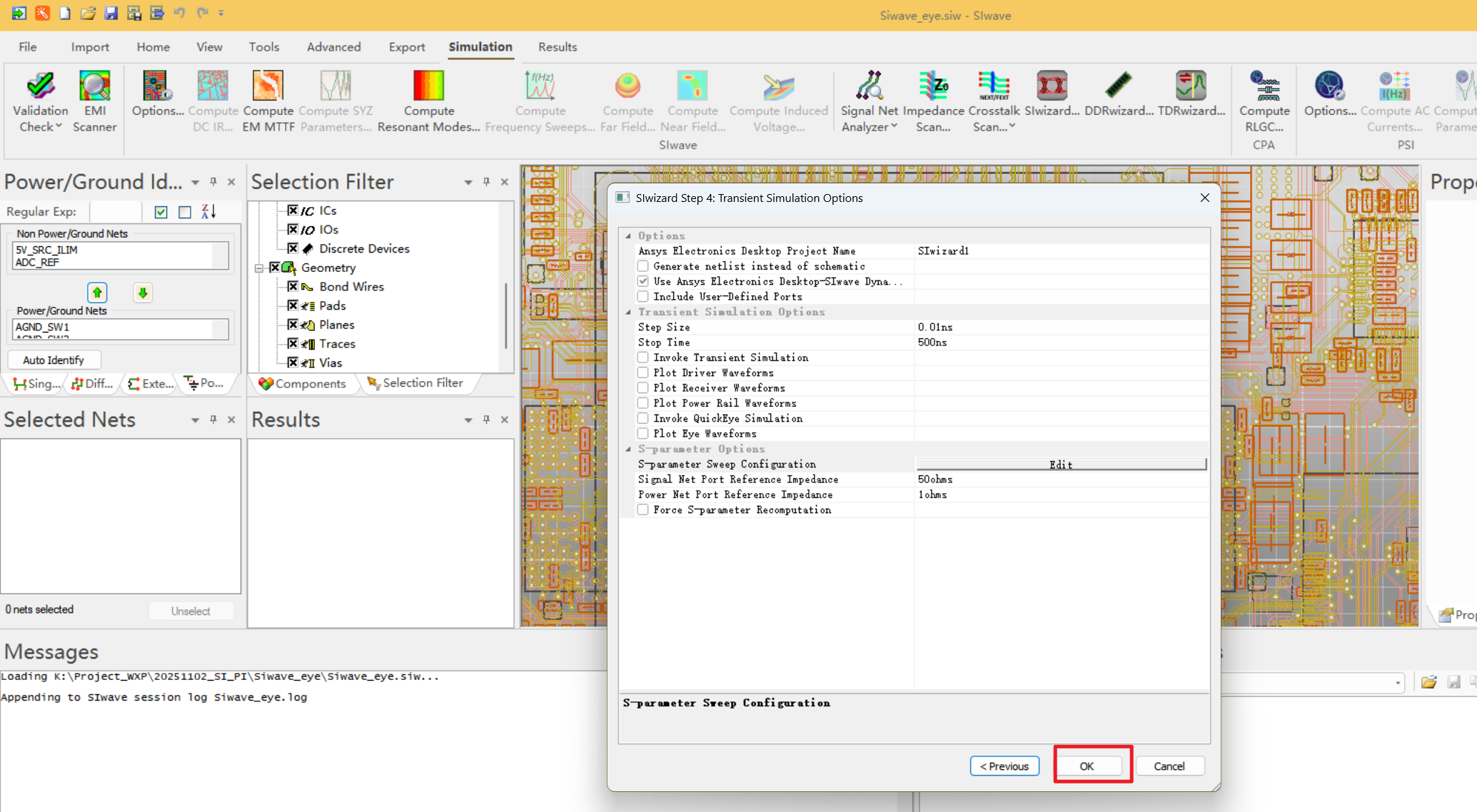

在这一步中,如下设置,我们的数据率是100Mbps,对应的时域时间是10ns,此处仿真50个bit,所需要的仿真时间是500ns:

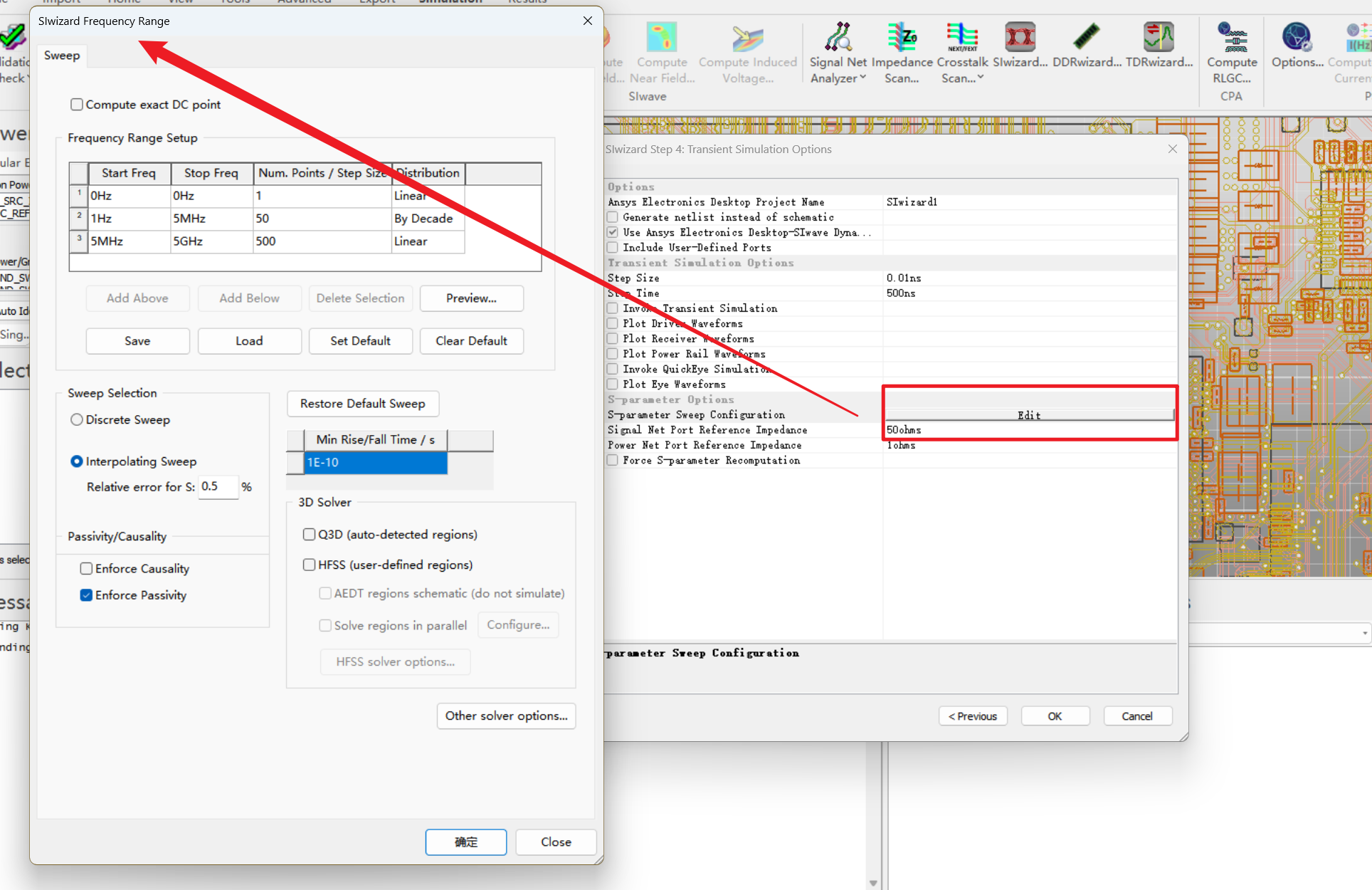

在S参数选项,需要打开查看下,此处仿真信号的速率只有50Mbps,仿真到5GHz是足够的了,此处不进行修改了:

全部设置完成点击OK:

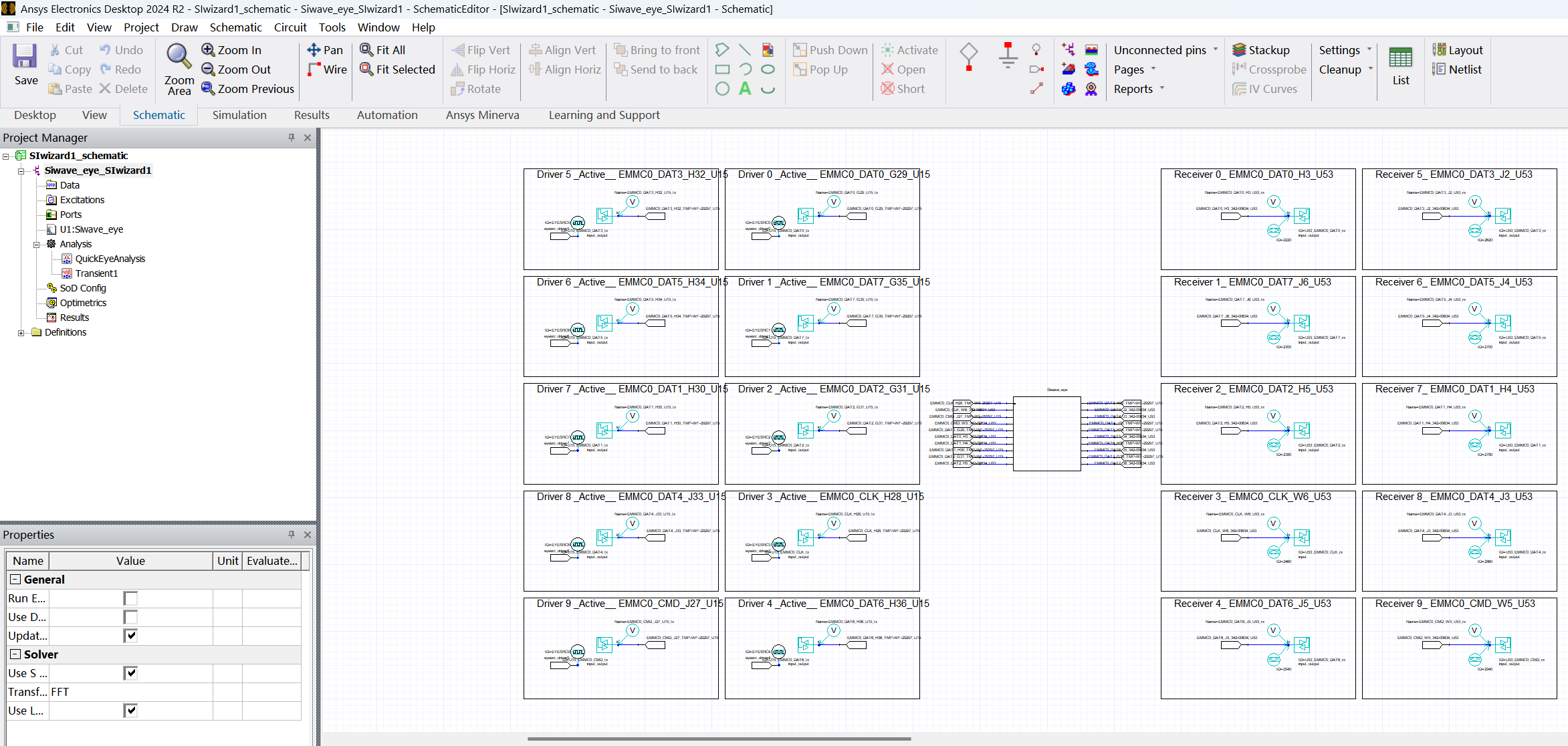

稍等一会,自动打开了界面:

2.3、启动仿真与结果查看

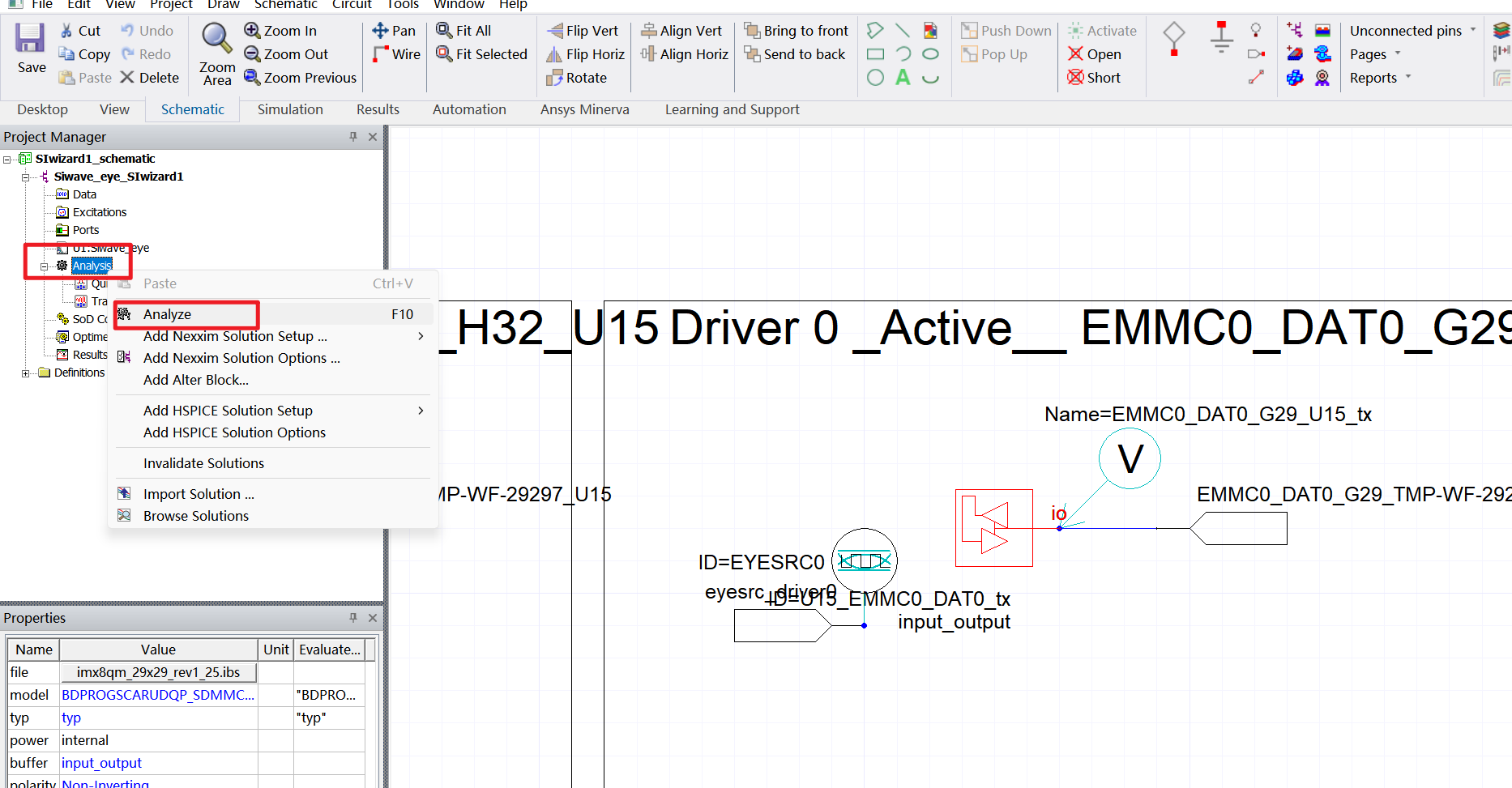

在弹出的界面右键启动仿真:

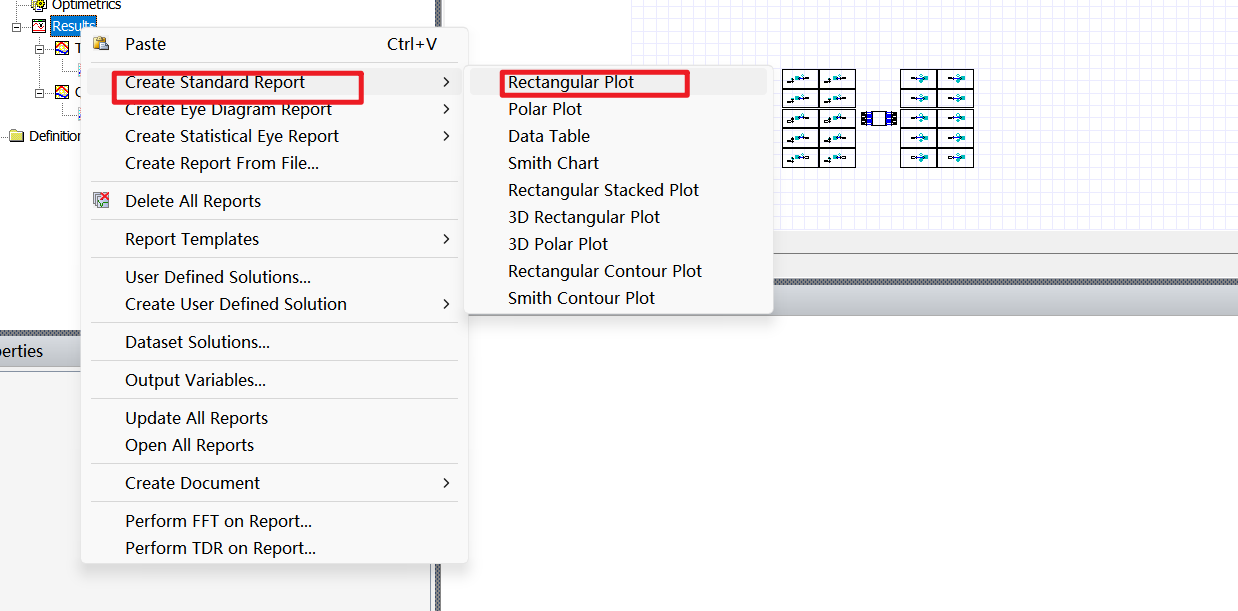

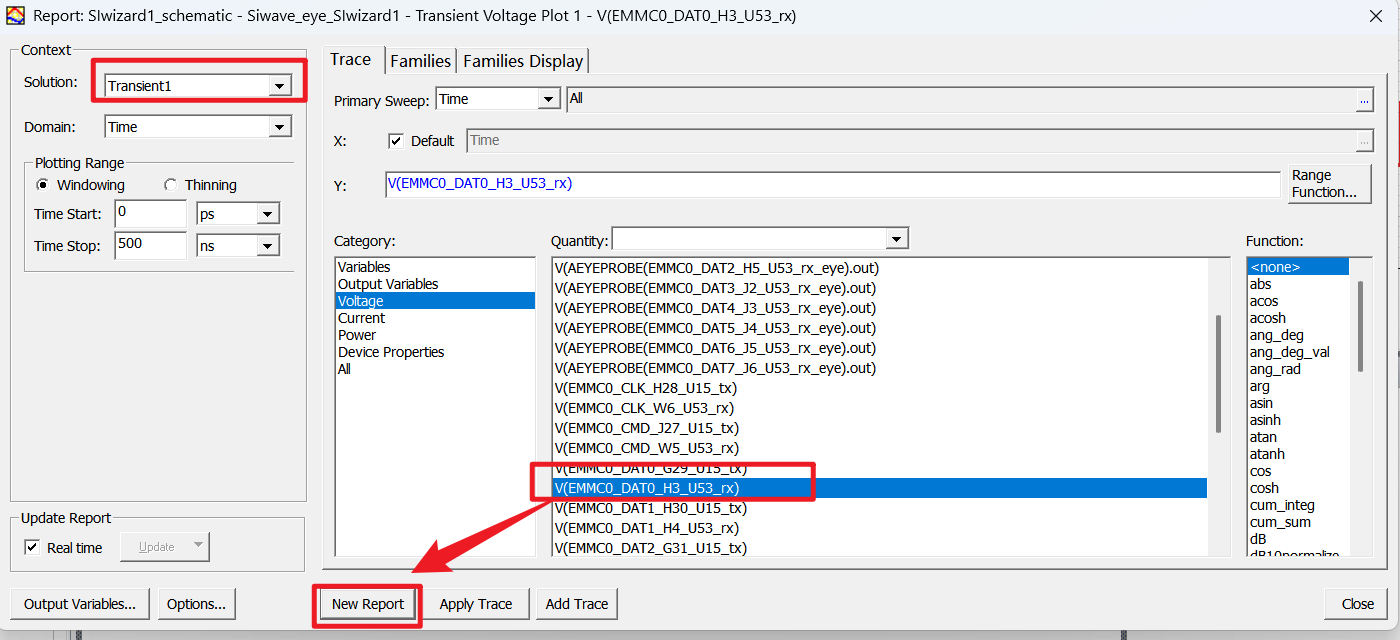

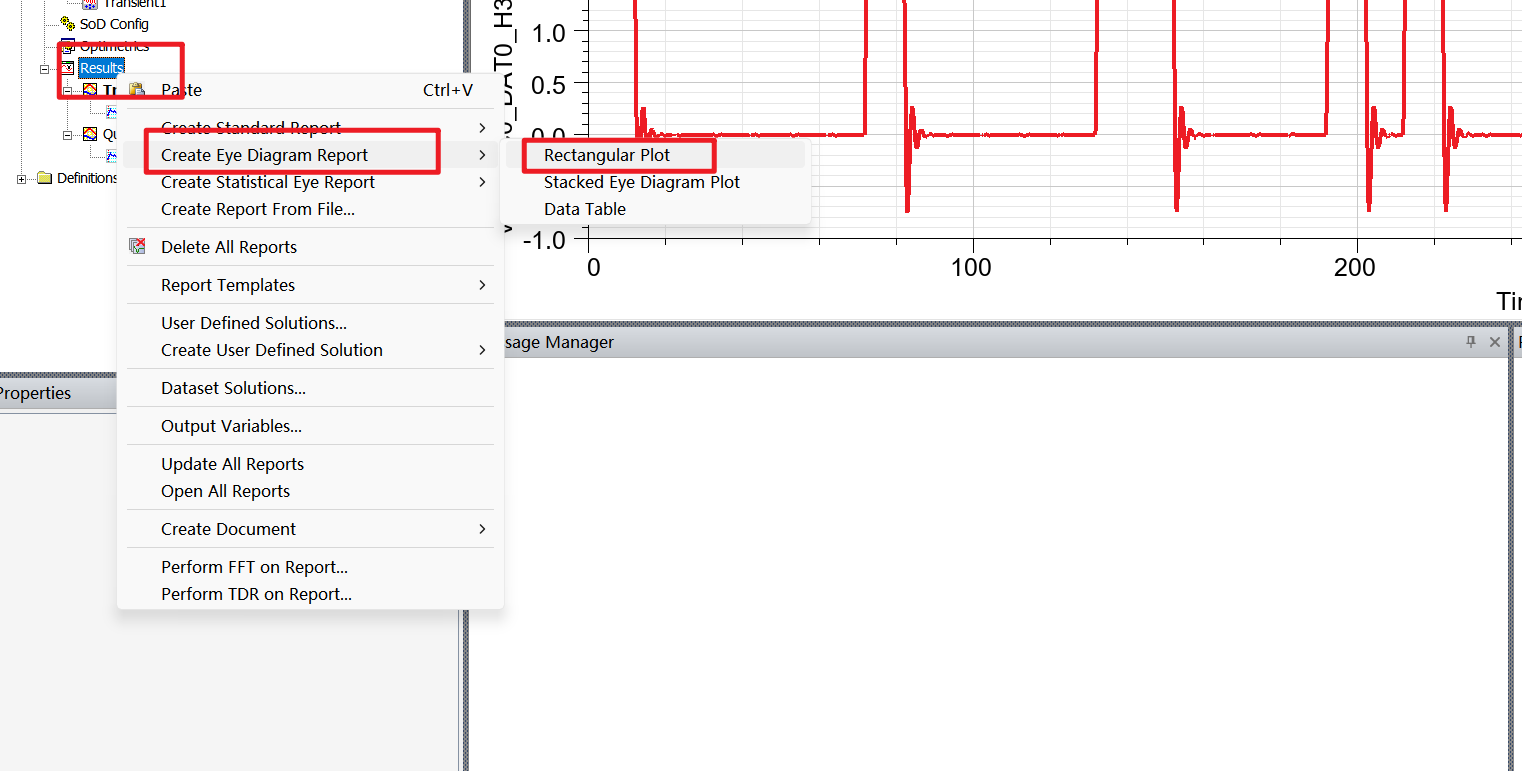

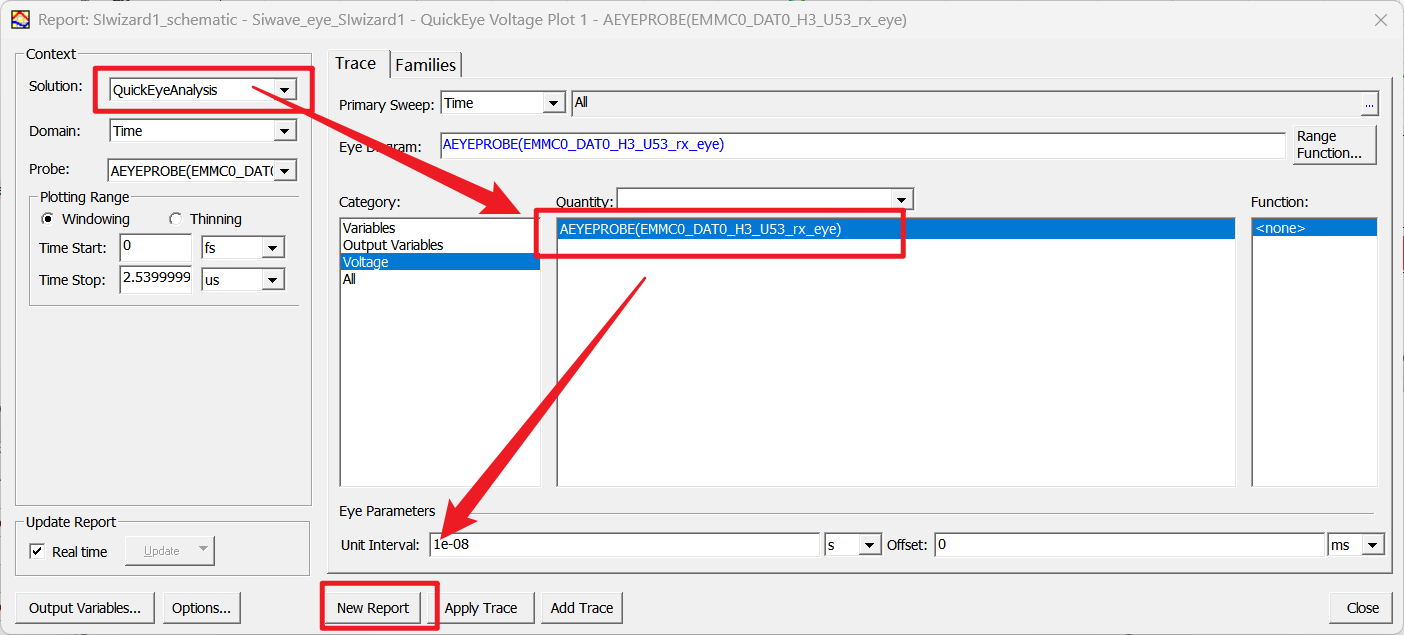

运行完成后添加图表进行查看,先看看EMMC端接收到的波形:

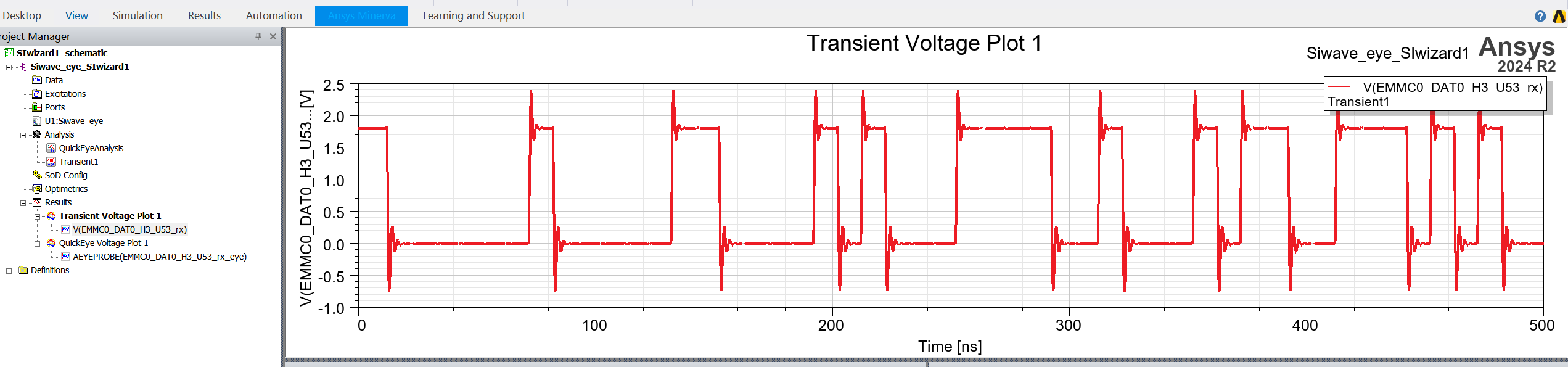

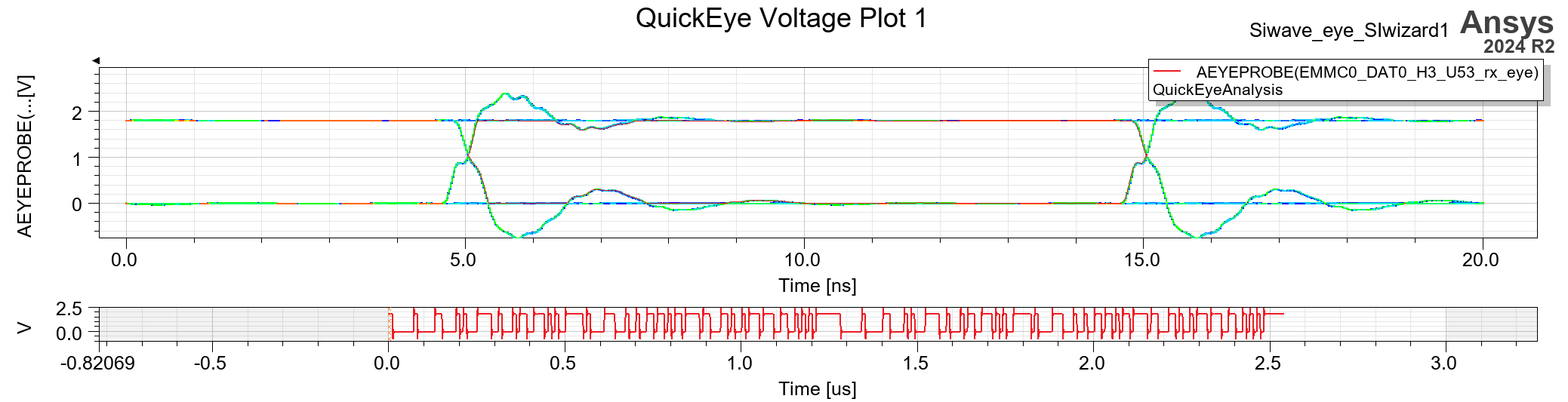

看看眼图,眼图本质上是在一个UI内同时观察电压裕量 和时间裕量 。

其中,眼高 主要反映噪声和幅度裕量,眼宽 主要反映抖动和时序裕量;而 ISI、反射、串扰、损耗 都会导致眼图闭合,从而增加误码风险。

具体解释如下:

| 类别 | 作用 | 典型参数 | 参数含义 | 工程判断 |

|---|---|---|---|---|

| 眼高(Eye Height) | 衡量电压方向开口大小 | Eye Height / Vertical Opening | 在最佳采样时刻,"1"和"0"之间可用的电压裕量 | 越大越好,小说明噪声、衰减、串扰或ISI较重 |

| 眼宽(Eye Width) | 衡量时间方向开口大小 | Eye Width / Horizontal Opening | 在判决门限附近可安全采样的时间裕量 | 越大越好,小说明抖动、ISI或时序裕量不足 |

| 交叉点 | 观察翻转位置是否稳定 | Crossing % / Crossing Voltage | 上升沿和下降沿的交叉位置,常看是否接近理想门限 | 偏移大说明占空比失真或上下拉不对称 |

| 抖动 | 衡量边沿时间不确定性 | Total Jitter、RJ、DJ | 边沿到达时间的散布,含随机抖动和确定性抖动 | 越小越好,过大会压缩眼宽 |

| 噪声 | 衡量电压波动 | Noise / Vertical Noise | 同一采样时刻电压分布的离散程度 | 越小越好,过大会压缩眼高 |

| 上升/下降时间 | 反映边沿快慢 | Rise Time / Fall Time | 信号从低到高、从高到低的转换速度 | 太快易反射和串扰,太慢易造成ISI |

| 过冲/下冲 | 观察阻抗不连续和振铃 | Overshoot / Undershoot | 波形超过高电平或低于低电平的幅度 | 过大说明反射、端接不佳或驱动过强 |

| 振铃 | 观察反射衰减情况 | Ringing | 边沿之后的持续摆动 | 明显振铃通常意味着阻抗失配 |

| 码间干扰 | 衡量前后比特相互影响 | ISI | 前一个或前几个比特拖尾影响当前比特 | ISI大会让眼图左右和上下都收缩 |

| 采样点 | 确定最佳判决时刻 | Sample Time / Decision Point | 接收端执行判决的最佳时间位置 | 通常选在眼图最开的位置 |

| 判决门限 | 确定"0/1"分界 | Threshold / Decision Level | 接收机区分高低电平的参考电压 | 设置不当会直接影响误码判断 |

| 误码趋势 | 综合评估链路质量 | BER Trend / Mask Margin | 根据眼图开口和统计分布估计误码风险 | 开口越大、越远离掩模,误码风险越低 |

| 掩模测试 | 判断是否满足规范 | Eye Mask / Mask Margin | 用标准禁止区域检查波形是否侵入 | 不碰掩模通常表示满足接口要求 |

| 测试激励 | 决定眼图覆盖场景 | PRBS、1010、自定义比特流 | 用什么数据模式激励通道 | PRBS更接近真实数据,1010更适合看单一翻转 |

| 通道损耗影响 | 反映链路带宽能力 | Insertion Loss 相关表现 | 高频损耗会让边沿变缓、眼图闭合 | 损耗越大,通常ISI越严重 |

| 串扰影响 | 反映相邻网络耦合 | NEXT / FEXT 相关表现 | 邻线开关引入的干扰叠加到被测线上 | 串扰大会降低眼高并扰乱采样 |