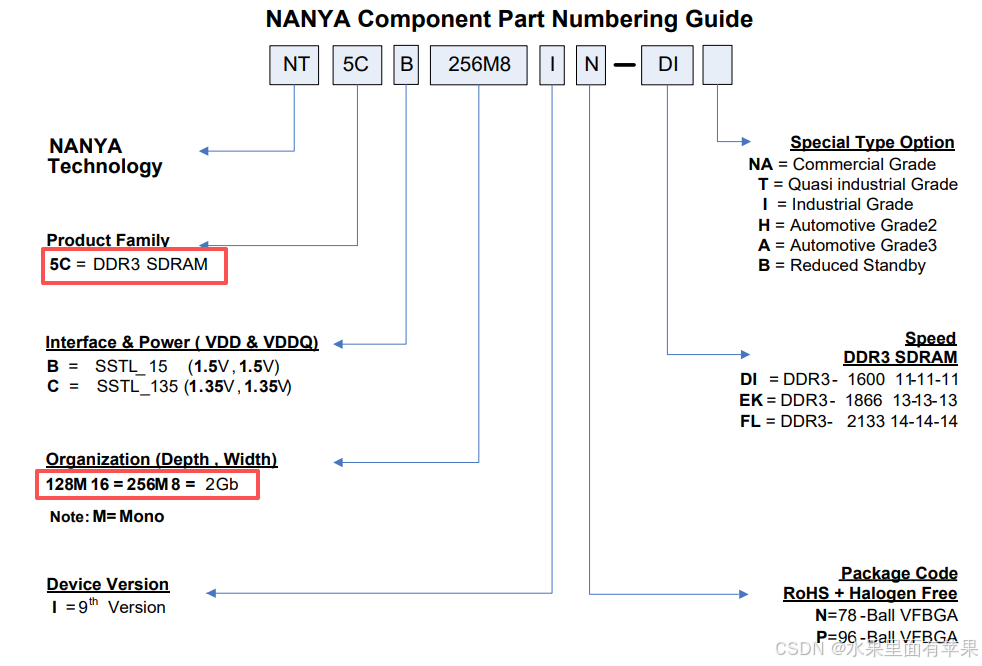

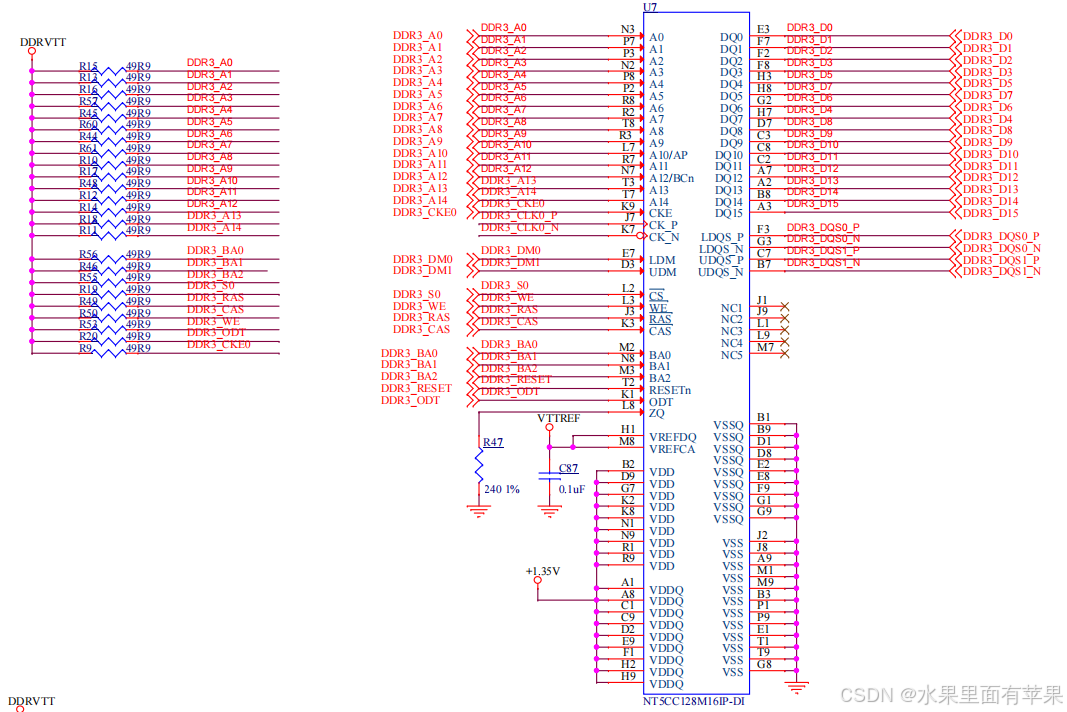

NT5CC128M16IP-DI DDR3芯片 2Gbit

芯片介绍

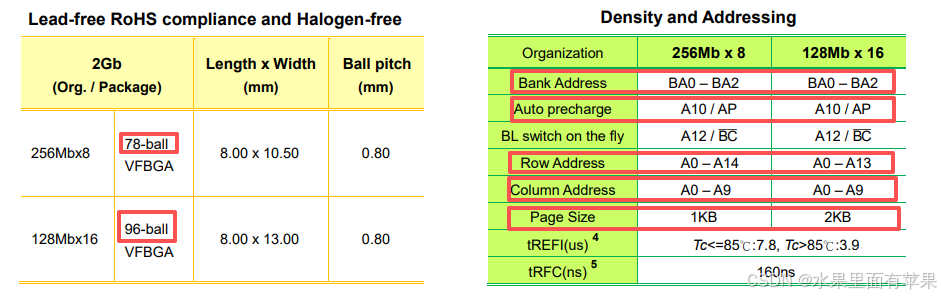

南亚科技生产的 2Gb (128M x 16) DDR3L SDRAM 芯片

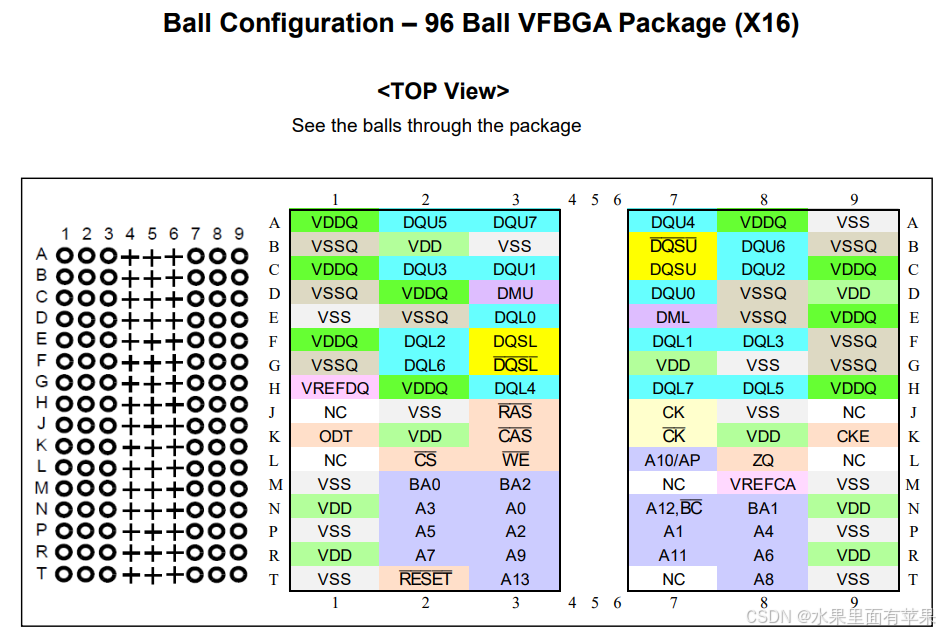

封装形式:VFBGA-96

关管脚功能说明

核心电源与地

- VDD / VDDQ (电源) :

- VDD :为核心逻辑电路(如地址解码器、控制逻辑等)供电,通常为 1.35V ±0.075V。

- VDDQ:为输出缓冲器(即数据输入/输出电路)供电,电压与VDD相同(1.35V)。分开供电有助于减少噪声干扰。

- VSS / VSSQ (地) :

- VSS:核心逻辑电路的地。

- VSSQ:输出缓冲器的地。

时钟与地址控制

- CK, CK# (差分时钟输入) :

- 所有命令和地址的采样都以此差分时钟的交叉点为参考。CK 为正相时钟,CK# 为反相时钟。DDR3采用差分时钟以提高抗噪性和时序精度。

- CKE (时钟使能) :

- 高电平时,使能内部时钟电路和输入缓冲器。低电平时,芯片进入低功耗状态(如自刷新或掉电模式)。这是实现节能的关键信号。

- CS# (片选) :

- 低电平有效。当CS#为高时,该芯片被"取消选中",所有命令被忽略。这是多芯片系统中选择特定芯片的关键信号。

命令输入

这三个信号共同构成命令,在时钟上升沿被采样。

-

RAS# (行地址选通) :

-

CAS# (列地址选通) :

-

WE# (写使能) :

* RAS#、CAS#、WE# 这三个信号的不同组合,在CS#有效时,定义了具体的操作命令,如激活(ACT)、读(RD)、写(WR)、预充电(PRE)、刷新(REF)等。

地址与存储体选择

- A[15:0] (地址输入) :

- 复用地址总线。在"激活"命令时,提供行地址 ;在"读/写"命令时,提供列地址和自动预充电位(A10)。

- 其中A10 在读写命令时有特殊功能:高电平表示操作后对该存储体执行自动预充电。

- A12 在刷新命令时用于选择自动刷新(REF)还是自刷新(SREF)。

- 其他高位地址(如A15, A14等)用于选择行。

- BA[2:0] (存储体地址输入) :

- 用于选择芯片内部的8个存储体(Bank)之一。每个存储体可以独立工作,提高并发效率。

- ODT (片上终端电阻使能) :

- 高电平时,在芯片内部为数据(DQ)和数据选通(DQS)信号启用终端电阻。这能改善信号完整性,特别是在高速运行时,减少PCB板上的反射,无需外接电阻。其值可通过模式寄存器设置。

数据输入/输出

- DQ[15:0] (数据输入/输出) :

- 16位双向数据总线。在读写操作时传输数据。采用源同步时序,与DQS信号边沿对齐。

- DQS, DQS# (差分数据选通) :

- 读操作时:由内存芯片产生,边缘与读出的数据(DQ)中心对齐。控制器用此信号来采集数据。

- 写操作时:由内存控制器产生,边缘与写入的数据(DQ)边缘对齐。内存芯片用此信号来采集控制器发来的数据。

- 与时钟类似,采用差分形式(DQS/DQS#)以提高抗噪性。

其他功能

- RESET# (复位) :

- 低电平有效。这是DDR3新增的重要功能。当RESET#为低时,强制终止所有操作,将芯片置于已知的闲置状态,不要求保持供电。用于快速初始化或从错误状态恢复。

- TDQS / TDQS# (终端数据选通) :

- 当芯片配置为x8模式时(此芯片是x16,此功能通常不使用),此引脚用作额外的数据选通终端。在x16模式下,此引脚应保持悬空或不连接(NC)。

- DM (数据掩码/写使能) :

- 对于此芯片,这个信号标注为"WOM"的可能性也存在,但标准名称是DM 。在写操作时,DM信号作为字节写入掩码。当DM为高时,对应的字节(对于x16芯片,每个DM对应一个字节,即8位)的数据在写入时被屏蔽(忽略)。在读操作时无效。

- 注意:有些DDR3芯片(特别是x16配置)可能有两个DM信号(如UDM、LDM),分别对应高字节和低字节。请务必以该芯片的官方数据手册为准。

空脚

- NC (No Connect) :

- 不连接。内部无电路,应保持悬空。

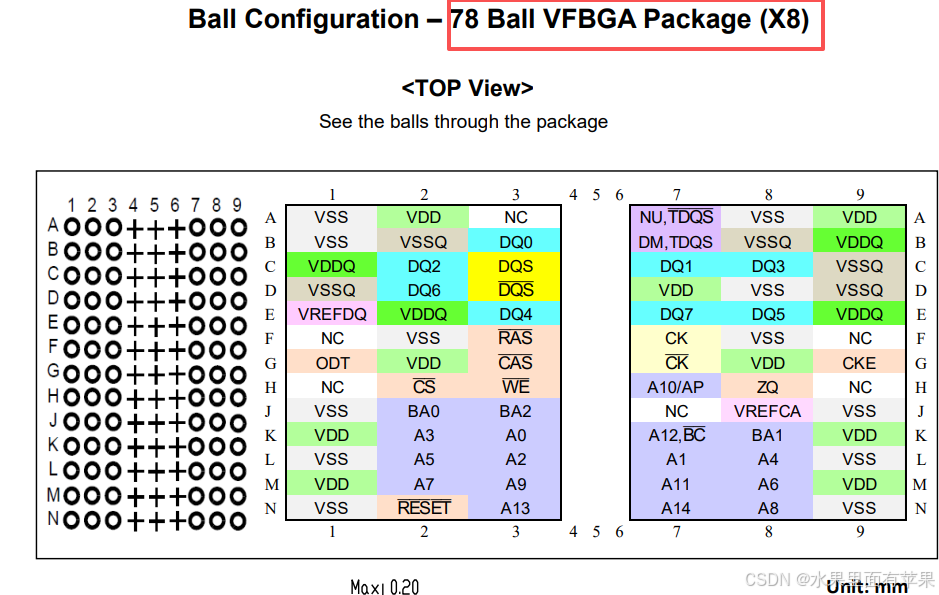

总结表格(以常见96-ball FBGA封装为例)

| 引脚类型 | 符号 | 名称与功能 | 关键说明 |

|---|---|---|---|

| 电源 | VDD, VDDQ | 核心与I/O电源 (1.35V) | |

| 地 | VSS, VSSQ | 核心与I/O地 | |

| 时钟 | CK, CK# | 差分系统时钟 | 所有动作的基准 |

| 控制 | CKE | 时钟使能 | 控制省电模式 |

| CS# | 片选 | 使能芯片 | |

| RAS#, CAS#, WE# | 命令输入 | 组合成具体命令 | |

| 地址 | A[14:0] | 复用地址总线 | 传送行/列地址 |

| BA[2:0] | 存储体地址 | 选择8个Bank之一 | |

| 数据 | DQ[15:0] | 双向数据总线 | 16位宽 |

| DQS, DQS# | 差分数据选通 | 读写数据的同步时钟 | |

| 特性 | ODT | 片上终端使能 | 改善信号完整性 |

| RESET# | 复位 | DDR3新增,强制初始化 | |

| DM (或 WOM) | 数据掩码 | 写操作时屏蔽字节 | |

| TDQS/TDQS# | 终端数据选通 | x16模式下通常为NC | |

| 空脚 | NC | 无连接 | 悬空即可 |

VREFCA 和 VREFDQ 分别是命令/地址总线和数据总线的参考电压。它们不是电源,而是用于判断输入信号逻辑"0"和"1"的判决门限。

• 它将接收到的信号(如 A0)与一个参考电压(VREF)进行比较。

• 如果信号电压 > VREF,则判为逻辑 '1'。

• 如果信号电压 < VREF,则判为逻辑 '0'。

ZQ引脚连接一个外部的高精度参考电阻,芯片内部电路通过这个电阻来"测量"和"调整"自己,确保其在各种工艺、电压、温度条件下,输出信号的电气特性始终符合规范。