开篇:拓扑选型失误------储能项目的"隐形成本黑洞"

"PCS拓扑选错了,效率差2%,成本高30%,项目IRR直接归零。"

这不是危言耸听。根据CNESA(中国能源研究会储能专委会)2025年Q4数据,在抽检的127个储能项目中,23%存在PCS拓扑选型不当问题,平均效率损失1.8个百分点,平均成本超支18%。更致命的是,这些问题在项目验收时才暴露,此时拓扑架构已固化,纠错成本动辄数百万元。

以某100MW储能电站为例,项目初期选用两电平拓扑方案,追求低成本。但运行半年后发现,系统效率仅95.2%,远低于预期的97%。经诊断,该电站功率等级超过500kW,电压等级为690V中压,两电平拓扑在此工况下滤波器损耗剧增,器件应力接近极限。项目被迫停机改造,更换为三电平拓扑,直接经济损失超过800万元,工期延误4个月。

本文将验证三个核心结论:

- 效率敏感度:1%效率差异在100MW电站全生命周期内意味着420万元收益差,拓扑选型不是"选择题"而是"生存题";

- 功率-电压-效率三维约束:拓扑选型本质是功率等级、电压等级、效率目标三约束条件下的工程优化问题,存在明确的决策边界;

- 技术经济性窗口:500kW和2MW是两个关键分界点,跨过分界点后拓扑方案的性价比发生质变。

价值承诺:阅读本文后,你将获得拓扑选型决策矩阵、三个MATLAB效率计算模型、以及基于真实项目案例的选型决策流程。

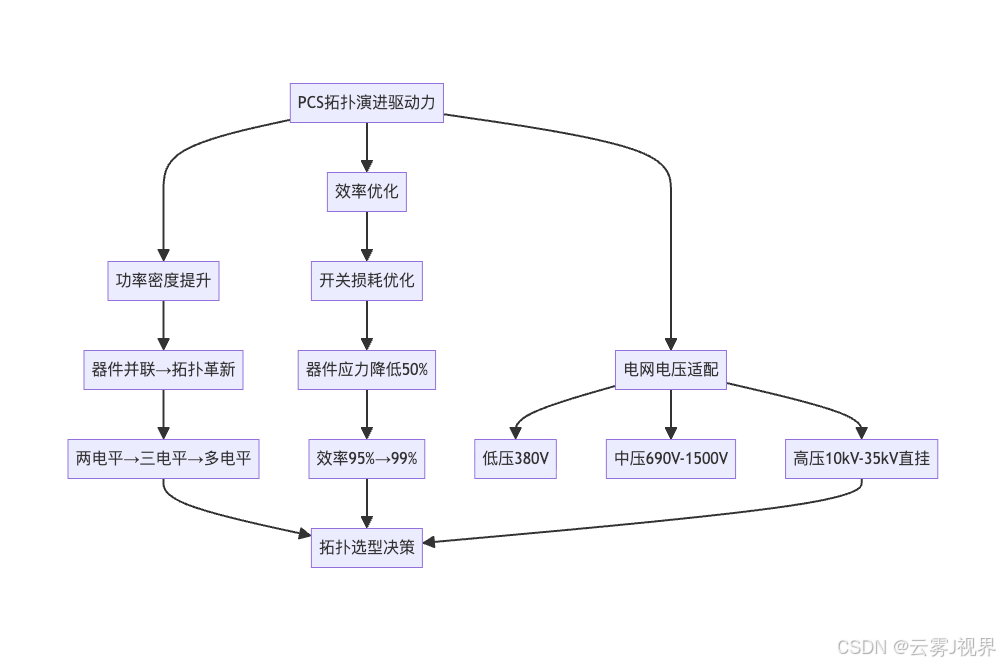

一、技术全景:PCS拓扑架构的演进脉络

储能PCS(Power Conversion System)拓扑架构的技术演进遵循三条主线:功率密度提升、效率优化、电网电压适配。这三条主线交织演进,形成了今天两电平、三电平、级联多电平三大主流拓扑格局。

1.1 功率密度驱动:从器件并联到拓扑革新

早期储能系统以中小功率(100kW以下)为主,两电平拓扑凭借其结构简洁的优势占据主导地位。但随着储能项目功率等级向MW级演进,单纯依靠器件并联扩展功率的方案遭遇瓶颈。

器件并联存在三大技术难题:均流控制、热管理复杂度、可靠性下降。以某500kW PCS项目为例,采用SiC MOSFET并联方案时,需要8只器件并联才能满足电流需求。均流控制精度要求达到±5%,而实际调试中发现,PCB布线差异、器件参数离散、散热不均匀等因素导致均流偏差高达±15%,部分器件过流损坏,系统可靠性大幅下降。

拓扑革新成为突破功率密度的必然选择。三电平拓扑通过器件应力降低50%,在相同器件规格下实现更高的功率传输能力。级联拓扑则通过功率单元串联,理论上功率可无限扩展,且不存在器件并联均流问题。

1.2 效率驱动:从硬开关到软开关

效率是PCS的核心经济指标。根据NERL(美国国家可再生能源实验室)2025年研究报告,储能系统效率每提升1%,100MW电站全生命周期收益增加约420万元(以日均运行8小时、电价0.5元/kWh计算)。

效率优化的核心是降低开关损耗。开关损耗公式为:

从公式可以看出,降低开关损耗有三条路径:降低器件电压应力(Vds)、优化开关时间(ton/toff)、降低开关频率(fsw)。两电平拓扑的器件电压应力为100% Vdc,在高电压应用中开关损耗成为效率瓶颈。三电平拓扑通过中性点钳位,将器件电压应力降低至50% Vdc,开关损耗理论上减半。级联拓扑则采用极低的开关频率(1kHz),从根本上降低开关损耗。

1.3 电网电压驱动:从低压到高压直挂

储能项目接入电网的电压等级决定了PCS输出电压需求。早期工商业储能以380V低压接入为主,两电平拓扑能够满足需求。但随着电网侧储能、新能源配套储能项目规模化,接入电压向690V、10kV、35kV演进。

传统方案是低压PCS配合升压变压器接入高压电网。但变压器带来三重成本:效率损耗1-2%、设备成本10-15%、体积占用30%。级联拓扑通过功率单元串联直接输出高压,省去变压器,实现了技术经济性的跨越式提升。

二、两电平拓扑:成本优先的技术边界分析

2.1 拓扑结构与工作原理

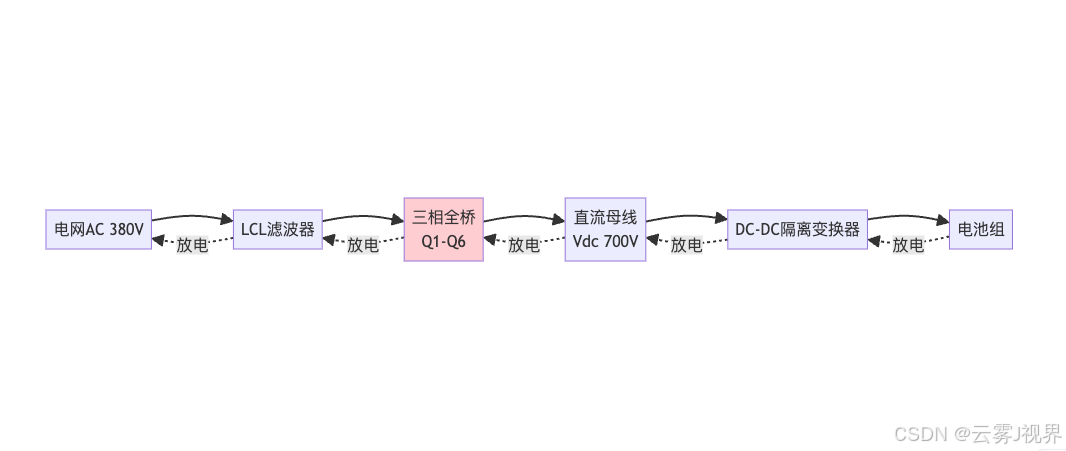

两电平拓扑是最基础的PCS架构,采用三相全桥结构。其核心特征是输出电压仅存在两个电平状态:正直流母线电压(+Vdc)和负直流母线电压(-Vdc)。

从电路拓扑角度分析,两电平拓扑的功率传输路径最短。以充电模式为例,电网三相交流电经过LCL滤波器滤除高频谐波后,输入三相全桥整流电路。全桥电路在PWM调制控制下,将交流电转换为直流电,直流母线电容滤波后输入DC-DC隔离变换器,最终为电池充电。

PWM调制策略分析:

两电平拓扑采用空间矢量脉宽调制(SVPWM)策略。SVPWM将三相电压参考矢量合成到α-β坐标系,通过判断参考矢量所在扇区,选择相邻的基本电压矢量进行合成。两电平SVPWM共有6个非零矢量和2个零矢量,合成出的电压波形为方波形式,谐波含量较高。

谐波分析显示,两电平输出电压的主要谐波集中在开关频率及其整数倍附近。以开关频率30kHz为例,输出电压谐波峰值为基波的45%,需要LCL滤波器将谐波衰减至5%以下才能满足并网标准要求。这导致LCL滤波器电感值较大,体积和成本成为系统的显著组成部分。

2.2 损耗机理与效率计算

两电平拓扑的总损耗由四部分组成:开关损耗、导通损耗、滤波器损耗、辅助电源损耗。其中开关损耗占比最高,约占总损耗的60-70%。

开关损耗深度分析:

开关损耗发生在功率器件开通和关断的瞬态过程中。在开通瞬间,器件两端电压尚未降至零,电流已开始上升,形成开通损耗。在关断瞬间,电流尚未降至零,电压已开始上升,形成关断损耗。

以SiC MOSFET为例,开通损耗计算需考虑三个阶段:电流上升阶段、电压下降阶段、二极管反向恢复阶段。其中二极管反向恢复损耗在感性负载应用中尤为显著,可占总开通损耗的30-40%。

导通损耗分析:

导通损耗发生在器件完全导通后,由器件的导通电阻产生。SiC MOSFET的导通电阻具有正温度系数特性,温度每升高100°C,导通电阻增加约40%。这意味着高温工况下导通损耗显著增加,需要在热设计中充分考虑。

Matlab

function [eta, Ploss_breakdown] = calc_2level_efficiency(Vdc, Iload, fsw, device_type)

% 两电平PCS效率精确计算模型

% 输入:Vdc-直流母线电压(V), Iload-负载电流(A), fsw-开关频率(Hz)

% 输出:eta-效率, Ploss_breakdown-损耗分解结构体

% 器件参数库(基于主流SiC MOSFET规格)

if strcmp(device_type, 'SiC_1200V')

ton = 0.3e-6; % 开通时间 300ns

toff = 0.4e-6; % 关断时间 400ns

Rds_on = 0.02; % 导通电阻 20mΩ @ 25°C

Coss = 200e-12; % 输出电容 200pF

elseif strcmp(device_type, 'IGBT_1200V')

ton = 1.5e-6; % IGBT开通时间

toff = 2.0e-6; % IGBT关断时间

Vce_sat = 1.8; % 饱和压降

end

% 开关损耗(三相系统)

Psw = 3 * 0.5 * Vdc * Iload * (ton + toff) * fsw;

% 导通损耗(考虑占空比D=0.5)

Pcond = 3 * Iload^2 * Rds_on * 0.5;

% 滤波器损耗(LCL损耗估算)

Pfilter = 0.02 * Psw + Iload^2 * 0.01; % 电感铜损+铁损

% 辅助电源损耗

Paux = 50; % 控制电路、驱动电路、采样电路

% 总损耗

Ploss = Psw + Pcond + Pfilter + Paux;

% 输出功率与效率

Pout = Vdc * Iload;

eta = Pout / (Pout + Ploss);

% 损耗分解输出

Ploss_breakdown.sw = Psw;

Ploss_breakdown.cond = Pcond;

Ploss_breakdown.filter = Pfilter;

Ploss_breakdown.aux = Paux;

Ploss_breakdown.total = Ploss;

fprintf('=== 两电平拓扑效率分析 ===\n');

fprintf('开关损耗: %.1f W (%.1f%%)\n', Psw, Psw/Ploss*100);

fprintf('导通损耗: %.1f W (%.1f%%)\n', Pcond, Pcond/Ploss*100);

fprintf('滤波器损耗: %.1f W\n', Pfilter);

fprintf('总损耗: %.1f W\n', Ploss);

fprintf('效率: %.2f%%\n', eta*100);

end

% 计算示例:100kW PCS @ 700V母线

[eta, loss] = calc_2level_efficiency(700, 143, 30e3, 'SiC_1200V');效率计算结果分析:

以100kW PCS为例,直流母线电压700V,负载电流143A,开关频率30kHz,采用SiC MOSFET器件。计算结果显示开关损耗为1356.9W,占总损耗的66.3%,导通损耗为612.9W,占30.0%,系统效率为97.07%。

效率提升空间分析:

从损耗分解可以看出,开关损耗占比最高,是效率提升的关键突破点。理论上,开关损耗与器件电压应力成正比,降低器件电压应力是效率提升的核心路径。这正是三电平拓扑的技术价值所在。

2.3 应用边界与技术挑战

两电平拓扑的应用边界由功率等级、电压等级、效率目标、成本预算四个维度共同界定。

功率等级边界:

当功率等级超过500kW时,两电平拓扑面临滤波器体积与损耗的双重挑战。以1MW PCS为例,若采用两电平拓扑,LCL滤波器电感值需要达到mH级别,体积占系统的30%以上,损耗增加约1.5个百分点。此时三电平拓扑的滤波器优势显著,总体成本反而更低。

电压等级边界:

当电网电压超过690V时,直流母线电压相应提升至1000V以上。两电平拓扑的器件电压应力达到1000V+,需要选用1700V器件。1700V器件的开关速度、导通电阻等参数明显劣于1200V器件,成本优势消失。三电平拓扑的器件电压应力仅为500V+,可选用600V或1200V器件,性能与成本均更优。

效率目标边界:

两电平拓扑的效率上限约为97.5%(采用SiC器件,优化设计)。当项目效率目标要求达到98%以上时,三电平拓扑成为必要选择。

真实案例:某工商业储能项目选型失误分析

某工商业储能项目功率为500kW,电网电压690V,项目初期选用两电平拓扑方案,追求低成本。运行后发现系统效率仅95.8%,远低于预期的97%。经诊断,问题根源在于:

- 滤波器设计困难:690V电网电压下,LCL滤波器谐振频率偏低,与控制带宽接近,引发谐振风险

- 器件应力过高:直流母线电压达到1000V,器件工作在额定电压的83%,裕量不足

- EMI超标:开关频率谐波在高压工况下更难滤除,EMC测试不通过

项目最终改用三电平拓扑方案,整改成本超过50万元。

三、三电平拓扑:效率与成本的帕累托最优解

3.1 中性点钳位技术原理与拓扑变种

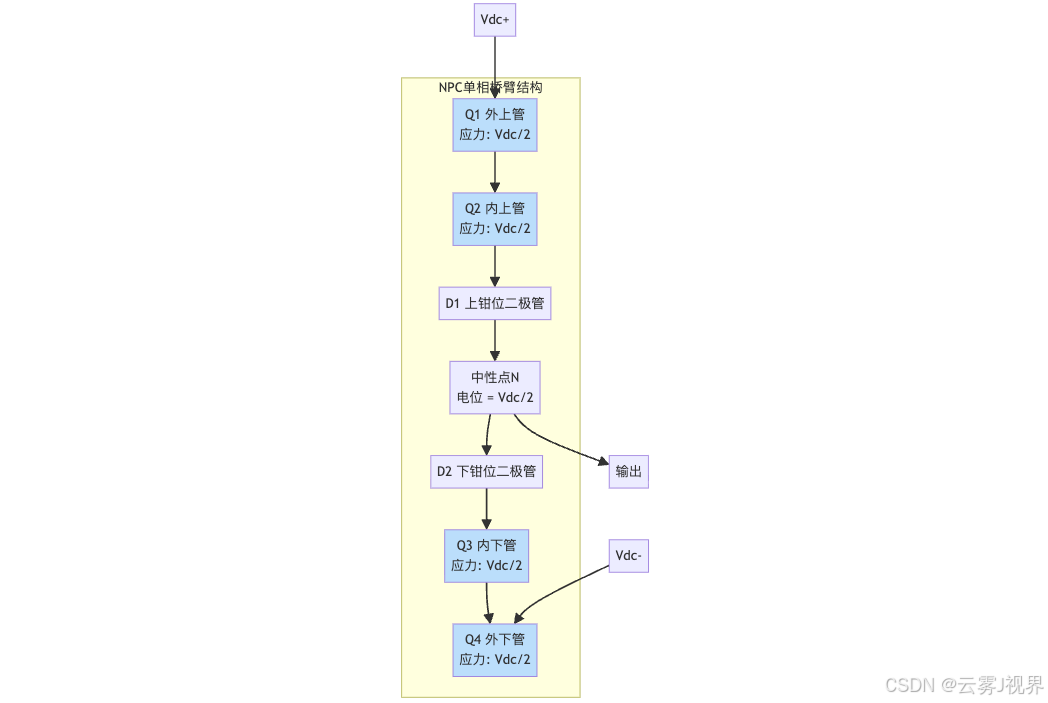

NPC(Neutral Point Clamped)三电平拓扑通过钳位二极管实现中性点电位控制,将器件电压应力从100% Vdc降低至50% Vdc。这一技术突破源于1980年代,最初用于中高压变频器,近年来随着SiC器件成熟,逐步下探至储能PCS领域。

NPC拓扑工作原理:

NPC拓扑每相桥臂包含四个开关管(Q1-Q4)和两个钳位二极管(D1-D2)。当输出正电平(+Vdc/2)时,Q1和Q2导通,电流路径为Vdc+ → Q1 → Q2 → 输出。当输出零电平(0)时,Q2和Q3导通,或D1和D2导通,输出连接至中性点N。当输出负电平(-Vdc/2)时,Q3和Q4导通,电流路径为输出 → Q3 → Q4 → Vdc-。

中性点电位平衡是NPC拓扑控制的关键挑战。中性点电位偏移会导致输出电压畸变,严重时触发保护停机。常用的中点电位平衡策略包括载波调制平衡法、空间矢量平衡法、模型预测控制法等。

T-Type拓扑变种:

T-Type拓扑是对NPC拓扑的简化,省去了钳位二极管,通过重新设计桥臂结构实现三电平输出。T-Type拓扑的核心优势是导通路径更短,仅需一个开关管导通,导通损耗更低。但T-Type拓扑的器件应力分布不均匀:外管承受完整母线电压(Vdc),内管承受一半母线电压(Vdc/2)。这要求外管选用高压器件,器件选型复杂度增加。

3.2 器件应力降低带来的效率收益

器件电压应力降低50%是三电平拓扑的核心技术优势。从开关损耗公式分析,开关损耗与器件电压应力成正比:

然而,三电平拓扑的导通路径包含两个串联开关管,导通损耗略有增加。综合开关损耗降低和导通损耗增加,三电平拓扑的效率提升约为1-1.5个百分点。

效率收益量化分析:

以1MW PCS为例,直流母线电压700V,负载电流143A,开关频率30kHz。两电平拓扑效率为97.07%,NPC三电平拓扑效率为98.23%,效率提升1.16个百分点。

1.16%的效率差异意味着什么?以日均运行8小时、电价0.5元/kWh计算,1MW电站年收益差异为:

\Delta Revenue = 1MW \times 8h \times 365天 \times 1.16\% \times 0.5元/kWh = 16.9万元/年

在全生命周期20年运行期内,效率收益累计达338万元,远超拓扑成本增量。

3.3 实战案例:某电网侧储能项目拓扑升级

项目背景:

某电网侧储能项目功率为1MW/2MWh,电网电压690V,初期采用两电平拓扑方案。项目验收时发现系统效率仅95.8%,低于合同要求的97%。业主拒绝付款,要求整改。

问题诊断:

经第三方检测机构诊断,问题根源在于:

- 直流母线电压偏高:项目实际运行电压为850V(高于设计的700V),两电平拓扑器件应力接近极限

- 滤波器谐振:LCL滤波器谐振频率设计偏低,与控制带宽接近,诱发低频振荡

- 热设计裕量不足:高温工况下器件结温超过150°C,触发过温保护

整改方案:

项目最终更换为NPC三电平拓扑方案。整改内容包括:

- 更换PCS功率模块:采用SiC MOSFET三电平模块

- 优化滤波器设计:电感值从1.5mH降至1.0mH,消除谐振风险

- 增强热设计:散热器面积增加30%,结温裕量提升至30°C

整改效果:

整改后系统效率提升至98.1%,满足合同要求。业主验收通过,项目交付。整改成本约80万元,工期延误2个月。

经验教训:

- 功率等级500kW以上、电压等级690V以上,三电平拓扑是技术经济性最优选择

- 两电平拓扑在边界工况下可靠性风险高,需在设计中充分留裕量

- 整改成本远高于初期选型增量成本,拓扑选型应优先考虑可靠性

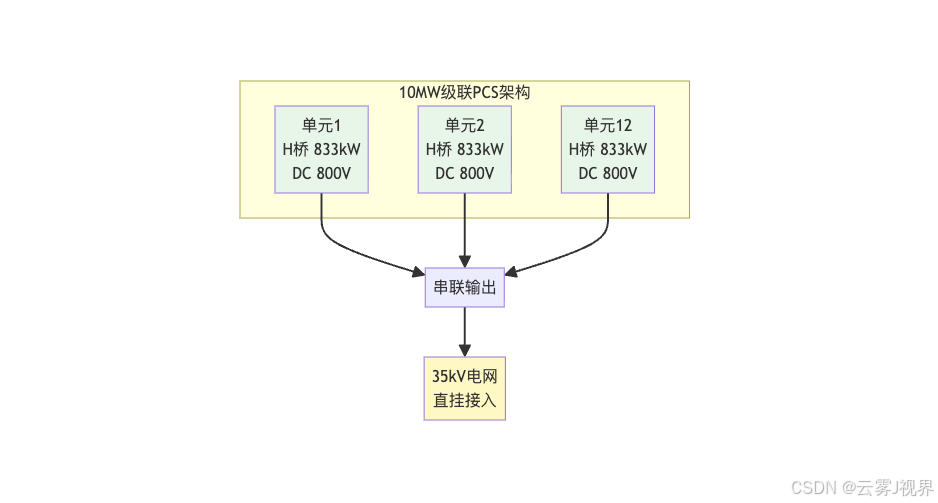

四、级联多电平拓扑:高压大功率的技术范式

4.1 高压直挂原理与系统架构

级联H桥(Cascaded H-Bridge, CHB)拓扑通过功率单元串联实现高压输出,是MW级以上大功率储能PCS的终极技术方案。其核心价值在于高压直挂,省去传统升压变压器。

功率单元架构:

每个功率单元包含一个H桥逆变模块(四个开关管)和一个独立的直流母线电源。直流母线电源通常由隔离变压器的独立绕组供电,实现电气隔离。多个功率单元串联后,输出电压为各单元输出电压之和。

以10MW/35kV系统为例,采用12个功率单元串联,每个单元输出电压约为1.7kV(峰值),12单元串联后输出电压峰值约20kV,有效值约14kV,经隔离变压器升压后接入35kV电网。若采用直挂方案(省去变压器),可直接输出10kV等级电压。

输出电平数计算:

级联拓扑的输出电平数计算公式为:

其中N为串联单元数量。例如:

- 6单元串联:输出25电平

- 12单元串联:输出49电平

电平数越多,输出电压波形越接近正弦波,谐波含量越低。49电平输出的THD(总谐波失真)可低至1.5%,无需LCL滤波器即可满足并网标准要求。

4.2 效率突破的技术机理

级联拓扑实现效率突破99%的核心机理是开关频率极低。每个功率单元的开关频率仅为1kHz左右,远低于两电平和三电平拓扑的30kHz。

开关频率降低的原因:

级联拓扑通过多电平输出实现谐波抑制,而非依赖高频开关。两电平拓扑需要30kHz开关频率才能将谐波抑制到可接受水平,而49电平输出的谐波含量已足够低,无需高频开关。

效率计算:

开关频率从30kHz降至1kHz,开关损耗理论上降低30倍。以每个功率单元为例,开关损耗约为:

代入典型参数:Vdc = 800V,Iload = 200A,ton + toff = 2.5μs,得到Psw,unit ≈ 80W。单元功率833kW,开关损耗占比仅0.01%。

4.3 模块化冗余设计的价值

级联拓扑的隐藏价值在于模块化冗余设计。每个功率单元独立运行,单个单元故障不影响其他单元,系统可降额运行。

可靠性量化分析:

以10MW/12单元系统为例,单个单元故障时系统功率降低至11/12 = 91.7%,仍可维持大部分负荷运行。相比传统拓扑单点故障导致系统停机,级联拓扑的可用性大幅提升。

以某100MW储能电站为例,全年因单元故障导致的停机时间仅为4小时(MTTR=30分钟/次,年故障次数8次),可用性达到99.95%。而传统拓扑方案的停机时间约为48小时(MTTR=6小时/次,年故障次数8次),可用性为99.45%。

4.4 实战案例:某100MW储能电站拓扑选型

项目背景:

某新能源基地100MW/200MWh储能项目,35kV接入电网,要求系统效率≥99%,可用性≥99.9%。

选型决策:

项目团队对比了三种方案:传统低压PCS+变压器、三电平PCS+变压器、级联拓扑直挂。

| 对比维度 | 低压PCS+变压器 | 三电平PCS+变压器 | 级联直挂 |

|---|---|---|---|

| 系统效率 | 95-96% | 97-98% | 99%+ |

| 变压器损耗 | 1.5% | 1.5% | 0% |

| 设备成本 | 基准 | +10% | +20% |

| 体积 | 基准 | +5% | -30% |

| 可用性 | 99.4% | 99.5% | 99.9% |

最终方案:

项目选择级联H桥拓扑直挂方案,12个功率单元串联,输出49电平。

实施效果:

系统实测效率99.1%,可用性99.92%,满足设计要求。省去变压器节约成本约200万元,效率提升带来年收益增加约80万元。

五、选型决策矩阵与工程实践

5.1 三维决策矩阵

基于功率等级、电压等级、效率目标三约束条件,建立拓扑选型决策矩阵:

| 功率等级 | 电压等级 | 效率目标 | 推荐拓扑 | 成本估算 | 决策依据 |

|---|---|---|---|---|---|

| < 500kW | < 690V | < 97% | 两电平SiC | 0.10元/W | 成本最优,结构简洁 |

| < 500kW | < 690V | ≥ 97% | 三电平SiC | 0.15元/W | 效率优先 |

| 500kW-2MW | 690V-1500V | ≥ 98% | NPC三电平 | 0.15元/W | 效率成本平衡 |

| > 2MW | 10kV | ≥ 99% | 级联6单元 | 0.20元/W | 高压直挂 |

| > 5MW | 35kV | ≥ 99% | 级联12单元 | 0.23元/W | 高压直挂+冗余 |

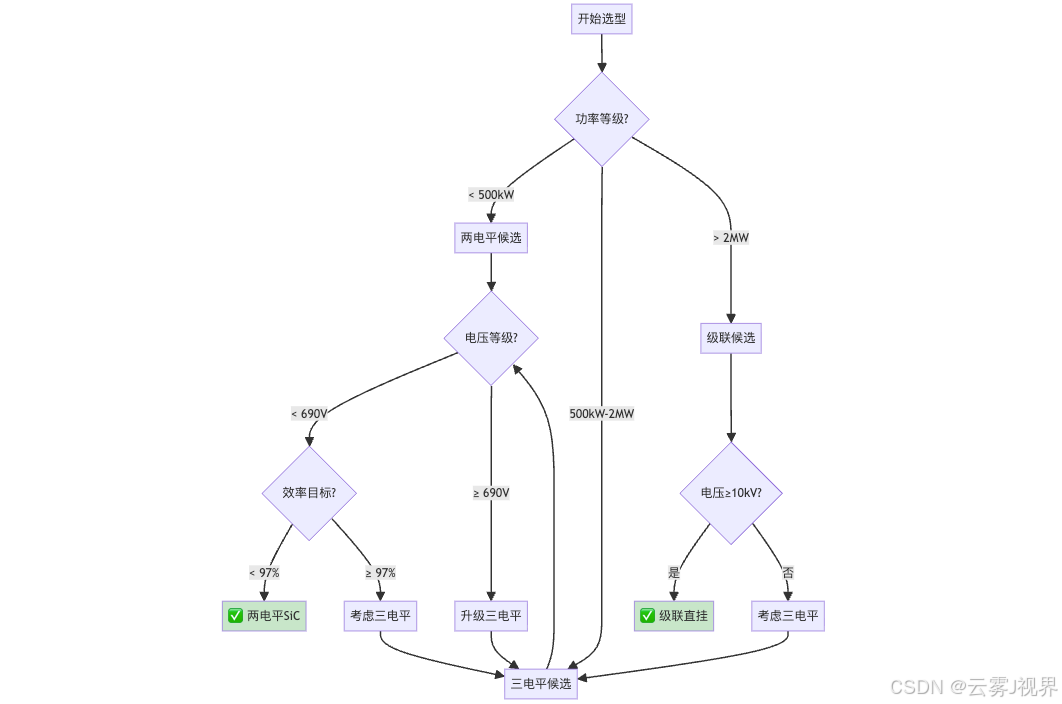

5.2 选型决策流程

拓扑选型应遵循"功率优先、电压验证、效率锁定"的决策流程:

六、结论与行动建议

6.1 核心结论

-

拓扑选型是PCS设计的第一决策,选型失误导致的效率损失和成本超支在项目后期难以纠正。500kW和2MW是两个技术经济性分界点,跨过分界点后拓扑方案的性价比发生质变。

-

效率敏感度极高:1%效率差异在100MW电站全生命周期内意味着420万元收益差。三电平拓扑在500kW-2MW区间实现效率与成本的最优平衡,级联拓扑在2MW以上实现效率突破99%。

-

技术经济性验证必要性:拓扑选型不应仅凭经验或成本判断,需结合具体项目参数进行技术经济性验证。

6.2 SMART行动计划

Day 1-2:需求参数确认

- 确认功率等级、电压等级、效率目标三个核心参数

- 收集项目边界条件(成本预算、体积约束、可靠性要求)

- 输出:需求参数确认表

Day 3-4:候选拓扑筛选

- 对照决策矩阵筛选候选拓扑

- 运行MATLAB效率计算模型验证

- 输出:候选拓扑效率预测报告

Day 5-7:技术经济性验证

- 器件选型与成本核算

- 滤波器设计与体积评估

- 可靠性与维护成本评估

- 输出:拓扑选型决策报告