当我们谈论电磁时,我们在谈论什么?这不是一个离我们生活很远的话题,也不仅仅与硬件研发有关,我们的生活中随处可见电磁干扰现象。比如,KTV中两个话筒距离太近,可能会出现啸叫;再比如,一些地磁混乱的地区,会出现GPS定位异常甚至失灵。这些现象,其实都是电磁干扰在现实生活中的直观体现。

很多人虽然不清楚其背后的物理机制,但大多都有一个共识:电磁干扰会显著影响电子设备的使用体验,甚至直接导致功能失效,这也是为什么现在产品上市前都必须通过相关电磁兼容标准的认证。

当电磁干扰问题发生在电子产品中时,最终几乎都会指向同一个关键载体 - PCB。

在工程实践中,EMC(Electromagnetic Compatibility,电磁兼容)常常被误认为"成品测试阶段才需面对的问题",但实际上,EMC的根源往往在PCB设计与制造阶段就已经被埋下了。

PCB是电子设备信号、电源、电流回路和参考平面的物理载体,也是电磁能量最容易产生、耦合和辐射的地方。在PCB上,电磁噪音不是随机出现的,而是高度集中在几个少数功能模块中,更准确地说 - "电流快速变化"或"参考不稳定"的地方,就一定会产生电磁噪音。

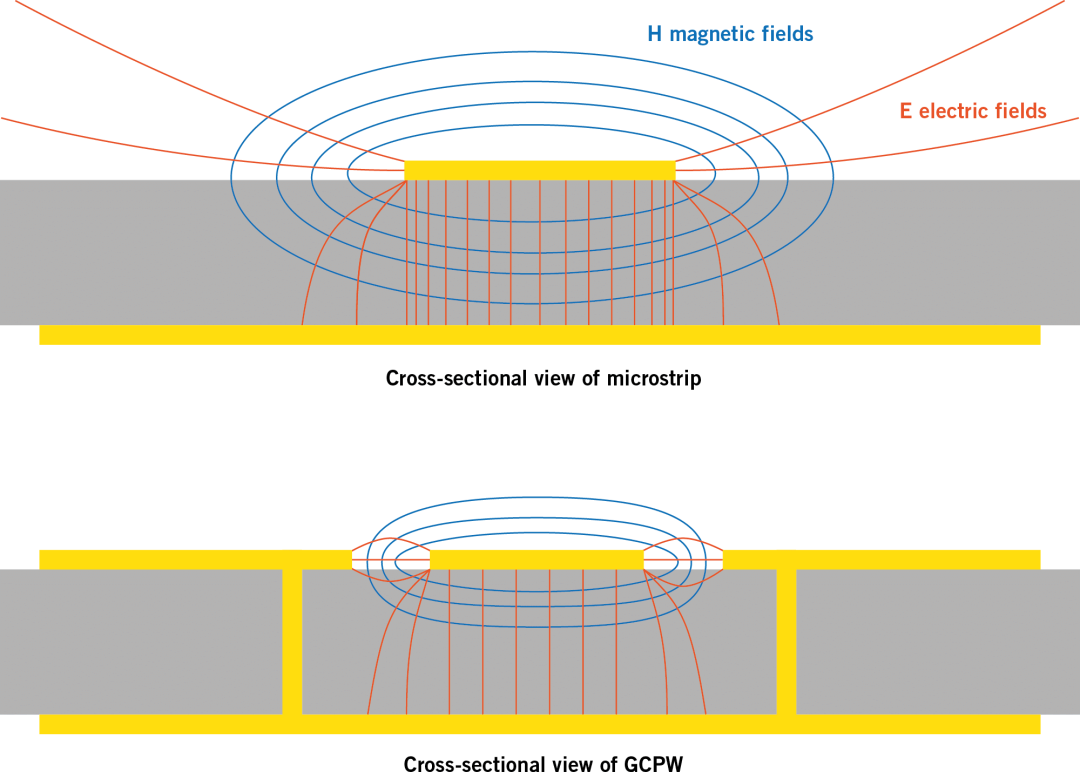

下图展示了当电源接入PCB时传输线产生的电场与磁场,这些场域与周边信号相互作用,影响信号质量。

The Electronical and magnetic fields produced by transmission lines when power is applied to the PCBs.(Source: NCAB)

The Electronical and magnetic fields produced by transmission lines when power is applied to the PCBs.(Source: NCAB)

PCB电磁兼容性设计

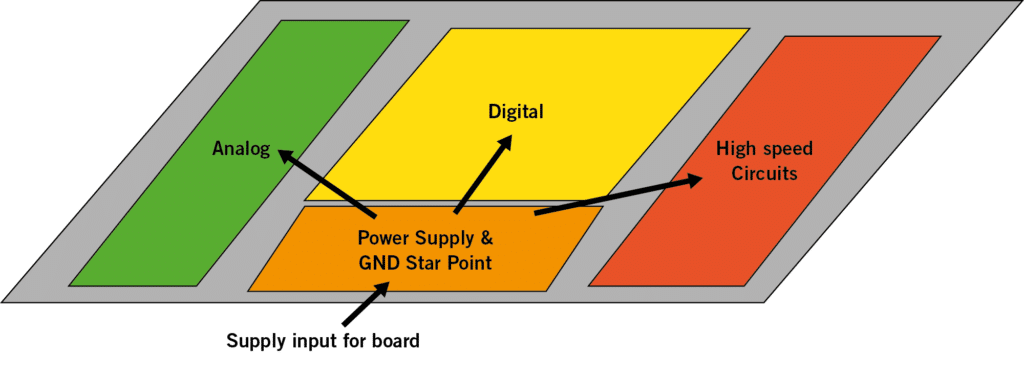

功能分区

我们可以将PCB划分为不同的功能区域,如数字电路区、模拟电路区、电源区等,每个区域,都有自己的噪声源、电流回路、参考需求及可接受的干扰水平,如果不能做好各个功能区间的屏蔽,导致这些模块在PCB上边界不清、回流交叉,那么噪声就可能以辐射或传导的形式发散出去。

在进行PCB元器件布局时,需要注意:

-

高频/噪声电路(如开关电源、时钟电路)应远离敏感电路(如模拟信号、传感器),来减少干扰耦合。

-

高速芯片(如MCU、存储器)应远离板边和借口,避免外部干扰。

-

关键元件布局:晶振/时钟源应靠近负载芯片,缩短走线路径,减少辐射和干扰。电源芯片应靠近用电单元,减少电源路径上的压降和噪声。敏感元件(如小信号放大器、高精度ADC)应远离噪声源,如大功率器件、开关电源等。

此外,还要控制电流回路面积,特别是高频信号的回路面积,在低频时,信号导线是导线,但在高频时,信号导线就成了天线,对外产生辐射。

电源与接地设计

1. 电源层设计

电源层应完整、连续、避免分割,来减少电源噪声的传播。在电源入口处添加滤波电容,滤除电源线上的高频噪声。

2. 接地层设计

使用完整、连续的地平面,为信号提供低阻抗回路,避免分割地平面,特别是高频电路的地平面,来防止地弹噪声。

各子系统的地,应通过过孔连接到主地平面。

3. 去耦电容设计

在每个电源引脚就近放置0.1uF高频陶瓷电容和10uF储能电容,来滤除电源线上的高频噪声和提供瞬态电流。电容的接地端应该直接打孔至地平面,减少引线电感,提高滤波效果。

电源层、接地层与去耦电容,共同构成了一个用于处理高速瞬态电流的闭合系统,这个系统的稳定性,往往比信号线本身更直接决定了整块板在电磁环境中的表现。

信号线设计

走线规则

-

避免90°垂直走线,用45°弧线或圆弧走线,减少阻抗突变导致的反射。

-

高速线(如USB、HDMI)应按设计要求匹配阻抗特性(如50Ω/100Ω差分),来减少信号失真和辐射。

-

差分信号线应保持等长、等距,减少共模噪声。

-

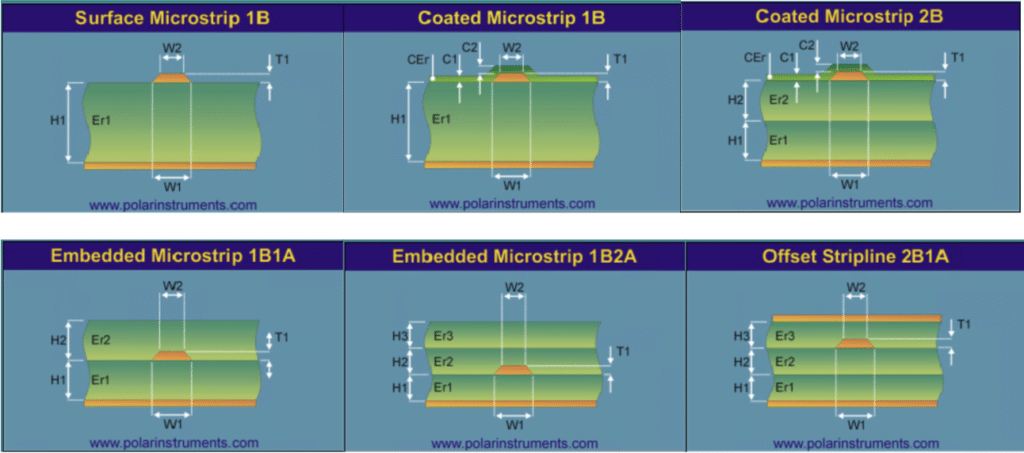

微带线将信号层置于PCB外层,而带状线则是将信号置于两个接地层之间。带状线结构通常能提供更好的阻抗控制,因其走线更具封闭性,减少了受外部干扰因素影响的可能性。

串扰控制

-

高速信号线(如时钟、数据总线)应使用3W原则(线间距≥3倍线宽),避免串扰。

-

为减少耦合干扰,建议避免平行走线,特别是长距离平行走线。

-

建议在关键信号线两侧添加保护地线,屏蔽外界干扰

其它优化措施

叠层结构

合理设计PCB的层叠结构,如将电源层和地层相邻排列,来减少电源噪声对信号层的干扰。在高速信号层下方安排完整的地平面,提供稳定的参考和屏蔽作用。一个好的叠层设计有助于阻抗控制、成品良率、成本、交期等因素的平衡。

过孔设计

减少过孔数量,特别是关键信号线上的过孔数量,来减少信号失真和辐射。优化过孔布局,避免过孔形成大的电流环路或天线效应。当高速信号必须换层走线时,需要在信号过孔旁添加Stitching Via,为信号换层提供连续、最短的回流路径。

我们曾在实践中遇到这样一个案例 - 高速信号阻抗线与过孔间距过近。设计师为了在外层焊盘间腾出布线空间,主动移除了参考层上的非功能焊盘(Anti-pad),最后结果就是阻抗不如预期。

从电磁角度来看,Anti-pad增大后,信号线下方在这个区域没有参考面,导致阻抗突变,引起信号反射,同时增大的Anti-pad破坏了信号原定的回流路径,导致信号走线与回流路径形成的环路面积增大,向外辐射电磁能量,影响产品的EMC性能。

材料选择

选择具有低介电常数和低损耗的PCB材料,来减少信号传输过程中的衰减和失真。考虑使用阻抗控制材料或特殊涂层材料,来提高PCB的EMC性能。

总结

PCB的EMC性能,是产品核心功能、成本、可靠性及合规性要求的权衡。比如高速通信设备需要优先控制辐射发射,而医疗设备需重点提升抗干扰度。PCB EMC是个庞大的课题,涉及信号完整性、电源完整性、热管理、机械结构等多方面因素,PCB设计工程师需在多个维度间找到最佳平衡点。

NCAB建议在设计初期就与PCB供应商密切合作,优化设计,尤其是复杂的设计方案,能最大程度降低潜在风险。