会贴一些基础的板子介绍,主要是一些基础引脚 还有 提示介绍 它双核与众不同的特性

目录

[GPIO Muxing引脚复用功能选择:](#GPIO Muxing引脚复用功能选择:)

[GPIO 端口分组(Port A~H):](#GPIO 端口分组(Port A~H):)

[GPIO Input X-Bar (输入交叉开关):](#GPIO Input X-Bar (输入交叉开关):)

[GPIO Output X-BAR(输出交叉开关):](#GPIO Output X-BAR(输出交叉开关):)

[Input X-Bar 与 Output X-Bar:](#Input X-Bar 与 Output X-Bar:)

官方数据手册下载地址:

我这介绍 双核特性等 都是基于官方数据手册:

TMS320F28379D 数据、产品信息和支持 | 德州仪器 TI.com.cn

开发板引脚图下载地址:

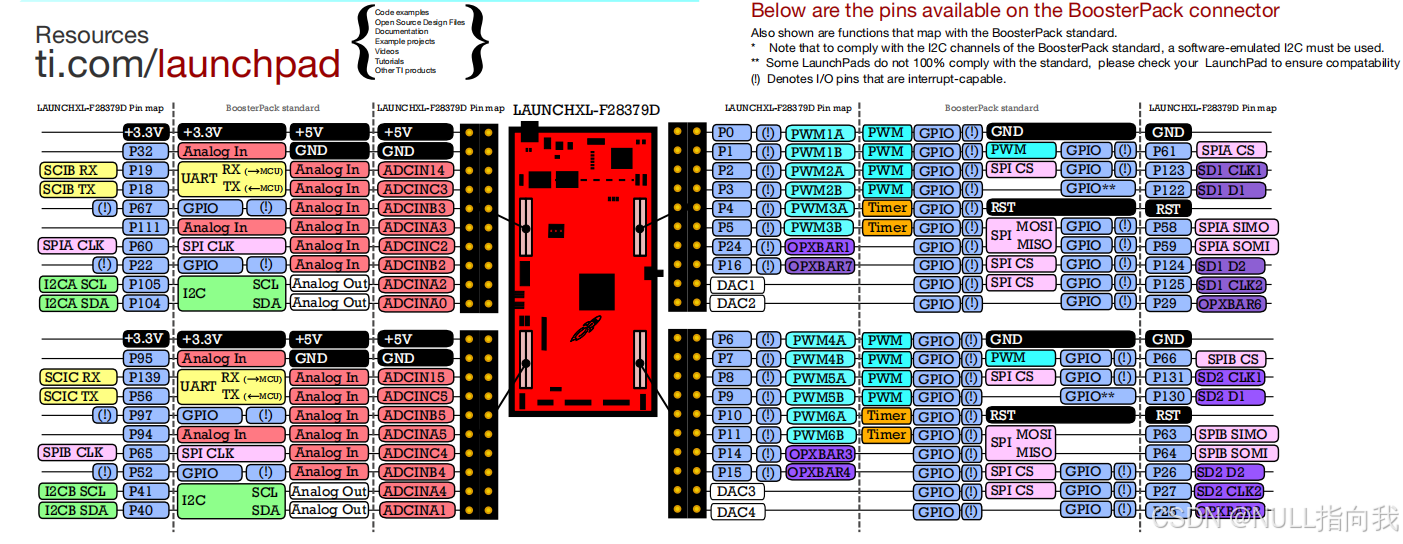

其实引脚定义是要看手册的,但还是直接对着开发板提供的图片比较方便接线,

这图和开发板 背面标的 好像有点手性对称...不管了,一样用的

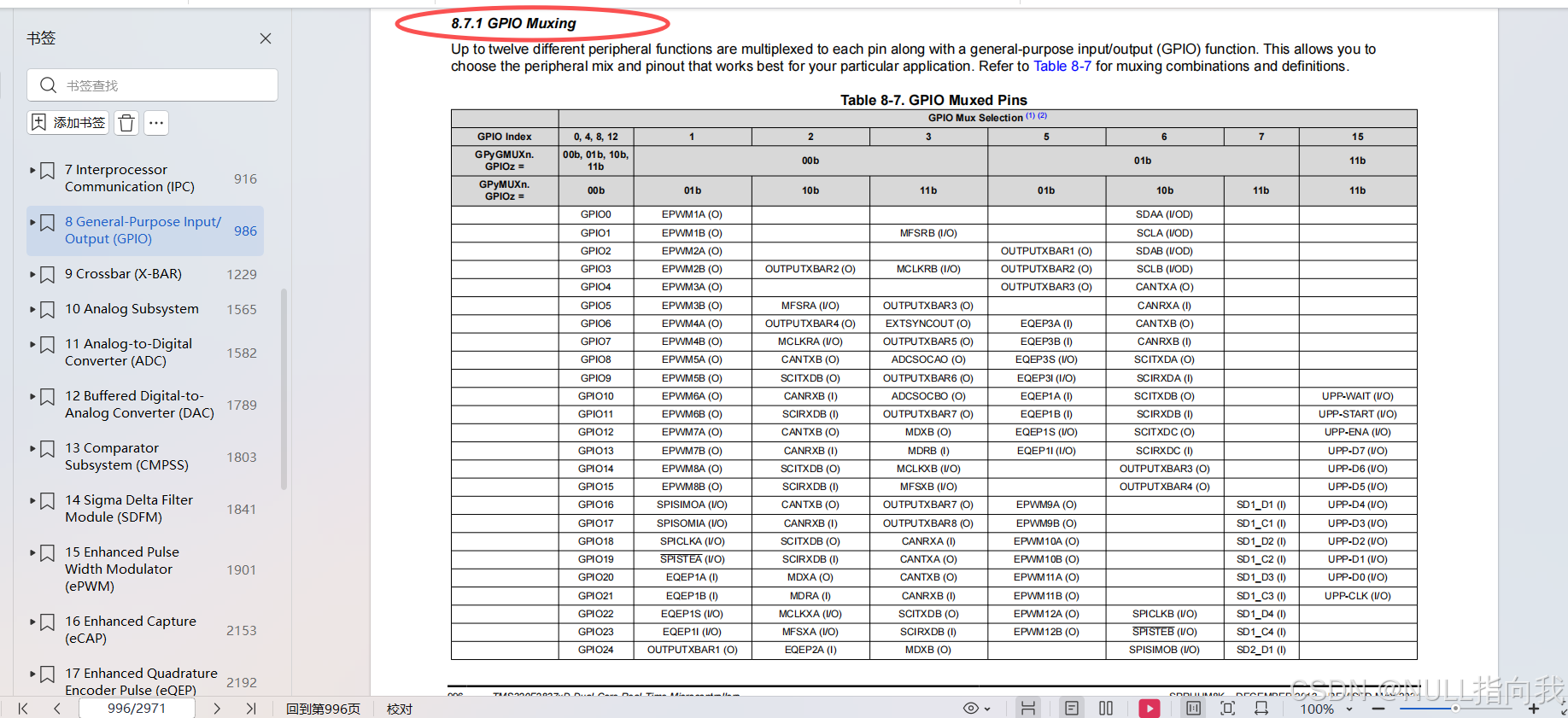

GPIO Muxing引脚复用功能选择:

GPIO 引脚复用功能选择,在手册搜索这个,可以看到最详细的引脚复用功能表格:

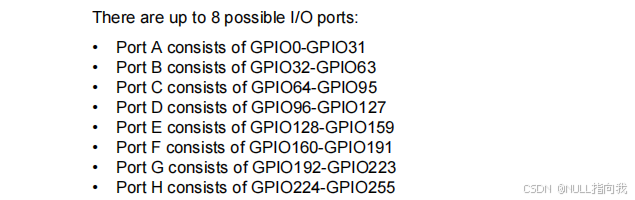

GPIO 端口分组(Port A~H):

不是所有芯片都有全部引脚

比如 F28379D 只有 97 个 GPIO,很多 Port 是不全的

可以基于端口分组,批量配置 GPIO 进入低功耗状态,从而大幅降低芯片功耗

要让 GPIO 不消耗能量,把不用的引脚配置为 "高阻输入 + 上拉 / 下拉",

避免浮空引脚产生漏电流,这是低功耗的核心。

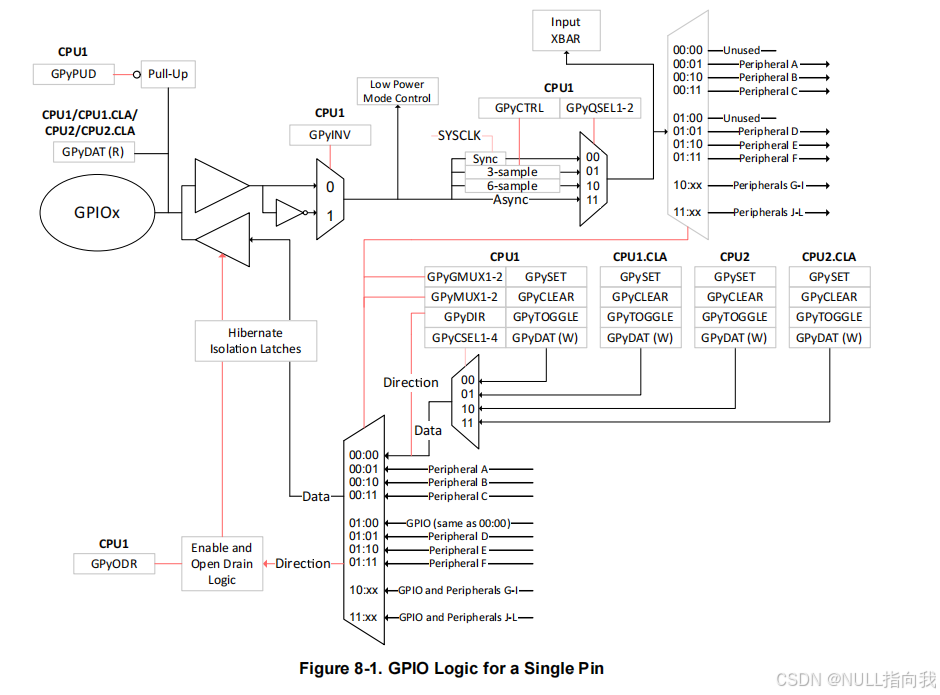

双核引脚管控:

从手册的这张图我们就能初步发现 引脚配置权全在 CPU1 手里

引脚硬件上是共用的一套,但输出只能一个核控制,输入两个核能同时读;

CPU1 先初始化所有 GPIO ,后 CPU1 释放 CPU2 复位 ,CPU2 去用已经分配好的引脚

CPU2 能读、能输出、能控制,只是不能改配置

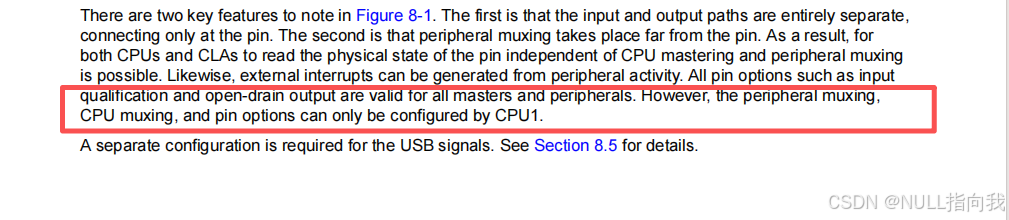

官方手册第987页直接就说明了这个双核引脚管控方式:无论引脚由哪个 CPU 主控、被分配给哪个外设,两个 CPU 和两个 CLA 都能独立读取引脚的物理电平

外设复用、CPU 主控分配、引脚选项(上拉 / 下拉 / 方向 / 滤波等),只能由 CPU1 配置。

CPU2 能读:不管谁控制输出,CPU2 都能读引脚真实状态

CPU2 能输出:只要 CPU1 把主控权分给 CPU2,CPU2 就能正常驱动输出

CPU2 不能改配置:所有复用、主控、引脚属性,全归 CPU1 管,CPU2 只能用

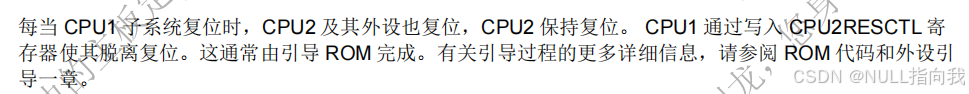

双核复位逻辑:

为了保证 GPIO / 外设配置的权威性

上电默认CPU1 先跑,CPU2 处于 被强制复位态 (Held in Reset)

CPU1 必须手动把 CPU2 从复位态拉出来,CPU2 才能开始运行

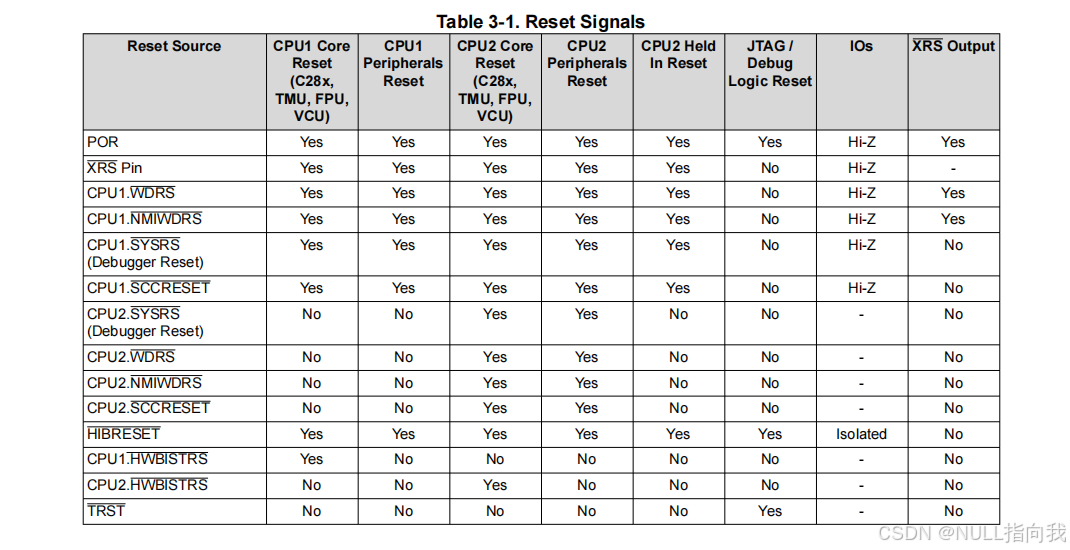

芯片级复位

(

XRS外部引脚、POR上电、CPU1.WDRSCPU1 看门狗、CPU1.NMIWDRSNMI 看门狗)全芯片彻底复位,CPU1、CPU2、所有外设、寄存器全部清零,相当于芯片完全重启。

CPU1 系统级复位(

CPU1.SYSRS、CPU1.SCCRESET)CPU1 子系统复位 → CPU2 子系统被强制复位并锁死在复位态,不会自动启动。

CPU2 要想重新运行,必须由 CPU1 手动操作

CPU2RESCTL寄存器,释放 CPU2 的复位,这个动作通常由引导 ROM 自动完成,也可以由用户代码手动控制。

CPU2 子系统复位(CPU2 自己的复位)只复位 CPU2 及其专属外设,CPU1 正常运行、不受任何干扰。

复位信号表

CPU1绝对主控,CPU2受控从核

手册83页

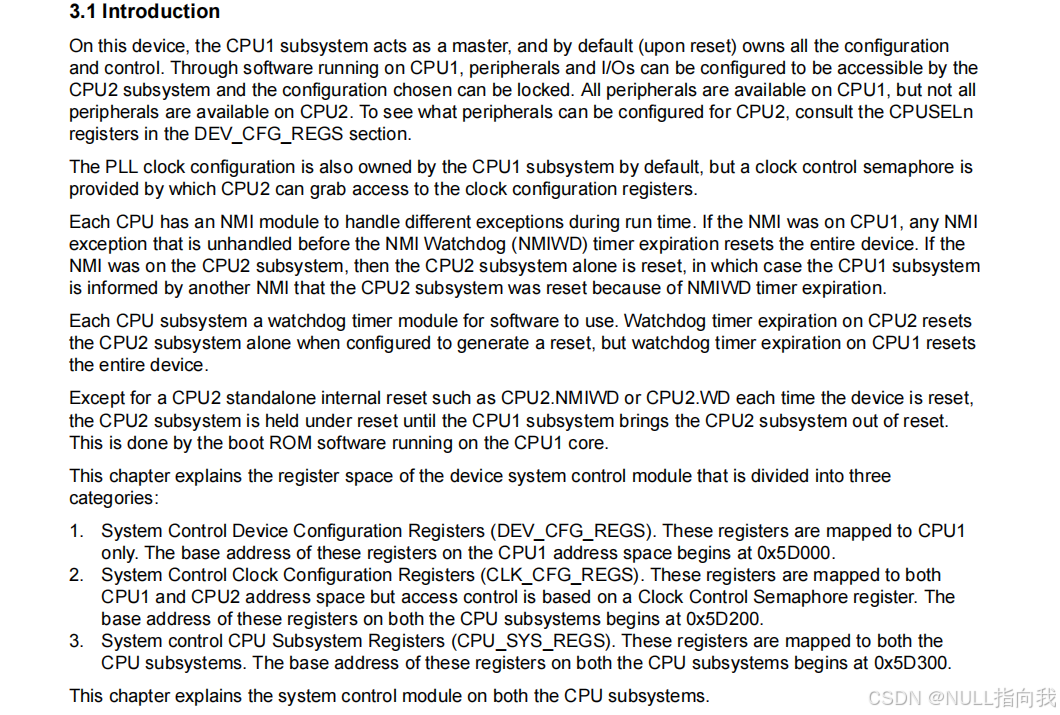

设备中断体系结构:

GPIO 引脚中断(XINT):

一个 GPIO 引脚的中断,永远只能触发其中一个 CPU,无法同时触发两个。

由 CPU1 通过 Input X-Bar 路由,只能分配给其中一个核。

路由配置(比如把 GPIO0→CPU1.XINT1,GPIO1→CPU2.XINT1):只能由 CPU1 完成,CPU2 无权修改 X-Bar 寄存器。

路由完成后,CPU1 和 CPU2 各自在自己的 PIE 里使能对应 XINT 中断:

分配给 CPU1 的 XINT:由 CPU1 在自己的 PIE 中使能,触发 CPU1 中断

分配给 CPU2 的 XINT:由 CPU2 在自己的 PIE 中使能,触发 CPU2 中断

ADC/SPI 等共享外设中断:

硬件会同时广播给两个核的 PIE

ADC/SPI/SCI/CAN 等共享外设中断:硬件广播,双使能即可同时触发

只要两个核各自在自己的 PIE 里使能该中断,就能同时收到;

归属权由 CPU1 配置,但不影响中断广播。

归属权不影响中断:哪怕 ADC 归 CPU1 主控,只要 CPU2 在自己的 PIE 里开了 ADC 中断,CPU2 也能收到 ADC 转换完成中断。

只要 CPU1 在自己的 PIE 中使能了该中断 → 就能收到

只要 CPU2 在自己的 PIE 中使能了该中断 → 就能收到

两个都使能 → 同一个中断事件,同时触发两个核的中断服务函数

定时器中断:双核完全独立:

CPU1 的 TIMER0/1/2 只触发 CPU1,CPU2 的 TIMER1/2 只触发 CPU2,无法共享。

CPU1:拥有 TIMER0、TIMER1、TIMER2 三个定时器,中断只触发 CPU1

CPU2:仅拥有 TIMER1、TIMER2 两个定时器,中断只触发 CPU2

TIMER0 是 CPU1 专属,CPU2 没有这个定时器,无法共享

两个核各自配置自己的定时器中断,完全独立,互不影响。

中断使能权限:

路由 / 归属配置(X-Bar、CPUSEL):仅 CPU1 可配置

PIE 中断使能、IER/IFR、全局中断:两个核各自配置自己的

其他中断源

IPC 中断(核间通信)

专门用于双核通信,CPU1 可以给 CPU2 发中断,CPU2 也可以给 CPU1 发中断,是软件触发的双向中断,用于双核同步。

NMI / 唤醒中断

双核各自独立,CPU1 的 NMI 复位全片,CPU2 的 NMI 仅复位自己;唤醒中断各自独立,由 CPU1 配置唤醒源。

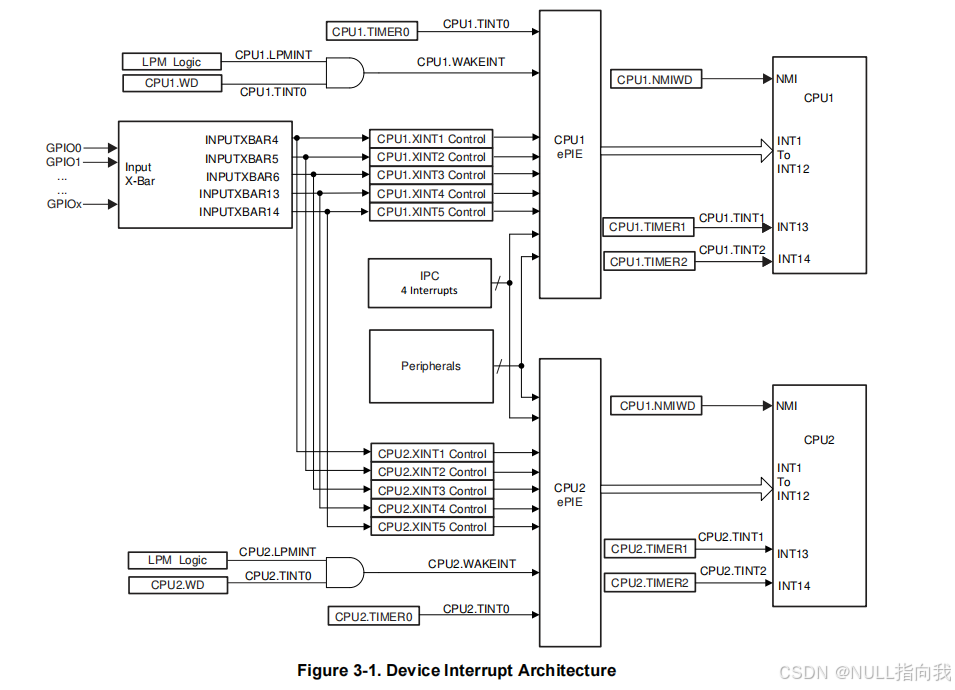

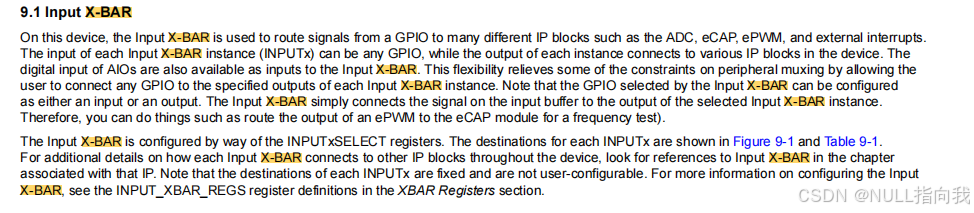

GPIOInput X-Bar (输入交叉开关):

GPIO 引脚中断(XINT):只能分配给一个核,不能同时触发

On this device, the Input X-BAR is used to route signals from a GPIO to many different IP blocks such as the ADC, eCAP, ePWM, and external interrupts.**翻译:**Input X-BAR 的作用,就是把 GPIO 的信号,路由到 ADC、eCAP、ePWM、外部中断等不同的 IP 模块。

它是一个硬件级的信号开关,不是改 GPIO 复用,而是把 GPIO 内部信号转发给其他模块。

The Input X-BAR is configured by way of the INPUTxSELECT registers.翻译: X-BAR 通过

INPUTxSELECT寄存器配置,且只能由 CPU1 配置GPIO 中断的路由、X-BAR 的配置,只有 CPU1 能写这些寄存器,CPU2 无权修改。

Note that the GPIO selected by the Input X-BAR can be configured as either an input or an output.**翻译:**被 X-BAR 选中的 GPIO,既可以配置为输入,也可以配置为输出。

哪怕 GPIO 是输出模式,X-BAR 也能把它的输出信号路由给其他模块(比如把 ePWM 的输出 GPIO,路由给 eCAP 做频率测试)。

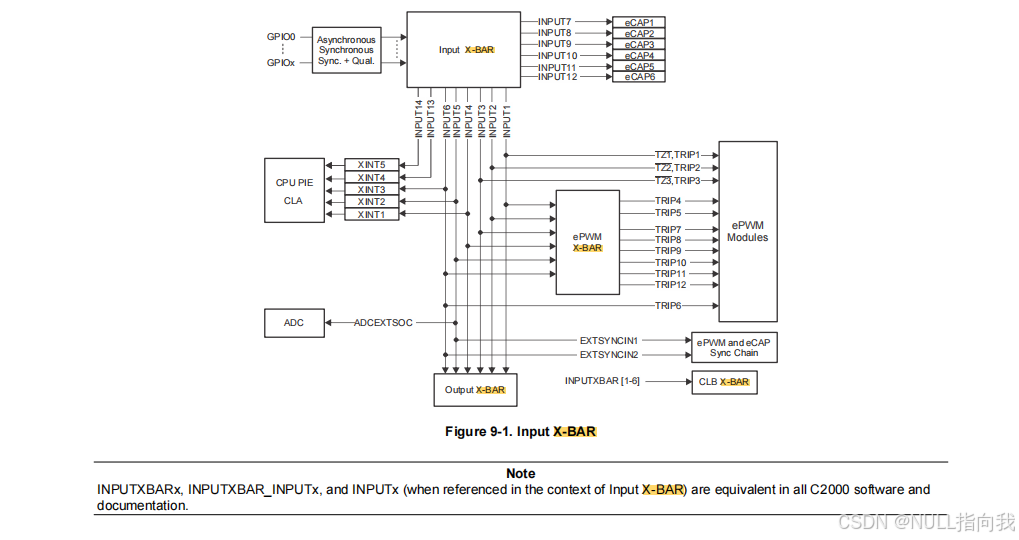

图中清晰显示:

所有 GPIO 先进入 Input X-BAR,再从 X-BAR 输出到

XINT1~XINT5,最终连接到 CPU 的 PIE 中断系统。GPIO 中断必须经过 X-BAR 路由,一个 GPIO 只能被配置到一个 XINT,

因此只能分配给 CPU1 或 CPU2 其中一个,不能同时触发两个核。

X-BAR 的多模块路由能力:

图中显示 X-BAR 的输出同时连接了:

eCAP 模块(INPUT7~12)

ePWM 的 Trip / 同步信号

ADC 的 ADCEXTSOC(外部启动转换信号)

Output X-BAR、CLB X-BAR 等其他模块

一个 GPIO 的信号,可以同时路由给多个不同的 IP 模块(比如一个 GPIO 同时给 ADC 做启动信号、给 ePWM 做 Trip 保护、给 CPU 做外部中断),极大提升了灵活性。

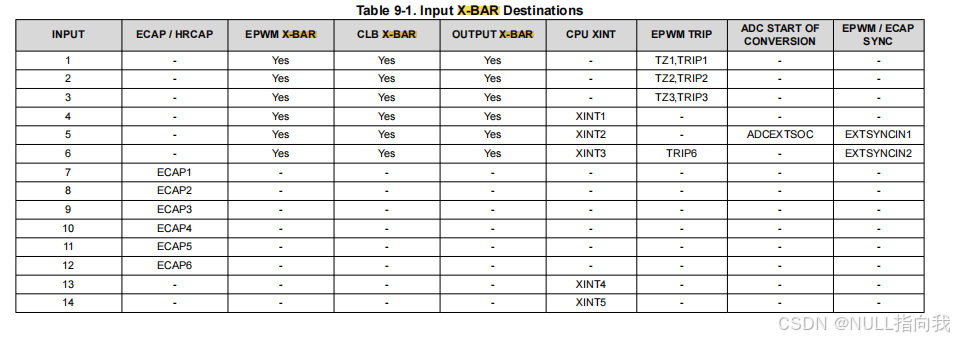

Input X-BAR 的路由权限清单

INPUT CPU XINT 说明 4 XINT1 只能连 XINT1 5 XINT2 只能连 XINT2 6 XINT3 只能连 XINT3 13 XINT4 只能连 XINT4 14 XINT5 只能连 XINT5

GPIO Output X-BAR(输出交叉开关):

专门解决把芯片内部信号输出到 GPIO 引脚的灵活路由问题

Input X-BAR 是「GPIO → 内部模块 」的路由器,而 Output X-BAR 是「内部模块 → GPIO」的路由器

它能把芯片内部任意多个信号(比如 ePWM、eCAP、ADC、CPU 控制信号等),通过逻辑或(OR)组合后,输出到指定的 GPIO 引脚。

彻底打破了传统 GPIO 复用「一个引脚只能对应一个内部信号」的限制,实现了多信号合并输出、灵活路由。

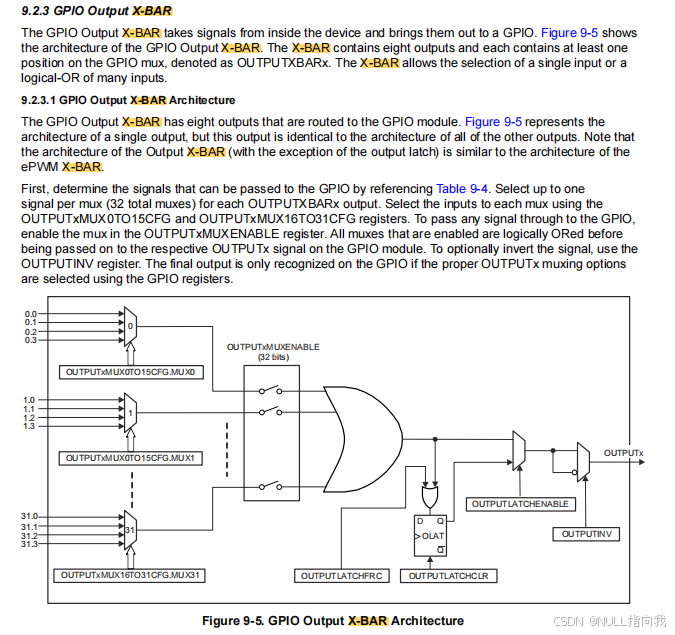

32 路输入源:左侧有 32 组输入(0.0~0.3、1.0~1.3 ... 31.0~31.3),对应芯片内部所有可路由的信号(ePWM、eCAP、ADC、CPU 等)。

输入选择(MUX) :每个 Output X-BAR 通道,通过

OUTPUTxMUX0TO15CFG/OUTPUTxMUX16TO31CFG寄存器,选择要路由的输入信号。使能开关(MUXENABLE) :通过

OUTPUTxMUXENABLE寄存器,开启 / 关闭对应输入信号的路由,只有使能的信号会参与逻辑或。逻辑或(OR)门 :所有使能的输入信号,经过逻辑或运算后,合并为一路信号。

可选反转(OUTPUTINV) :通过

OUTPUTINV寄存器,可选择反转输出信号(高变低、低变高)。可选锁存(LATCH) :通过

OUTPUTLATCHENABLE寄存器,可开启输出锁存,让信号保持状态,适合脉冲信号输出。最终输出到 GPIO :处理后的信号,通过 GPIO 复用(

OUTPUTXBARx模式)输出到物理引脚。8 路独立输出 :Output X-BAR 有 8 个独立的输出通道(

OUTPUTXBAR0 ~ OUTPUTXBAR7),每个通道都可以单独配置。多输入逻辑或(OR) :每个通道可以选择单个输入信号 ,也可以选择多个输入信号做逻辑或后输出,实现「多个事件触发同一个 GPIO 输出」。

GPIO 复用绑定 :每个 Output X-BAR 通道,对应 GPIO 复用表中的一个固定位置(比如

OUTPUTXBAR0对应某个 GPIO 的复用模式 7),配置后该 GPIO 就会输出 X-BAR 的信号。

实战应用场景:

- 多故障信号合并输出

把 CPU1 故障、CPU2 故障、ePWM 过流、ADC 过压等多个内部故障信号,通过 Output X-BAR 做逻辑或,合并输出到一个 GPIO 引脚,接一个故障告警灯:

只要任意一个故障发生,GPIO 就会输出高电平,点亮告警灯,不用分别控制每个信号。

- 灵活的 PWM 输出路由

把多个 ePWM 模块的同步信号,通过 Output X-BAR 路由到同一个 GPIO,实现多轴电机的同步触发,不用受传统 GPIO 复用的限制。

- 脉冲信号锁存输出

把 eCAP 捕获的脉冲信号,通过 Output X-BAR 的锁存功能,保持输出状态,方便外部电路检测,避免脉冲过窄导致漏检。

- 双核状态指示

把 CPU1 和 CPU2 的运行状态信号,通过逻辑或合并输出到一个 GPIO,用一个 LED 指示双核是否正常运行。

Input X-Bar 与 Output X-Bar:

| 特性 | Input X-BAR | Output X-BAR |

|---|---|---|

| 核心方向 | GPIO → 内部模块 | 内部模块 → GPIO |

| 核心功能 | 把 GPIO 信号路由给 ADC、ePWM、中断等 | 把内部信号路由给 GPIO 引脚输出 |

| 输入 / 输出 | 输入:任意 GPIO;输出:固定到对应模块 | 输入:任意内部信号;输出:8 路独立通道 |

| 逻辑运算 | 无(纯路由) | 支持多输入逻辑或(OR)合并 |

| 典型场景 | GPIO 触发 ADC 采样、外部中断、ePWM 保护 | 多事件合并输出到一个 LED、故障告警、ePWM 同步输出 |