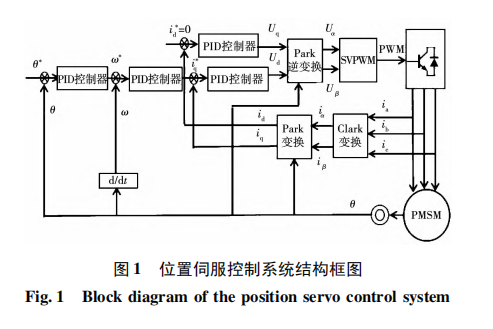

永磁 同步 电机 ( permanent magnet synchronous motor,PMSM) 省去了转子励磁装置,无需励磁电流,具有结构简单、体积小等优点,尤其在空间有限且需要多轴伺服精确控制的应用场合具有广泛的前景,如工业机器人、数控机床、导弹舵机和相控阵列天线等[1-2]。

目前,多轴伺服控制系统主要包括数字信号处理器 (digital signal processor,DSP) 的软件方案以及现场可编程逻辑门阵列 (field programmable gate array,FPGA) 的硬件方案。DSP 的软件方案,价格低廉、灵活性强,可以实现多种控制算法,得到广泛的应用。近些年,TI 等公司推出了电机专用的 DSP 控制芯片,计算性能十分强大,还添加了很多电机实际控制需要的外设单元,已成为市场主流伺服控制产品。但软件串行中断的执行方式限制了处理器的性能,不适合运算复杂且实时性要求非常高的应用场景,单个 DSP 难以满足高精度多轴伺服控制的需求。而采用多个 DSP 互联的设计方式,就会使得设计难度增加,成本上升,系统集成度降低,同时各轴之间易出现不同步的问题。因此 DSP 的软件方案难以实现多轴伺服电机的高性能控制[3-6]。

FPGA 具有高速、低功耗、并行处理和模块化等特点,允许单一芯片控制多台电机,部分学者对其开展了深入探索[7-10]。国内李铁才等人[11-12]对基于 FPGA 的高性能多轴伺服系统进行了研究,实现了四轴电机伺服控制 ASIC 芯片等一系列的成果。国外的 Hsin-Hung Chou、B-M L 等人[13-14]在单片 FPGA 上集成了多轴控制算法,设计了多轴伺服电机控制平台。伺服控制系统的位置环、速度环、电流环闭环算法以及相应的信号采集与处理算法由纯硬件逻辑实现,实现单 FPGA 芯片的全数字化多轴控制。这种技术方案由于位置环、速度环需求灵活,纯硬件的设计方式很难满足通用性的要求,而且很难根据外部参数和实时状态配置参数,存在软件与硬件功能规划不合理的问题。

随着多处理器片上系统 (multi-processor system on chip,MPSoC) 的发展,Ben Othman 等学者[15-18]将其引入电机驱动等实时控制领域,提出了基于FPGA 的 MPSoC 架构,用于实现高实时性、高精度运行的系统。本文提出一种基于 MPSoC 的多轴伺服驱动方案,该方案采用 FPGA 作为处理器。在单轴电机控制上,电流环控制 IP 核实现电流环算法,速度环算法在软核中实现,通过软硬件协作的方式完成单轴电机的精确控制。结合 MPSoC 构建了多轴伺服控制系统,集成了核间通讯和上电自启动等功能。最后搭建了两路实验系统,并通过实验验证了方案的有效性。

2 系统整体方案

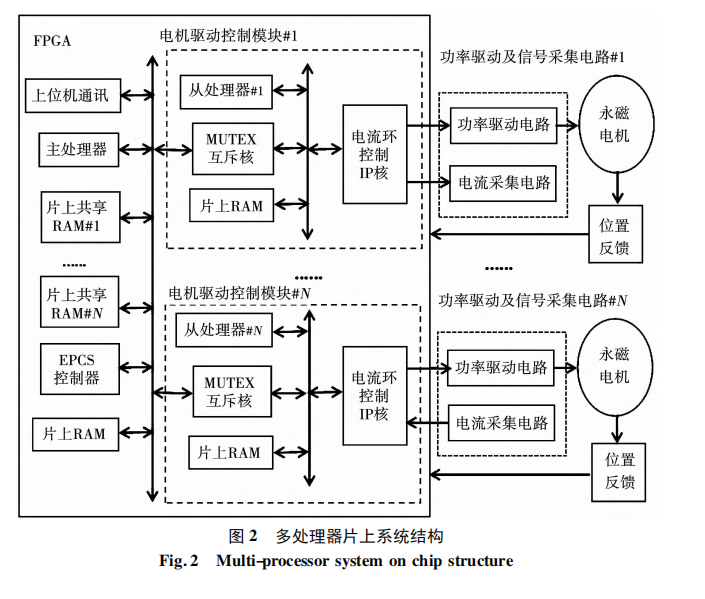

图2 给出了这种基于 MPSoC 的多轴伺服控制方案的整体结构框图。

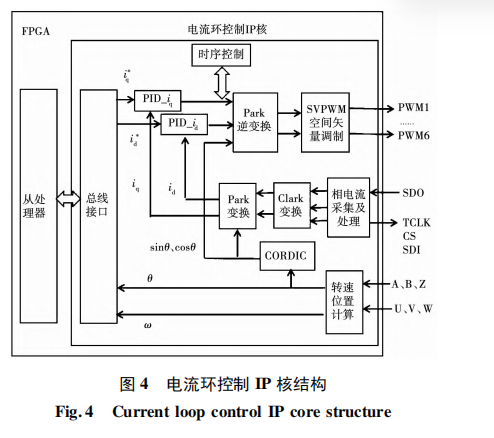

为实现单轴电机的高精度控制,结合软硬件协同设计方法,设计了单轴电机控制模块。具有高实时性和算法相对单一等特点的电流矢量控制算法以及信号采集、处理算法由纯硬件逻辑设计的电流环控制 IP 核实现,具有强灵活性的速度环算法在嵌入式软核中以软件方式实现。单轴电机控制模块内部包含以下模块: 电流环控制 IP 核模块,用于实现对

应轴的电流环矢量控制算法以及信号采集和处理算法,将计算的位置、速度信息反馈给从处理器用于闭环控制。从处理器,首先读取片上共享内存上的数据完成与主处理器之间的核间通讯; 其次接收同一模块内部的电流环控制 IP 核反馈的速度信息,执行对应轴的速度环算法,根据计算结果输出电流指令;此外还包括闭环参数配置、多种对外接口等软件功能。片上 RAM,用于存储从处理器的程序,提供从处理器程序的运行空间。

为实现多轴电机独立、同步驱动,对单轴电机控制模块进行多路拓展,设计了多处理器片上系统结构,添加了多个模块完善片上功能。在主处理器与从处理器间采用 MUTEX 核与片上共享内存结合的通讯方式实现多处理器间的数据通讯。添加 MUTEX 核,用于实现多个处理器对片上共享存储资源的互斥访问; 添加片上共享 RAM,用于实现多个处理器通讯时的数据交互以及存储。

多处理器片上系统还添加了以下模块: 上位机通讯模块,连接上位机,接受上位机的指令并将其传输给主处理器,同时将控制器实时状态发送给上位机; 主处理器,处理上位机的命令,发送任务,控制从处理器及其他模块完成任务; EPCS 控制器对接外部的串行存贮器,通过搬运串行存贮器中的代码实现 FPGA 的数据配置; 片上 RAM 模块存储主处理器的程序,提供主处理器程序的运行空间。 多处理器片上系统在单片 FPGA 芯片内部设计完成,FPGA 通过外部接口与驱动板连接,获取位置、速度和电流相关信号用于处理计算,输出 PWM波信号用于电机控制。每一路的电机控制模块对应一路功率驱动及信号采集电路,彼此无干扰、并行驱动。功率驱动及信号采集电路集成在一块驱动板上,由功率驱动电路、电流信号采集电路、位置速度反馈电路三部分组成。

多处理器片上系统在单片 FPGA 芯片内部设计完成,FPGA 通过外部接口与驱动板连接,获取位置、速度和电流相关信号用于处理计算,输出 PWM波信号用于电机控制。每一路的电机控制模块对应一路功率驱动及信号采集电路,彼此无干扰、并行驱动。功率驱动及信号采集电路集成在一块驱动板上,由功率驱动电路、电流信号采集电路、位置速度反馈电路三部分组成。

4 两路实验系统的构建

为验证基于 MPSoC 的多轴伺服控制技术方案的可行性与有效性,对已构建的单轴电机控制模块进行两路拓展,在单片 FPGA 芯片内搭建两路实验系统,用于后续实验验证。

所使用的开发平台采用 Cyclone V 5CEBA4F23C7N作为主控芯片,包含 49K 逻辑资源,Altera 开发软件(Quartus II) 提供了设计环境与库,NIOS II 软核、 Avalon 总线以及可定制 IP 核,用于设计多处理器片上系统的体系结构。两路实验系统利用了 FPGA 内部 32% 的逻辑资源,5 476 个自适应逻辑单元。 FPGA 时钟频率为 50 MHz,电流环控制频率为100 kHz,速度环控制频率为 25 kHz。

不仅可实现多轴电机驱动控制、上位机通讯等功能,也提高了控制平台的集成度。系统性的对软硬件功能进行规划,实现各功能模块在硬件和软件两方面的合理分配,系统灵活性得到提高,也有利于硬件、软件的设计,减少设计周期。