顶层集成Verilog代码

核心动作:建立内部"连接线(Wire)",把各个模块无缝串联起来。

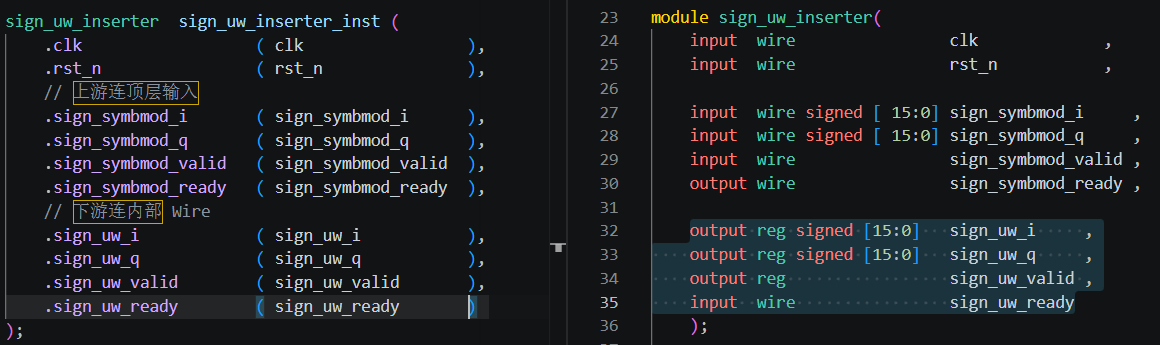

以信号段UW插入举例:

Verilog 模块例化(调用模块) = 把写好的功能模块,像 "电子元器件" 一样,插到你的电路里用。

Verilog模块例化的标准格式:

模块名(已经定义好的模块名) 例化名<调用该模块时取的名字> (

.端口名1 ( 连线1 ),

.端口名2 ( 连线2 ),

// ...所有端口

);

模块例化注意:

1,在底层模块内部(sign_uw_inserter):它是一块"芯片"。在子模块内部,因为我通过always@()或者always @(posedge clk)这个状态机大逻辑来给他赋值,所以它必须拥有"记忆"与"驱动能力"。

这里的output reg就像是芯片内部极其强力的输出驱动寄存器(引脚的推挽电路)。它负责把状态机算出来的 1 或 0 稳稳地锁住,并推向引脚。

在always和initial块里的变量要用reg型变量

2,顶层集成模块(SC-FDE_tx_comb_part):它时"PCB主板",顶层模块不负责产生数据,它扮演的角色是一块绿色的PCB印刷电路板。

在顶层定义的wire signed[15:0] sign_uw_i,在物理世界中,就是印在PCB板上的一根纯粹的铜导线。

这根铜导线的一头焊在sign_uw_inserter芯片的输出引脚(reg)上,另一头焊在下游合路器tx_data_merge的输入引脚上。

3,Verilog语法铁律速记

在 Verilog 语法中,模块例化的连线规则非常死板,但只要记住下面这两句话就永远不会错:

铁律 1(对内) :模块的 output 在自己内部怎么写都可以 。如果被**always 驱动就写****re**g,如果被 assign 驱动就写 wire。

铁律 2(对外) :当你在外层例化这个模块时,去接它 output 的那根线,必须、绝对、只能是 wire 类型!(因为你不能用一个存放状态的寄存器去硬接另一个寄存器输出的管脚,那会导致电路短路或多驱动冲突)。