1. 晶振概述

晶振(晶体振荡器)是一种利用石英晶体的压电效应产生稳定频率信号的电子元件。

1.1. 工作原理

-

压电效应:石英晶体具有压电特性,当在晶体两端施加交变电压时,晶体因逆压电效应产生机械振动;反之,机械振动又通过正压电效应产生交变电场。这种"电-机-电"的可逆转换特性,使晶体能在特定频率下形成稳定振荡。

-

谐振频率:晶体的固有谐振频率由其物理尺寸、切割角度和材料特性决定。当外加电压频率接近晶体固有频率时,晶体发生共振,机械振动幅度最大,电路通过反馈机制维持稳定振荡,输出精确的频率信号。

1.2. 晶振分类

- 按功能与补偿方式:

- 无源晶振(晶体谐振器):需搭配外部电路才能起振,成本低、体积小,适用于对精度要求不高的场景。

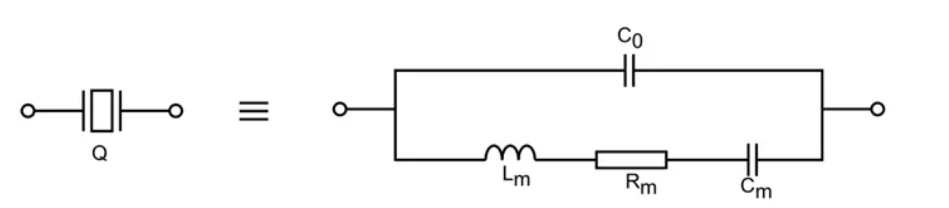

石英晶体的等效模型

- 有源晶振(晶体振荡器):内置振荡电路,直接输出稳定时钟信号,精度高、抗干扰能力强,广泛应用于通信、工业控制等领域。

- 温补晶振(TCXO):内置温度补偿电路,通过热敏电阻感知环境温度并调整频率,适用于宽温范围的高精度应用,如GPS、通信设备。

- 恒温晶振(OCXO):将晶体置于恒温槽内,保持温度恒定,频率稳定性极高,常用于航空航天、高端测量仪器等对精度要求极高的场景。压控晶振(VCXO):输出频率可通过外部电压微调,适用于锁相环、频率合成器等需要频率调整的系统。

- 按封装形式:

- 插件晶振:引脚直插式,多用于旧款设备或需频繁更换的场合。

- 贴片晶振:表面贴装,体积小、重量轻、耐震性强,广泛应用于现代电子设备。

- 按频率模式:

- 基频晶振:晶体直接振动产生基频,频率范围通常在1MHz~50MHz。

- 泛音晶振:振动在基频奇数倍频点(如3次、5次泛音),可实现更高频率(100MHz以上),需电路支持泛音模式。

1.3. 晶振作用

- 提供时钟信号:为电子设备(如计算机、手机、通信设备)提供稳定的时钟信号,同步和控制各部件的操作,确保数据准确传输和处理。

- 实现信号稳定性:频率稳定性高,受环境温度、电压波动影响小,可避免信号波动和时序偏移,保证系统可靠运行。

- 支持精确定时:在航空航天、科学仪器等领域,为精密测量、导航定位等提供高精度时间基准,满足对时间精度要求极高的应用需求。

2. 晶振起振原理

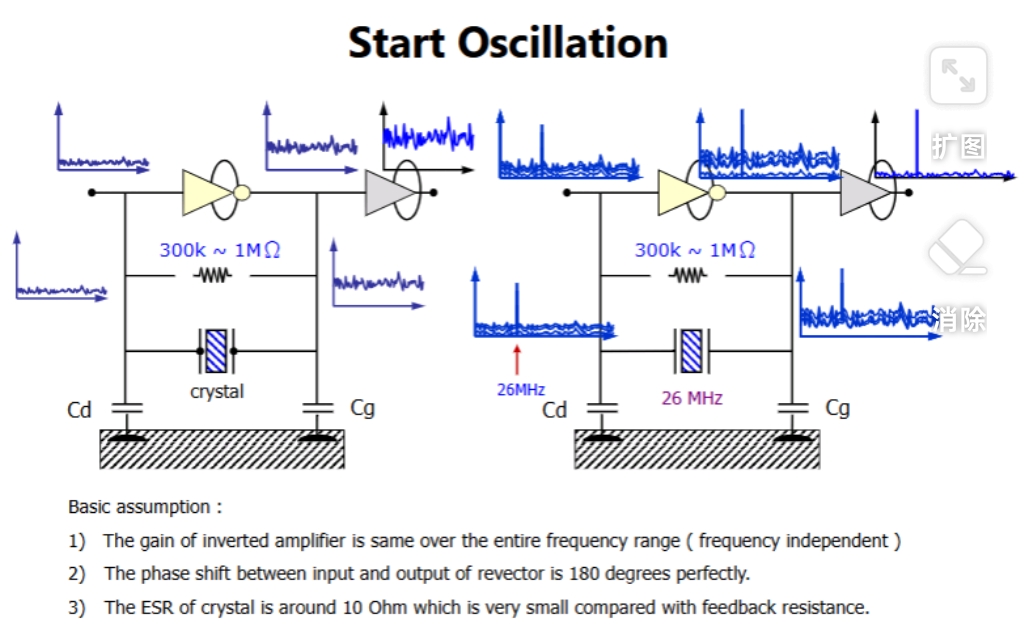

- 电路结构

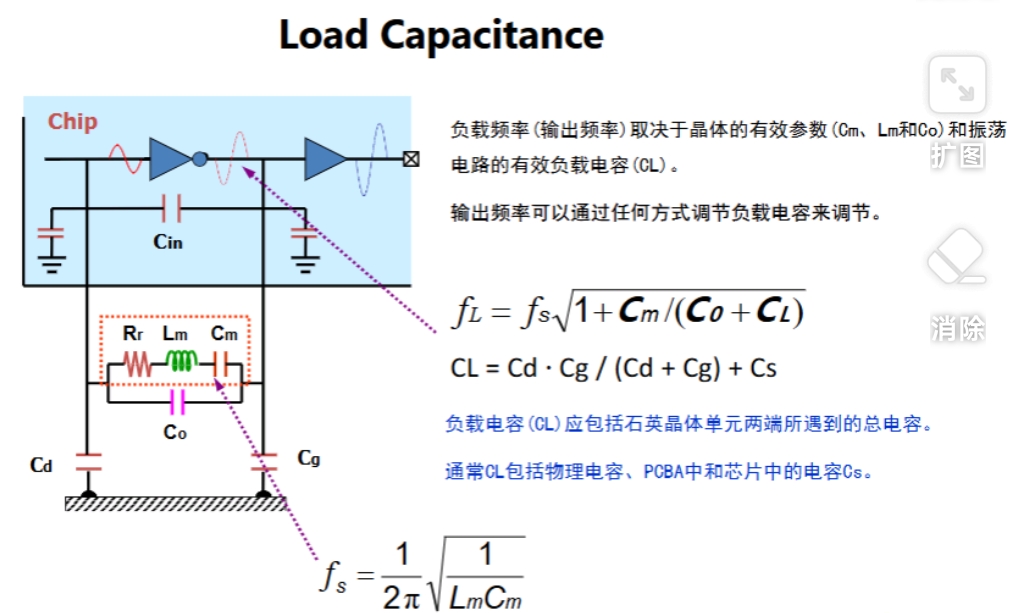

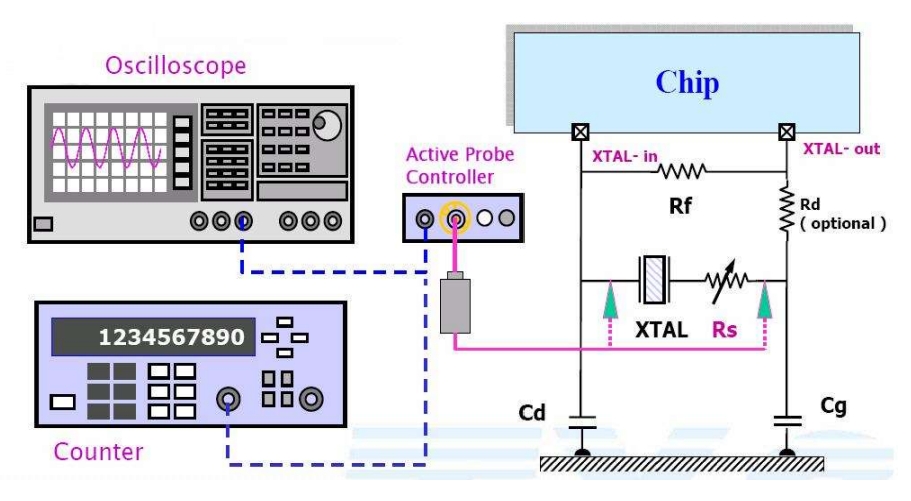

这是典型的Pierce晶振振荡电路,包含以下关键部分:

- 反相放大器(门电路/运放):提供180°相移与增益

- 反馈电阻(300k~1MΩ):使反相器工作在线性区,同时提供直流偏置

- 晶振(crystal):在串联谐振频率附近呈感性,提供额外180°相移

- 负载电容 Cd / Cg:决定晶振的负载电容CL,匹配谐振频率

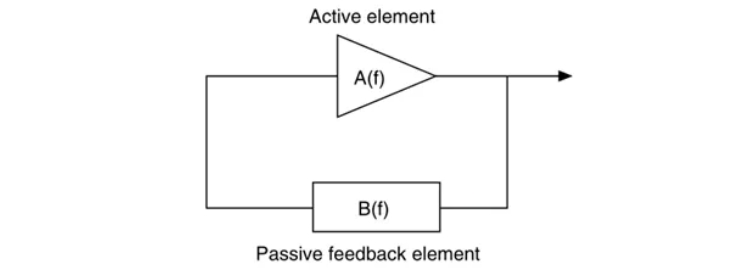

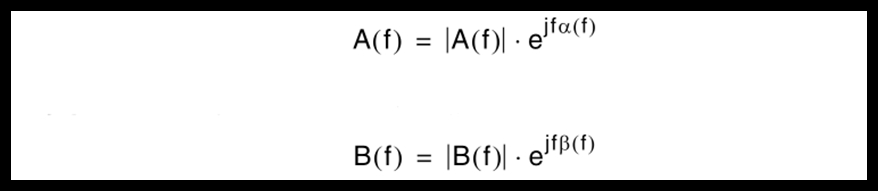

A(f)是放大器部分,给这个闭环系统提供能量以保持其振荡。

B(f)是反馈网络,它决定了振荡器的频率。

为了起振,以下的巴克毫森准则必须得到满足。即闭环增益应大于1,并且总相移为360°。

振荡需要初始能量才能启动。通电瞬变和噪声可以提供所需的能量。然而,能量需要足够高才能在所需的频率下触发振荡。为了让振荡器稳定工作,实际A(f)*B(f)>>1,这意味着开环增益应该远远高于1。振荡达到稳定状态所需的时间取决于开环增益。

3. 晶振负载电容

负载电容CL是指连接到晶振上的终端电容。CL值取决于外部电容器Cd和Cg,杂散电容Cs。

振荡频率精度,主要取决于振荡电路的实际负载电容与晶振制造商给出的CL值是否相同。振荡频率是否稳定则主要取决于负载电容值是否保持稳定不变。

- 串联谐振频率 fs:晶振在不考虑外部负载时的固有谐振频率,公式:

- 负载谐振频率 fL:晶振接入电路后,受外部负载电容 CL 影响的实际工作频率,公式:

从公式可以看出:负载电容 CL 越大,实际工作频率 fL 越低;反之,CL 越小,fL 越高。

4. 晶振测试方案

测试项目主要包含晶振频偏测试,晶振负阻测试,晶振驱动功率测试,晶振启动时间测试;

另外,还有晶振稳定起振的电气参数测试:信号单调性,信号占空比,信号脉宽等等,电气测试相对测试方法简单就不一一介绍。

4.1. 晶振频偏测试

- 晶振频偏定义:

- 频偏 = 实际输出频率 − 标称频率

- 行业用 ppm(百万分之一) 表示:

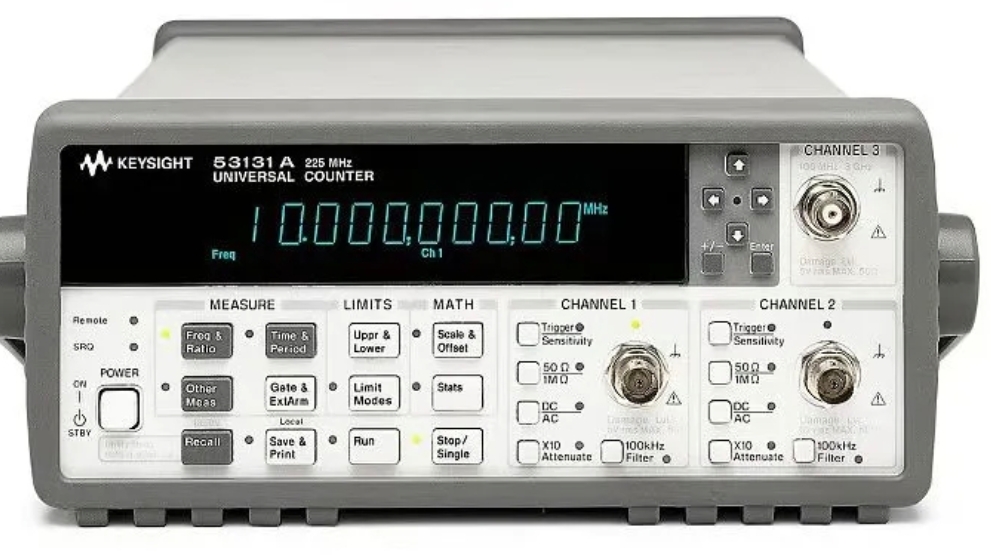

- 测试设备:

- 高负载或低频晶振,负载电容>8pF:频率计+低负载探头

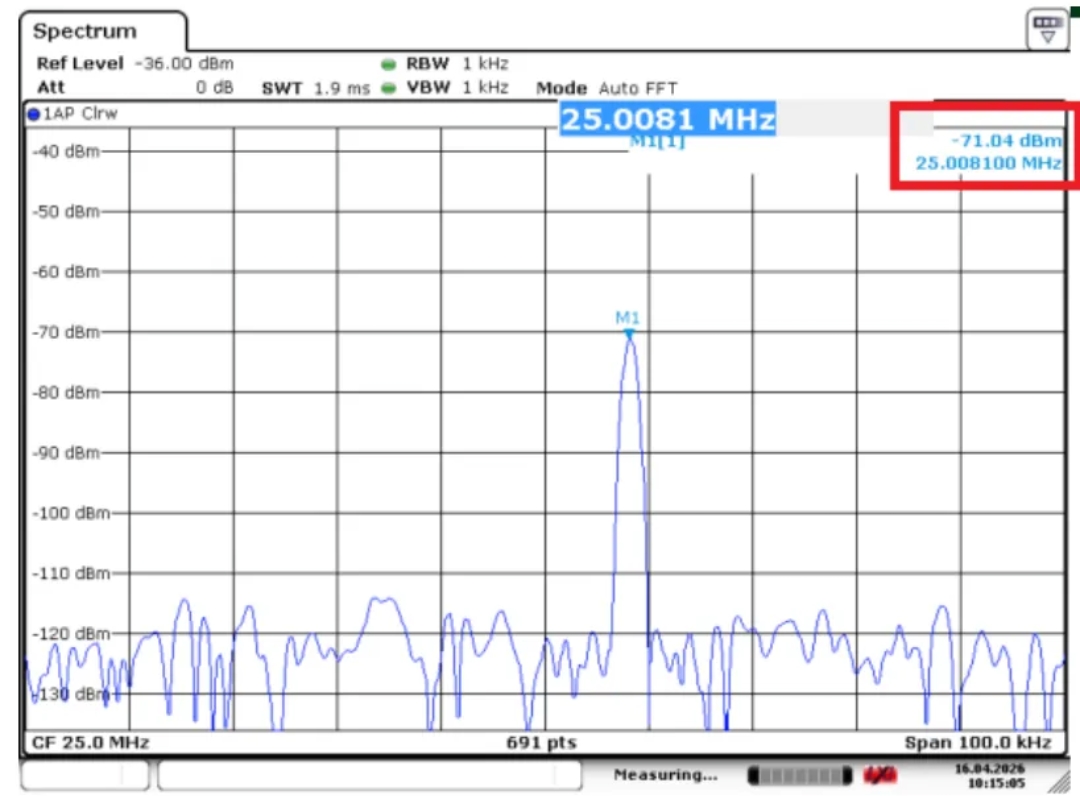

- 低负载晶振≤8pF:频谱分析仪

- 测试方法:

- 频率计:将低负载探头连接晶振输出端口(XIN_OUT),读取频率计上显示的频率,即为晶振起振稳定的工作频率;

- 频谱分析仪:用静场探头扫描晶振起振稳定时的频率,用Marker点Peak Search功能找到最大点,即为晶振起振稳定时的频率;

- 常见晶振频偏标准:

|----------|--------------|------|-----------|

| 晶振类型 | 常温频偏 | 温漂范围 | 适用场景 |

| 普通无源晶振 | ±10~±50 ppm | 大 | 消费电子、MCU |

| 高精度无源 | ±5 ppm | 中等 | 蓝牙、WiFi |

| TCXO温补晶振 | ±0.5~±2 ppm | 极小 | 通信、GPS、5G |

| OCXO恒温晶振 | ±0.01 ppm | 几乎无 | 基站、仪器、军工 |

考虑高低温对频偏影响一般在常温下调试频偏至10ppm以内;

- 频偏影响主要因素:

|-------------|--------------------------|---------------|-----------------------|

| 影响因素 | 对频偏的影响 | 典型现象 | 解决办法 |

| 负载电容 CL 不匹配 | CL 偏大 → 频率偏低CL 偏小 → 频率偏高 | 频率不准、跑快/跑慢 | 按晶振规格匹配 CL;调整 Cd/Cg |

| 温度变化 | 温度偏离25℃ → 产生温漂 | 高低温频偏超标 | 选AT切/宽温等级;用TCXO |

| 驱动功率过大 | 功率↑ → 频率↓,并加速老化 | 频率持续往下飘、发烫 | 串 Rd 限流,控制在 50--100μW |

| 驱动功率不足 | 激励不够 → 频率不稳、抖动 | 启动慢、易停振、噪声大 | 减小/去掉 Rd;提高负阻 |

| PCB 寄生电容 Cs | 寄生越大 → CL 等效变大 → 频偏 | 每块板频率不一致 | 走线短、包地、少过孔 |

| 晶振老化效应 | 时间越长 → 频率缓慢偏移 | 用久了慢慢不准 | 选低老化品;出厂预老化 |

| 电源噪声/地弹 | 噪声调制 → 频率抖动/漂移 | 相位噪声差、通信丢包 | 电源滤波、单点接地 |

| 机械应力/振动 | 应力改变晶片厚度 → 频偏 | 按压PCB频率变、摔后偏移 | Seam封装;布局避受力区 |

| ESD/浪涌损伤 | 内部晶片/电极受损 → 频偏突变 | 频率突然不准、不起振 | 加强ESD防护、防静电 |

4.2. 晶振负载测试

- 负阻定义:

指振荡电路为了提高晶振起振能力而通过设计途径来增加的反向补偿参数指标。负性阻抗不是晶振的内置参数,但却是振荡线路设计很重要的指标。

- 测试方法:

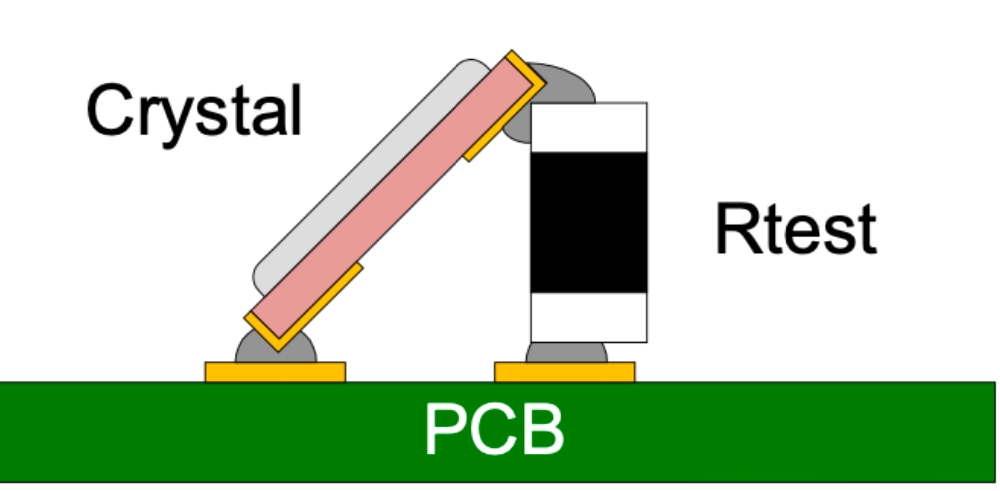

- 将可变电阻Rs与Crystal串联,连接到电路;

- 用示波器测试晶振的XTAL_OUT波形;

- 调整Rs,使得晶振的不起振;

- 使用万用表测试此时不起振的Rs值,即为晶振电路的负阻;

- 测试标准:

- 消费类:Rneg>(3-5)*Crystal ESR

- 车规类:Rneg>10*Crystal ESR

- 负阻不足影响:

- -晶振启动时间变长

- 低温/低电压/高ESR条件下不起振

- 电路抗干扰能力差,易停振

- 频率不稳定、抖动大、批量一致性差

- 提高负阻方法:

- 增大反馈电阻 Rf(典型 300kΩ~1MΩ)

- 优化放大器增益,选用增益更高的驱动方案

- 减小限流电阻 Rd(若有)

- 减少PCB寄生电容,保证负载电容 CL 匹配

- 缩短XTAL走线、远离干扰源、优化接地

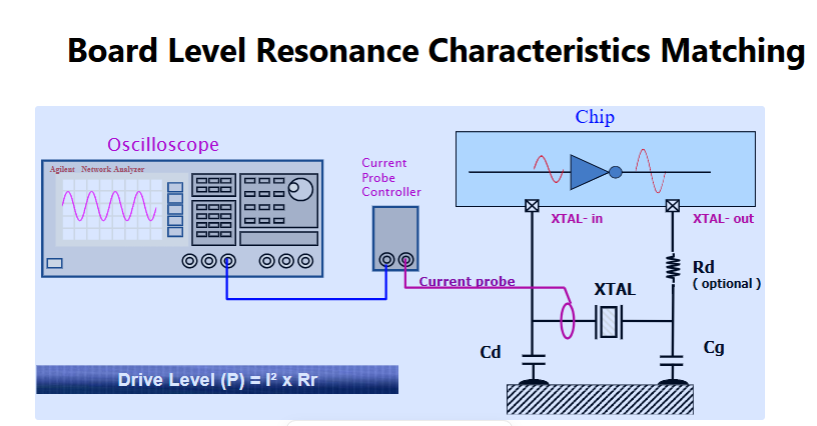

4.3. 晶振驱动功率测试

- 驱动功率定义:

驱动功率通常以微瓦(μW)或毫瓦(mW)为单位,表示晶振在正常工作状态下消耗的电功率。

驱动功率(Drive Level)公式:

P = I^2 *Rr

- I:晶振回路电流(由电流探头测得

- Rr:晶振等效串联电阻(ESR)

- 驱动功率作用:

驱动功率直接影响晶振的振荡稳定性、频率精度和长期可靠性。

- 功率过低可能导致晶振无法起振或振荡不稳定;

- 功率过高则可能使石英晶片过度振动,引发频率漂移、热应力增加甚至晶片损坏。

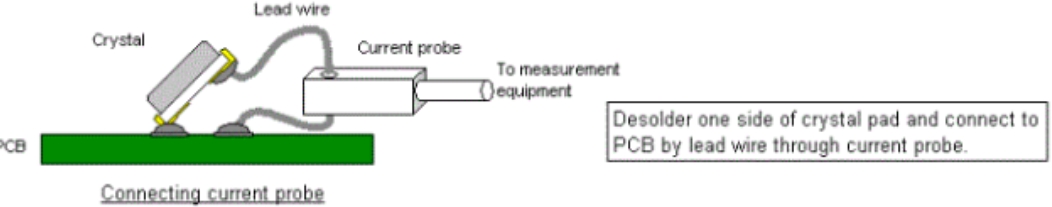

- 驱动功率测试方法:

- 电流探头串入晶振电路中;

- 晶振稳定工作,读取电流晶振稳定起振电流值;

备注:电流探头需带放大器且精度为uA级别,普通电流探头精度无法满足;

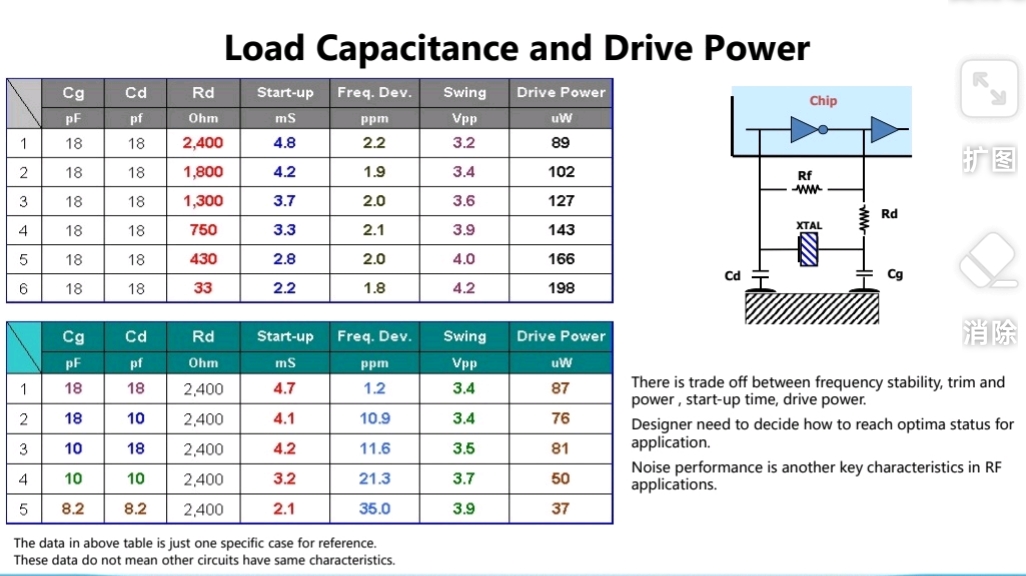

4.驱动功率影响因素:

|-------|----------------------------------------------------|

| 规律 | 工程结论 |

| Rd 越大 | 驱动功率(Drive Power)越低、起振时间(Start‑up)越长、波形幅度(Swing)越小 |

| Rd 越小 | 驱动功率越高、起振越快、波形幅度越大、频偏(Freq. Dev)略降低 |

- 驱动功率异常影响:

- 过驱容易造成晶振频偏;

- 过驱容易引发晶振损坏,造成晶振停振;

- 过驱加速晶振老化;

- 欠驱导致晶振无法起振;

- 驱动功率优化方法

|---------------|---------------------------------------------------------------|

| 异常现象 | 处理措施 |

| 驱动功率超标 | 1. 在晶振输出端串联限流电阻 Rd(100Ω~1kΩ),降低回路电流2. 减小放大器增益,或增大反馈电阻,降低驱动能力 |

| 驱动功率不足 / 起振困难 | 1. 减小限流电阻 Rd,或直接移除2. 优化负载电容 CL,保证相移条件,提高负阻 |

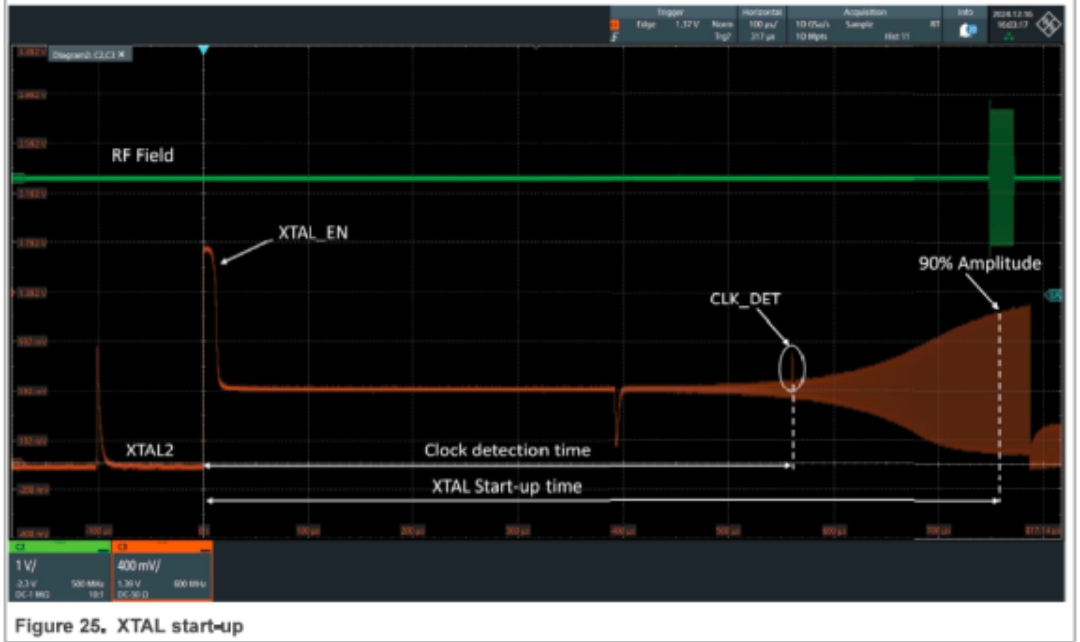

4.4. 晶振启动时间

1.启动时间定义:

晶振起振信号的包络值是稳态峰峰值得90%的时间,称起振时间或Start-up Time,MHz晶振一般在ms级别。

- 测试标准:

- 一般消费电子<5ms

- 汽车电子<3ms

- 高速通信<1ms

- 晶振启动时间影响因素:

|----------|-------------|----------------------|--------------------------|

| 影响因素 | 变化趋势 | 对启动时间的影响 | 工程对策 |

| 限流电阻 Rd | Rd 增大 | 驱动功率降低 → 启动时间变长 | 减小 Rd 或直接移除,提高驱动功率 |

| 负载电容 CL | CL 减小 / 不对称 | 启动时间缩短,但频偏急剧恶化 | 优先匹配晶振标称 CL,保持 Cd/Cg 对称 |

| 电路负阻 | 负阻不足 | 增益不够 → 启动慢、易停振 | 增大反馈电阻 Rf,保证负阻≥3~10×ESR |

| 晶振 ESR | ESR 越大 | 损耗越高 → 启动变慢 | 选用低 ESR 规格晶振 |

| 工作温度 | 低温环境 | ESR 上升、增益下降 → 启动明显变慢 | 选用宽温/车规晶振,优化驱动裕量 |

| 供电电压 | 电压偏低 | 放大器增益下降 → 启动变慢 | 保证芯片供电电压稳定、纹波小 |

| PCB 寄生电容 | 寄生电容大 | CL 等效变大 → 启动变慢、频偏偏移 | 缩短 XTAL 走线、减少过孔、优化接地 |

- 启动时间异常优化:

|---------|--------------|-----------------|

| 异常现象 | 原因 | 解决办法 |

| 启动时间过长 | Rd 过大、驱动功率不足 | 减小 Rd / 移除 Rd |

| 低温启动极慢 | 负阻不足、ESR升高 | 增大反馈电阻 Rf、优化 CL |

| 启动时好时坏 | CL 不匹配、寄生电容大 | 严格匹配 CL、缩短走线 |

| 上电偶尔不起振 | 驱动功率太低、负阻不够 | 提高驱动、保证负阻裕量 |