导读:当单颗芯片突破百亿晶体管、面积逼近光刻极限,"大芯片"时代的设计方法论正在发生深刻变革。Partition技术从最初的后端实现手段,演进为支撑Chiplet异构集成的系统级架构设计哲学。本文将深入解析Partition的四大维度------后端物理、功能逻辑、功耗域与系统架构,揭示其如何成为破解摩尔定律困局的关键钥匙。

一、什么是Partition?------芯片设计的"分而治之"哲学

Partition,中文常译为"划分"或"分区",是超大规模集成电路设计中将复杂系统拆解为可独立处理子模块的核心方法论。其本质是一种"分而治之"(Divide and Conquer)的工程思想,贯穿于芯片设计的全流程。

从层次上看,Partition可分为:

| 层级类型 | 说明 | 典型应用 |

|---|---|---|

| Top-Level | 芯片顶层,负责全局规划与模块拼接 | 全局Floorplan、IO Ring设计 |

| Sub-Top | 中间层级,包含多个Leaf Partition | CPU子系统、GPU子系统 |

| Leaf Partition | 最底层可独立实现的物理单元 | 单个CPU Core、Memory Controller |

层次化设计(Hierarchy Design)中"理论上讲,所有的none-top,互相之间都没有依赖关系(dependency),除非它本身也是一个小top"。这种树状结构使得设计团队能够并行推进,大幅降低项目周期。

二、为什么要做Partition?------四大驱动力

1. 工具与算力瓶颈:从"周收敛"到"日收敛"

当RTL规模突破上亿门、全芯片数据量达数百GB时,传统的Flat(展平式)设计方法已超出EDA工具的内存容量与Runtime极限:

Flat设计:单次综合/布局布线需24小时以上,内存占用>100GB

Partition设计:切成6-10个约20mm²的模块后,单块仅需30-40GB内存,8-10小时即可完成迭代,实现"日收敛"(Daily Turnaround)

"把顶层切成若干物理Partition后,可以把'一个巨问题'拆成'多个小且并行的问题'"。

2. 时序收敛质量(QoR):化长距为短距

超大Flat设计的长互连路径在一次性绕线时难以兼顾。Partition策略将跨模块路径转化为Interface Timing Budget(接口时序预算),让每个子块专注于内部优化,顶层只需关注少量关键跨区路径。

3. 团队协作效率:从串行到并行

不同Partition可分配给CPU、NPU、DDR、PCIe等子团队独立后端实现,只需遵守顶层给定的:

Pin Location(引脚位置)

Timing Budget(时序预算)

Power Domain(电源域)约束

项目周期可从"串行"变"并行",压缩30-40%后端时间。

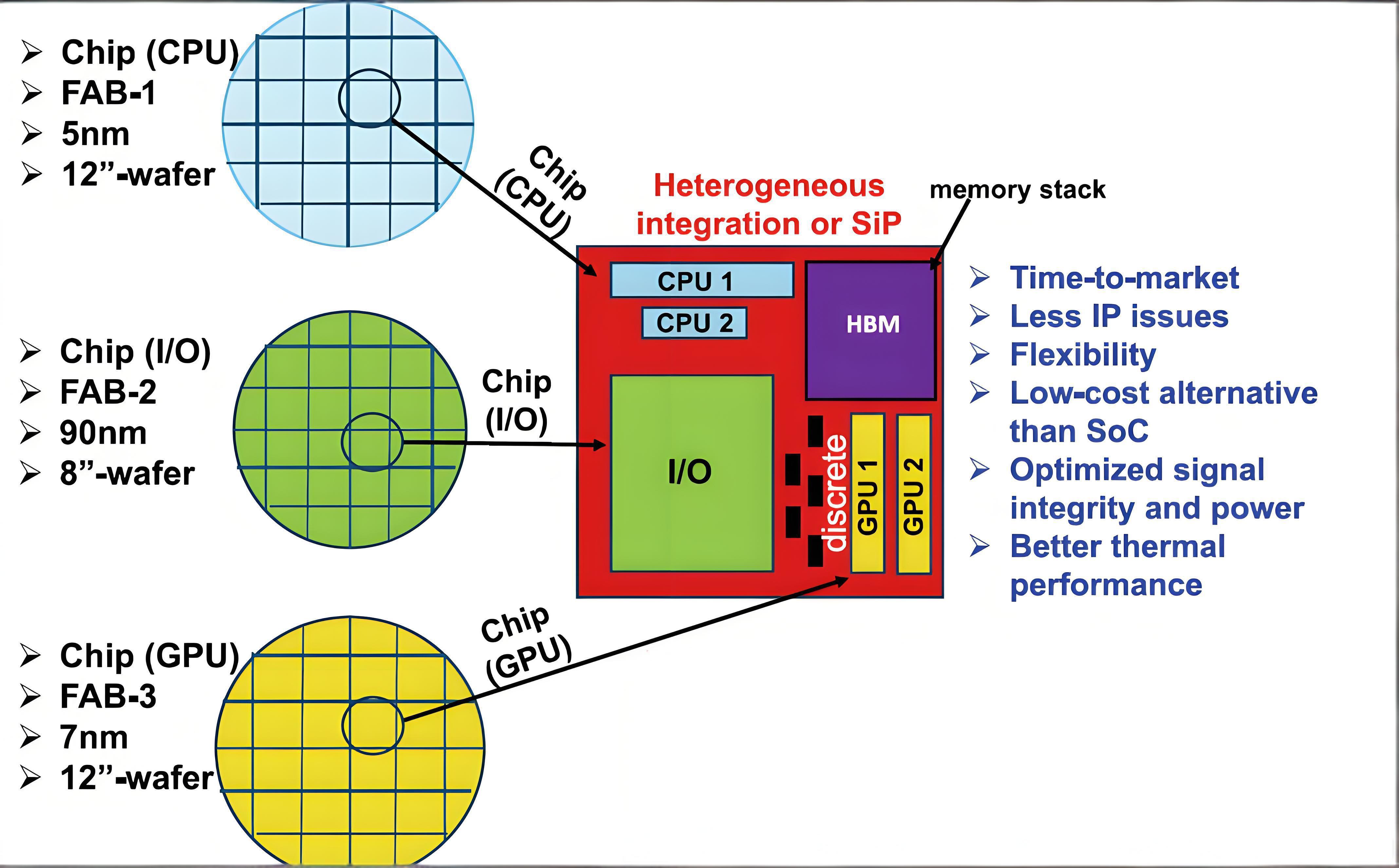

4. Chiplet架构基础:超越Reticle极限

当单Die面积超过光刻机Reticle极限(~858mm²)时,必须在RTL阶段做Top Partition,将"计算Tile""IO Tile""Memory Tile"划为独立芯粒,分别流片后通过2.5D/3D封装拼回。

三、Partition的四大维度深度解析

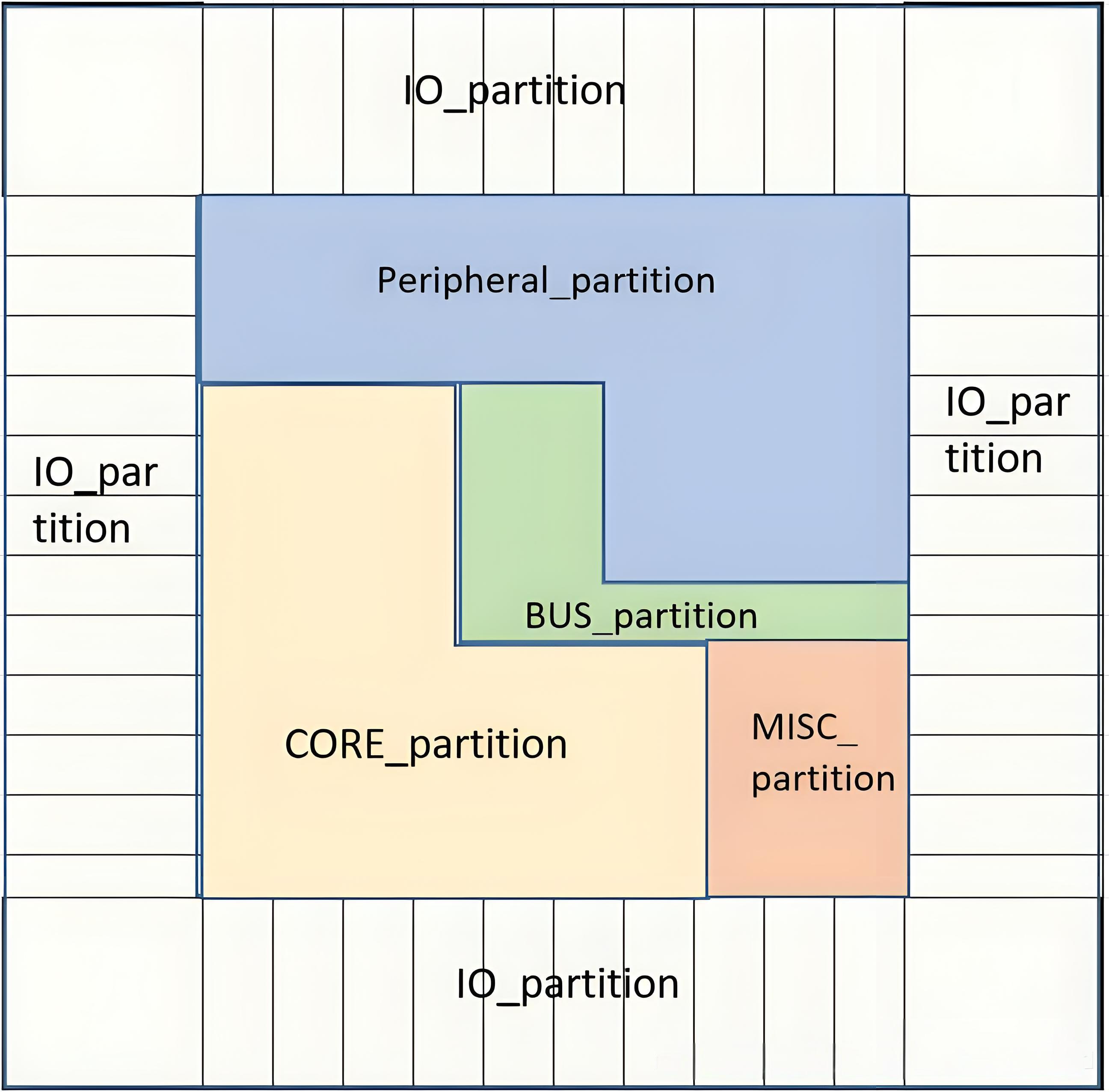

维度一:后端物理Partition------从Floorplan到GDSII

后端物理Partition是工程实现的核心,包含以下关键步骤:

(1)芯片级规划(Chip-Planning) 在RTL Freeze后、Placement前完成"城市总规"式设计:

核心面积、长宽比、利用率规划(通常预留20%通道给顶层PG与跨区信号)

I/O Ring & Bump Map(IO环宽≥60μm,预留ESD与Bump Escape)

电源网格方案(目标IR-Drop<3%,EM裕度>20%)

宏单元预布局(Memory靠边、SerDes靠近对应IO、PLL放中心)

(2)Partition边界与引脚分配(Pin Assignment)

形状划分:根据数据流(Data Flow)确定模块形状,允许非规整形态

出pin层选择:如CPU Core纵向出pin可用M3、M5,避免M7线宽过大

Feed-through通道:实现模块间无缝对接(Channelless),节省面积

(3)电源网格对齐 子模块间PG(Power Grid)需严格对齐,通过"网格参数一致、边界接口可复制、迭代位移≤几μm"实现无缝电流流动。具体包括:

全局网格规律:金属层、线宽/间距、Stripes周期统一

LEF预装:将PG Stripes写入Block LEF,工具自动对齐

Feed-through通道:为Power-Gating区域预留不被关断的"电源桥"

维度二:功能Partition------软硬件协同的架构艺术

功能Partition从系统架构层面划分,遵循软硬件协同设计原则:

划分原则:

功能内聚性:将关联紧密的功能封装在同一Partition,如CPU+Cache+SCU(Snoop Control Unit)形成CPU子系统

数据流导向:根据数据流向摆放模块,减少跨区信号

IP复用最大化:成熟IP(如DDR PHY、PCIe Controller)作为硬宏直接集成

方法论对比:

| 方法 | 流程 | 适用场景 | 优缺点 |

|---|---|---|---|

| Top-Down | 芯片级Floorplan→划Partition→子模块实现→顶层拼接 | 系统级设计、新架构 | 全局视角好,但前期估计误差敏感 |

| Bottom-Up | IP硬宏固化→推导顶层Floorplan→拼接 | IP复用为主、成熟SoC | 周期短30-40%,但顶层布线资源易被卡死 |

| Timing-Driven | 以关键路径延时为目标函数优化划分 | 高频设计、FPGA验证 | 保频率、减迭代,但算法复杂度高 |

| Chiplet-Aware | 功能→工艺/封装协同划分→多Die RTL→2.5D/3D封装 | 超Reticle设计、异构集成 | 超越面积限制,但封装复杂度高 |

维度三:功耗Partition------低功耗设计的物理实现

功耗Partition通过电源域(Power Domain)划分实现精细功耗管理,核心文件为UPF(Unified Power Format):

关键要素:

Power Domain划分:将芯片划分为多个可独立开关的电源域,如CPU Core域、SoC子系统域、IO域等

低功耗特殊单元布局:

Power-Switch:按"头串尾并"放两排,间距1×row-height

Isolation/Retention:靠近分区边界,减少关断后漂电影响

Level-Shifter:跨电压域信号100%覆盖,放在驱动侧

PG连接关系:顶层与Block的PG连接需在UPF中精确定义,确保物理实现一致性

注意事项:

多电压域(Multi-Voltage)引脚需物理隔离,避免串扰

电源序列(Power Sequencing)控制引脚位于可靠区域

跨电源域信号引脚需预留Isolation Cell插入位置

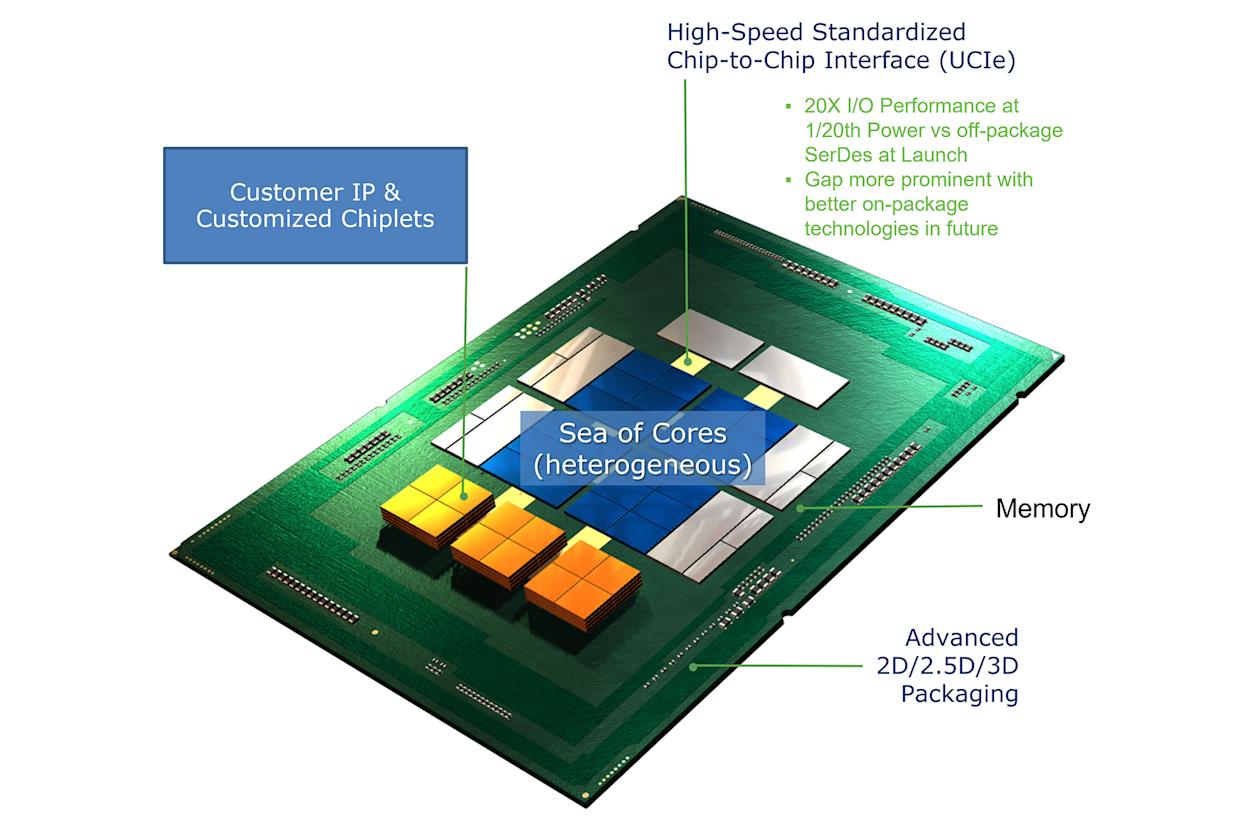

维度四:系统级Partition------Chiplet与异构集成

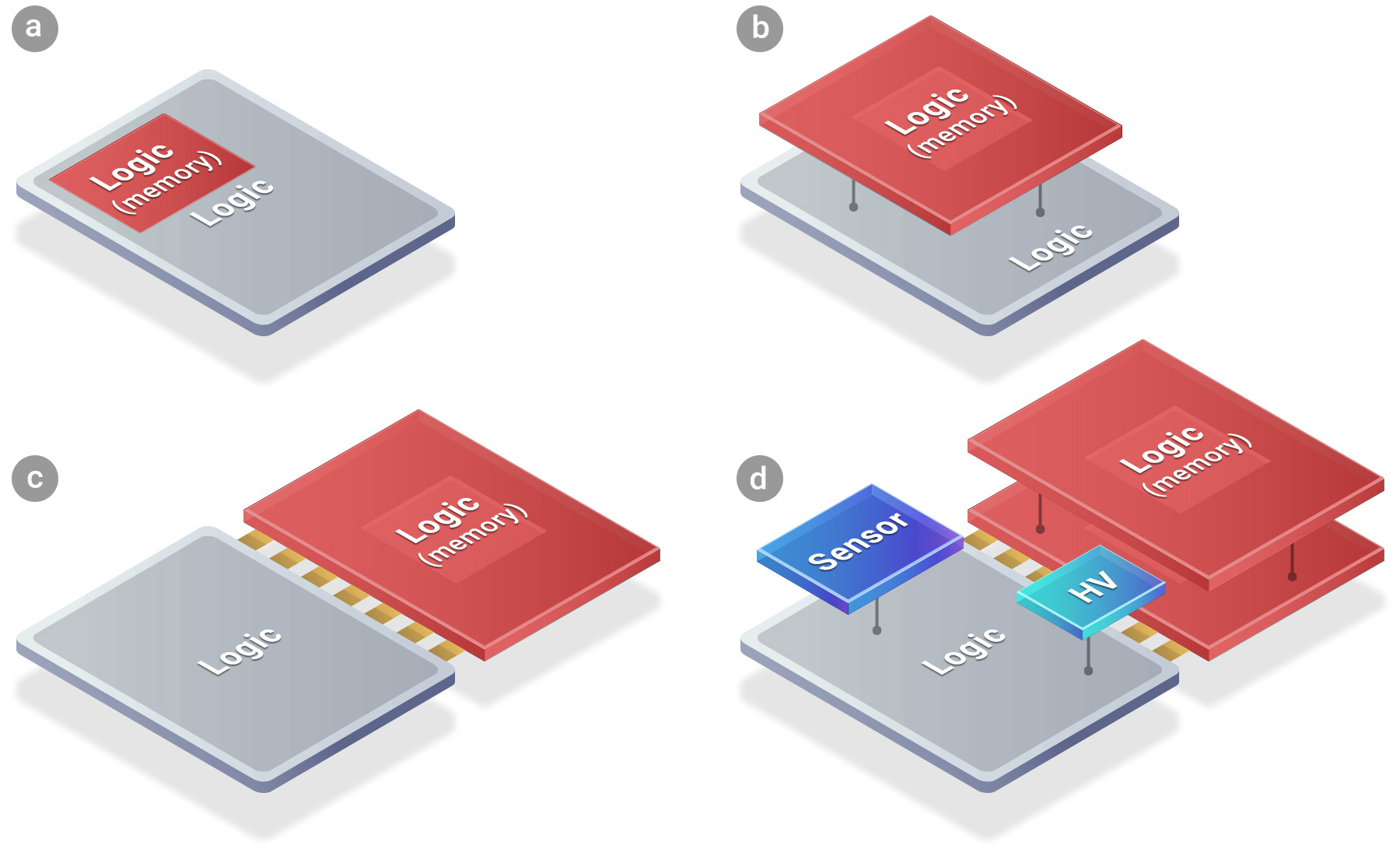

Chiplet是Partition理念在系统级的终极形态,通过"功能特性+工艺敏感度"拆分大芯片:

典型架构:

核心价值:

超越Reticle限制:单封装面积可>2000mm²,实现"晶圆级"算力

成本最优:IO/模拟部分留在老工艺,数字计算部分用新工艺,综合Wafer Cost降低25-40%

迭代加速:计算芯粒升级时,只需重流一片3nm Die,封装基板与IO Die复用

技术支撑:

混合键合(Hybrid Bonding):实现亚10μm键合间距,较传统微凸点(40-55μm)实现量级突破

3D堆叠:Face-to-Face(F2F)实现最短连接路径,Face-to-Back(F2B)通过TSV连接

四、Partition的优缺点与权衡

优点

| 维度 | 具体收益 |

|---|---|

| 工具效率 | 突破Runtime/Memory瓶颈,实现日收敛 |

| 时序质量 | 子块深度优化+接口预算,收敛更快更稳 |

| 团队协作 | 并行开发,周期压缩30-40% |

| 架构灵活 | 支持Chiplet异构集成,工艺灵活组合 |

| 良率提升 | 小芯粒良率远高于大Die,降低生产风险 |

| 成本控制 | 成熟IP复用、老工艺保留,NRE大幅降低 |

缺点与挑战

| 维度 | 具体风险 |

|---|---|

| 前期规划 | 对面积/功耗估计误差敏感,边界定错后期ECO牵动全芯片 |

| 时序预算 | 需在初期做Timing Budget,可能出现部分Block难收敛 |

| 依赖关系 | Sub-top依赖Leaf Partition,顶层工作需等待子模块完成 |

| 验证复杂度 | 最终Signoff需Flatten看结果,跨区路径验证复杂 |

| 封装成本 | Chiplet先进封装占量产成本30%+,远高于传统10% |

| 生态依赖 | 跨Die接口标准化(如UCIe)尚不成熟,需自定义PHY |

五、Partition设计的关键注意事项

基于文档资料与工程实践,总结以下核心要点:

1. 前期规划阶段

Reticle面积预留:单Die面积需留足封装余量,避免"装不下"

ESD面积占坑:Top-Partition阶段即预留ESD Corridor(≥150μm),比后端拼凑省1-2轮迭代

时钟源头统一:若时钟源头在顶层,Block级无需二次声明,工具自动衍生

2. 实现阶段

PG对齐优先:子模块M7层尽量连通形成整体,顶层用AP层打孔形成Power Mesh

Pin Assignment策略:按Timing-Criticality排序,先放时钟/高速总线,再布地址/控制,最后测试信号

Keep-out Margin:预留布线通道,Core Logic Area与IO Ring间保持合理间距

3. Signoff阶段

Cross-Partition STA:必须做,防止"局部优化、全局翻船"

IR-Drop闭环:分区对齐后跑Full-chip带向量功耗分析,检查跨边界节点压降

Formality验证:确保Partition接口逻辑与顶层一致

4. Chiplet特殊考量

TSV/Bond-pad对齐:3D IC需在上下Die Floorplan中同时锁定坐标

热管理:高功耗模块分散布局,设计独立散热通道

机械应力:硅中介层、微Bump、TSV带来新挑战,需协同设计

六、结语:Partition------后摩尔时代的核心设计哲学

从最初为解决工具算力瓶颈的后端手段,到支撑百亿晶体管SoC的层次化方法论,再到实现Chiplet异构集成的系统架构基础------Partition技术正在重新定义芯片设计的边界。

"层次化设计适当下非常流行的设计思路,随着芯片的规模越来越大,fullchip的数据量和复杂度和过去已经不能同日而语"。在摩尔定律放缓的今天,Partition不仅是一种工程技巧,更是连接"More Moore"与"More than Moore"的桥梁,是延续半导体产业创新的关键基石。

无论是正在攻坚5nm以下先进工艺的后端工程师,还是规划下一代AI芯片架构的系统架构师,深入理解Partition的多维内涵,都将成为应对"大芯片"时代挑战的必修课。