描述

地址空间或bd_addr_space对象是一个分配的逻辑可寻址空间

主机接口上的内存,或连接到AXI主机的AXI接口端口上的内存

块设计外部。

Vivado Design Suite的IP集成商遵循行业标准IP-XACT数据

用于捕获内存需求和功能的格式。有些区块可以有一个

与多个主接口相关联的地址空间,例如具有

系统总线和快速存储器总线。其他组件可以具有多个地址空间

与多个主接口相关,一个用于指令,另一个用于数据。

主接口引用地址空间或bd_addr_space对象。当AXI从设备

映射到主地址空间的主地址段(bd_addr_seg)对象是

创建,将从设备的地址段映射到主设备。

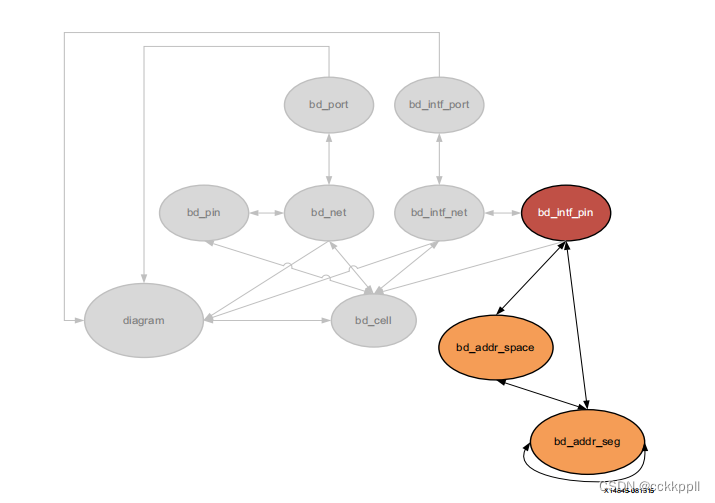

相关对象

主地址段bd_addr_seg与AXI中的地址空间相关联

主接口,在块设计中找到。地址空间由接口引用

引脚bd_intf_pin,位于单元bd_cell上。外部AXI主机与接口相关

端口,bd_intf_port。

您可以查询这些关联对象的bd_addr_space对象:

get_bd_addr_spaces-of_objects[get_bd_cells/microblaze_0]

get_bd_addr_segs-对象的[get_bd_address_spaces-对象的[get_bd_cells

/microblaze_0]]

还可以查询与块设计地址空间关联的对象:

get_bd_intf_pins-of_objects[get_bd_addr_spaces*SLMB]

属性

块设计地址空间对象bd_addr_space的属性包括

以下,具有示例值:

属性类型只读可见值

CLASS字符串true true bd_addr_space

NAME字符串false true数据

OFFSET字符串false true 0x00000000

PATH字符串true true/microblaze_0/Data

RANGE字符串假真0x100000000

TYPE字符串false true

要报告bd_addr_space对象的属性,可以复制并粘贴以下内容

命令输入Vivado Design Suite Tcl shell或Tcl控制台:

report_property-all[lindex[get_bd_addr_spaces]0]

BD_CELL

描述

块设计单元或bd_cell对象是IP集成商IP核心对象的实例,或者是

分层块设计单元。叶单元是IP目录中的核心。分层单元格是

包含一个或多个附加逻辑级别的模块或块,包括叶单元。

bd_cell对象的TYPE属性将块设计单元标识为引线单元

来自IP目录(TYPE==IP),或作为包含附加模块的分层模块

逻辑(TYPE==HIER)。

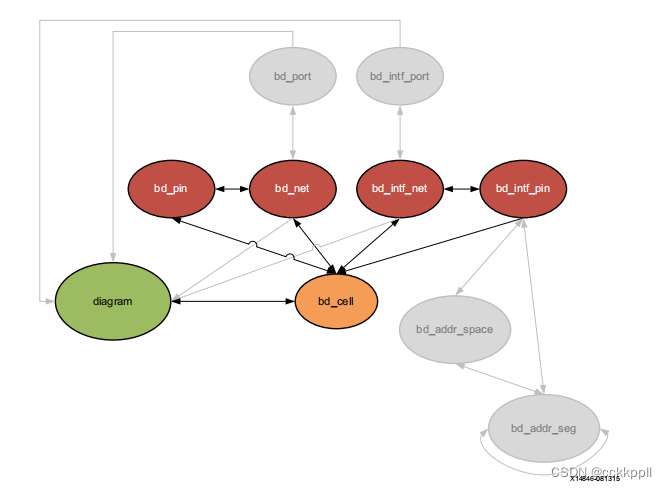

相关对象

如图2-3所示,块设计单元(bd_cell)位于块设计或图中

对象单元包括块设计引脚(bd_pin)和接口引脚(bd_intf_pin),并且可以

分层地包含块设计端口(bd_port)和接口端口(bd_intf_port)。他们

通过网络(bd_net)和接口网络(bd_intf_net)连接。内存相关块

设计单元还可以包含地址空间(bd_addr_space)和地址段

(bd_addr_seg)。可以查询与以下任意单元关联的块设计单元

对象,例如:

get_bd_cells-of_objects[get_bd_addr_spaces]

可以查询与块设计单元关联的对象:

get_bd_addr_spaces-of_objects[get_bd_cells]

也可以查询作为另一个块的层次对象的块设计单元

设计单元:

get_bd_cells-of_objects[get_bd_cells microblaze_0_axi_periph]

属性

块设计单元对象上的特定属性可以是多种多样的,

这取决于对象所代表的IP核心的类型。下表列出了一些

指定给Vivado Design Suite中bd_cell对象的属性,示例值如下:

Property Type Read-only Visible Value

CLASS string true true bd_cell

CONFIG.C_ALL_INPUTS string false true 0

CONFIG.C_ALL_INPUTS_2 string false true 0

CONFIG.C_ALL_OUTPUTS string false true 1

CONFIG.C_ALL_OUTPUTS_2 string false true 0

CONFIG.C_DOUT_DEFAULT string false true 0x00000000

CONFIG.C_DOUT_DEFAULT_2 string false true 0x00000000

CONFIG.C_GPIO2_WIDTH string false true 32

CONFIG.C_GPIO_WIDTH string false true 4

CONFIG.C_INTERRUPT_PRESENT string false true 0

CONFIG.C_IS_DUAL string false true 0

CONFIG.C_TRI_DEFAULT string false true 0xFFFFFFFF

CONFIG.C_TRI_DEFAULT_2 string false true 0xFFFFFFFF

CONFIG.Component_Name string false true base_mb_axi_gpio_0_0

CONFIG.GPIO2_BOARD_INTERFACE string false true Custom

CONFIG.GPIO_BOARD_INTERFACE string false true led_4bits

CONFIG.USE_BOARD_FLOW string false true true

LOCATION string false true 5 1720 200

LOCK_UPGRADE bool false true 0

NAME string false true axi_gpio_0

PATH string true true /axi_gpio_0

SCREENSIZE string false true 180 116

SDX_KERNEL string true false false

SDX_KERNEL_SIM_INST string true false

SDX_KERNEL_SYNTH_INST string true false

SDX_KERNEL_TYPE string true false

SELECTED_SIM_MODEL string false true rtl

TYPE string true true ip

VLNV string true true xilinx.com:ip:axi_gpio:2.0

To report the properties for a bd_cell object, you can copy and paste the following

command into the Vivado Design Suite Tcl shell or Tcl Console:

report_property -all [lindex [get_bd_cells] 0]