led.v

verilog

module led

#(

parameter P_CLK_FREQ_MHZ = 27, // 时钟频率,单位MHz,默认50MHz

parameter P_DEBOUNCE_MS = 20, // 消抖时间,单位ms,默认20ms

parameter L_CNT_WIDTH = 32 // 需要外部计算后传入

)

(

input wire i_clk , //系统时钟50Mhz

input wire i_rst_n , //全局复位

input wire i_key_B , //按键B输入信号

output wire [2:0] o_led, // 110 R, 101 B, 011 G

output wire [7:0] o_D

);

assign o_D={i_key_B,i_key_B,i_key_B,i_key_B,i_key_B,i_key_B,i_key_B,i_key_B};

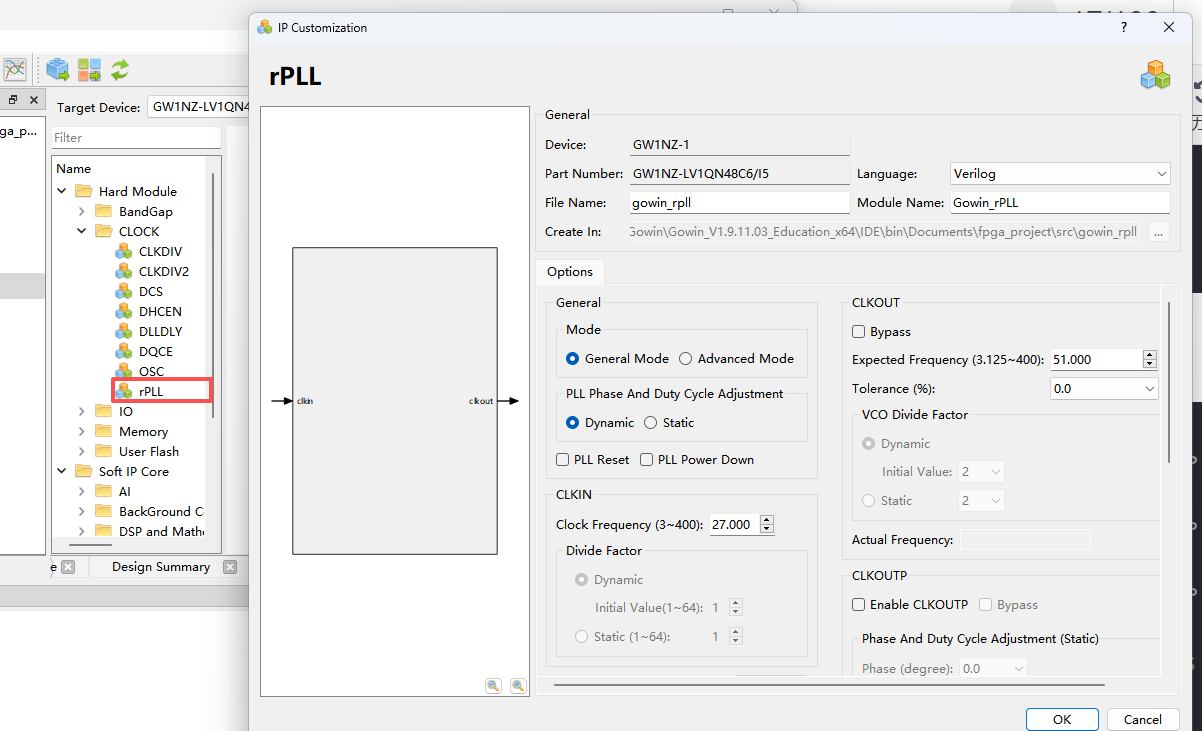

Gowin_rPLL your_instance_name(

.clkout(o_led[0]), //output clkout

.clkin(i_clk ) //input clkin

);

endmoduleled_prj.cst

Tang-Nano-1K 有几个引脚不能自由使用比如DONE, READY

bash

IO_LOC "o_led[2]" 11;

IO_PORT "o_led[2]" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

IO_LOC "o_led[1]" 10;

IO_PORT "o_led[1]" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

IO_LOC "o_led[0]" 9;

IO_PORT "o_led[0]" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

IO_LOC "i_rst_n" 13;

IO_PORT "i_rst_n" IO_TYPE=LVCMOS33 PULL_MODE=UP;

IO_LOC "i_clk" 47;

IO_PORT "i_clk" IO_TYPE=LVCMOS33 PULL_MODE=UP;

IO_LOC "i_key_B" 44;

IO_PORT "i_key_B" IO_TYPE=LVCMOS33 PULL_MODE=UP;

IO_LOC "o_D[7]" 40;

IO_PORT "o_D[7]" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

IO_LOC "o_D[6]" 41;

IO_PORT "o_D[6]" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

IO_LOC "o_D[5]" 38;

IO_PORT "o_D[5]" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

IO_LOC "o_D[4]" 39;

IO_PORT "o_D[4]" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

IO_LOC "o_D[3]" 42;

IO_PORT "o_D[3]" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

IO_LOC "o_D[2]" 35;

IO_PORT "o_D[2]" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

IO_LOC "o_D[1]" 17;

IO_PORT "o_D[1]" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

IO_LOC "o_D[0]" 16;

IO_PORT "o_D[0]" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;