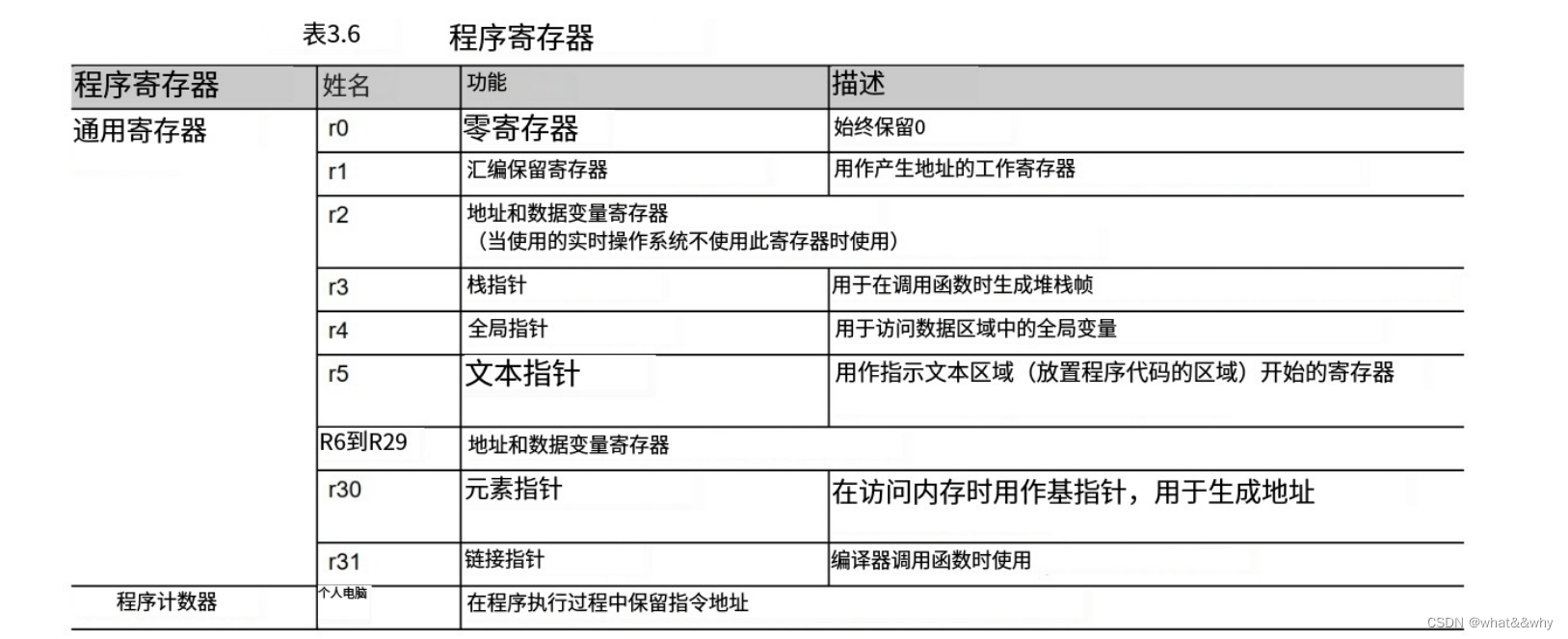

硬件规格(引脚分配,内存映射,外设功能规格、电气特性、时序图 )和操作说明

注意:有关使用的详细信息,请参阅应用说明 ---------外围函数。。。

1:存储指令完成与后续同步指令的一代

当控制寄存器被存储指令更新 时,从存储的执行开始有一个时间延迟

指令,以实际更新控制寄存器。因此,适当的处理在执行之前,需要同步以确保控制寄存器 反映更新的值 随后的指令。有关使用LDSR指令更新系统寄存器的程序的详细信息和

系统注册更新后的危害管理----如果在执行STSR指令之前执行LDSR指令来更新系统寄存器的设置

是为了读取系统寄存器或在调用CALLT指令或类似指令之前执行的 ,它使用系统则必须反映新的设置,以便执行所需的操作。这个CPU保证如果LDSR指令被用来更新表中所示的系统寄存器

当后续指令被执行时,新的寄存器设置将被应用。然而,它不保证新的设置将在指令获取中应用。在这种情况下,需要同步进程。同样,EI或DI指令的执行也以相同的方式处理

通过LDSR指令更新PSW的方式;也就是说,可以保证由EI或DI指令应用于后续指令。

注1:在LDSR和STSR指令的表示中,选择ID表示为selID 。

注2::该表包括一个寄存器的值不能更新,一个寄存器的位值不能更新无法更新。

注3:如果更新了这些控制中断接受的寄存器,中断将被接收

如果中断请求在执行后续指令时出现,则新的寄存器设置 。

注4:如果这些寄存器(控制寄存器库函数)被更新,中断将被接受

如果中断请求在执行后续指令时出现,则新的寄存器设置。

然而,当RESBANK指令在更新RBCR0之后执行时。同步流程是必需的 。

注5:如果执行LDSR指令以更新MPLA, MPUA或MPAT寄存器,则立即在另一条指令之后

执行LDSR指令更新MPIDX寄存器,保证MPIDX的新设置

反映在随后的说明中。为了读取MPLA, MPUA,或MPAT寄存器,使用STSR指令更新MPIDX寄存器后,需要一个同步过程。

注6:RH850/U2A不支持FXU系统寄存器。

MPU---

通过操纵MPU函数寄存器来更新内存保护设置的详细,更新主控板的内存保护设置。

要在获取后续指令时反映更新的设置,请执行SYNCI, eret和FERET指令 。但是,请注意,该指令是否读取不知道同步指令本身是否使用新的保护设置获取。在这个

在这种情况下,需要执行以下操作。

i)仅在用户模式下启用内存保护,在主管模式下更新设置。

ii)更新允许执行指令区域的内存保护设置。

iii)确定设置内存区域的指令执行,包括指令获取

待启用的同步指令用于更新PSW。操作UM ,使用中描述的EIRET or FERET指令.

请注意,这些指示是主管特权指示。意思是PSW的状态。嗯

只能从0(清除)修改为1(设置),管理员模式修改为用户模式

**2:控件中反映控制寄存器或内存中的更新结果时

后续指令的执行:**

例1:中断可以通过在中断后执行EI指令来启用

通过访问INTC2和外围电路中的控制寄存器来清除请求 。继续进行

在本例中如下所示。

(1)存储指令更新控制寄存器(ST.W等)

(2)上述控制寄存器(LD.W等)的虚读*1

(3) SYNCP

(4)后续指令(EI等)

例2:实现相同的处理,即使在访问需要等待安全之后

将一个给定的控制寄存器(寄存器a)更新到另一个控制寄存器(寄存器B)

以下情况:不同外设模块的互连操作和释放时

设置外围模块后,在INTC中中断掩码。

但是,如果控制寄存器A和B在同一个P-Bus组中,则不需要进行此处理。

对于P-Bus组和外围模块/寄存器之间的对应关系,请参见各自

部分。

(1)存储更新控制寄存器A的指令(ST.W等)

(2)上述控制寄存器(LD.W等)的虚读*1

(3) SYNCP

(4)存储/加载指令到访问控制寄存器B (ST.W, LD.W等)

范围内访问控制寄存器和内存时也需要进行相同的处理

等待内存等安全功能设置完成后开始保护

保护、ECC校验等。

此外,在保证存储访问的完成时也需要相同的处理

内存。

注1。可以使用同一P-Bus组的任何寄存器的虚拟读取来代替.

3:当控制寄存器和存储器中的更新结果反映在

获取后续指令的指令;

1. 如果你想写入一个指令到RAM,然后分支到RAM执行写入

说明,按以下步骤操作。

(1)存储指令来更新内存(ST.W .等)

(2)上述内存的虚拟读取(ld、w等)

(3) SYNCI

(4)后续指令(分支指令等)

2. 在等待完成更新控件后,分支到目标内存时

寄存器的内存保护和ECC,这样做如下。

(1)存储指令更新控制寄存器(ST.W等)

(2)控制寄存器的虚读(LD.W等)

(3) SYNCI

(4)后续指令(分支指令等)

4:加载指令完成和后续的同步指令的一代

当一个控制寄存器和内存被一个加载指令访问时 ,数据访问的顺序也是不保证程序顺序相同。因此,适当的同步处理 是为确保完成后续数据访问指令的加载指令而必需的 。

然而,同步处理对于访问某些目标数据空间是不必要的 。

负载同步的处理如下所示。

在访问地址a之前,需要等待完成对地址a的加载访问

其他地址B,在这种情况下进行如下操作。

(1)引用地址A的加载指令(LD.W等*1)

(2) SYNCP

(3)存储/加载指令访问地址B (ST.W, LD.W等)

注;加载指令:LD.*, SLD. **, LDV。*、tst1、set1、clr1、not1、popsp、resbank、dispose、switch、

call,系统呼叫,出租车,LDL

存储说明:ST.*, SST。STV *。*、set1、clr1、not1、pushsp、prepare、caxi

以下目标数据空间内的数据访问的操作顺序与程序。

-代码Flash

- H-Bus区0、1、2、3组

---调试(CPU0, CPU1, CPU2, CPU3)

-仪表RAM

-集群ERAM(集群0,1)

-全局仿真RAM

-集群RAM(集群0、1、2、3)

-

P-Bus区0、1、2H/2L、3、4、5、6H/6L、7、8、9组

-

i -总线区域,0,1,2组CPU外设区(self、CPU0、CPU1、CPU2、CPU3)

以下目标数据空间内的加载访问可以在完成前面的访问(加载或存储)。为了保证的秩序访问时,需要软件对上述访问进行同步处理。

---本地内存(self, CPU0, CPU1, CPU2, CPU3)

对于不同目标空间之间的数据访问,数据访问的顺序不一致

保证为程序订单。为了保证访问顺序,由软件进行同步处理事先访问是必要的

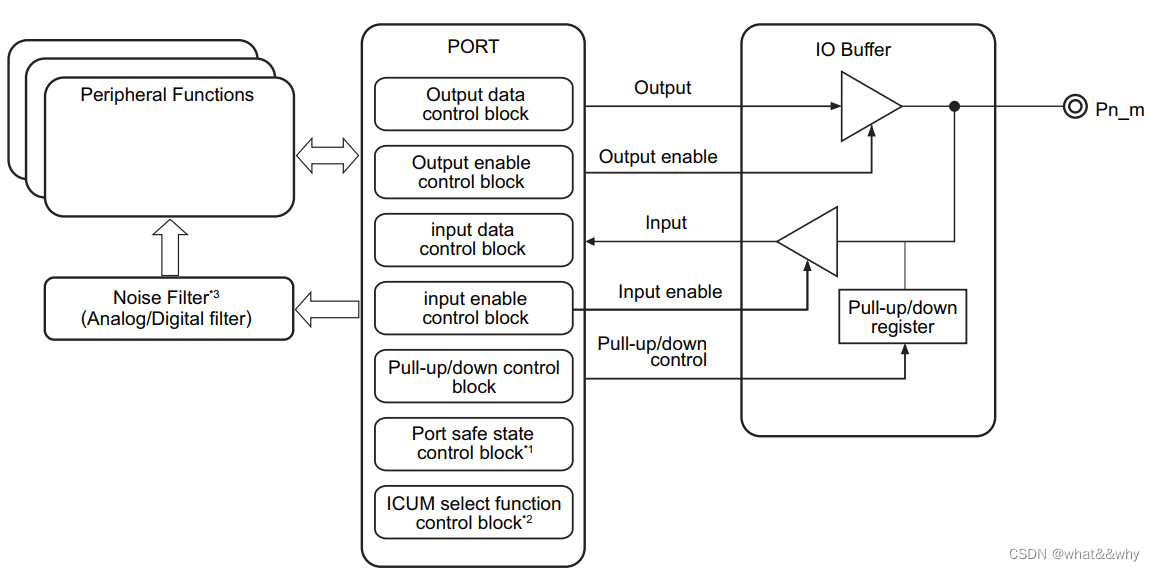

PIN

物理引脚。每个引脚都用唯一的引脚编号 表示。

一个引脚可以在几种模式下 使用。每个引脚都有一个名字来反映它的功能,也就是由所选模式决定。

PIN根据其功能和配置不同,有内部的电路设置参考手册可以获取到引脚的限定电压值

电压超调5.8 V ~ 6.5 V,累计时间小于2h。电压超调5.5 V;允许至5.8 V,累计时间小于100h。

电压超调范围允许为1.205 V ~ 1.42 V,累计时间小于2h;允许电压为1.155 V ~ 1.205 V,累计时间小于100h。

电压超调3.9 V ~ 4.6 V,累计时间小于2h。电压超调3.6 V;至3.9 V允许,累计时间小于100h。

输入电压应保持在-0.8 V≤Vin≤6.5 V。电源电压必须保持在额定范围内值。在所有状态下,注入电流必须保持在额定值内,包括升压/降压和开/关。注入电流影响封装的散热特性。

输入电压、模拟参考电压和模拟输入电压不得大于6.5 V。

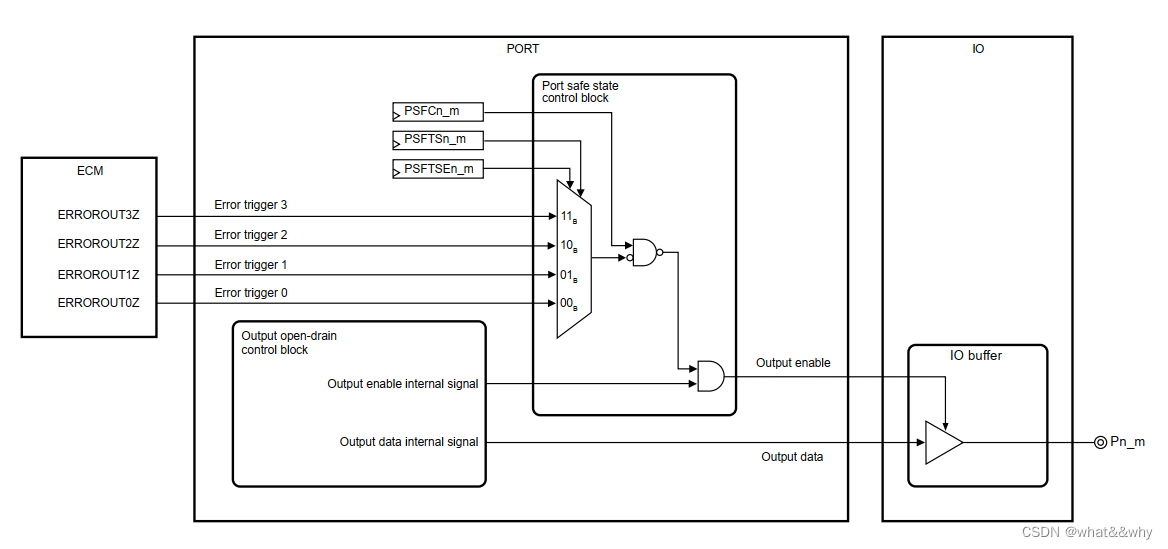

端口安全状态命令功能

Pn_m和APn_m具有端口安全状态功能,可以操作每个引脚的输出使能

分别通过为已定义的应用程序选择错误触发器 。本产品最多支持4个错误 名为ERROROUT0Z、ERROROUT1Z、ERROROUT2Z和ERROROUT3Z的触发器 ,以及触发器可以通过设置PSFTSn_m和PSFTSEn_m寄存器来选择 。有关错误触发器的详细信息

错误控制模块(ECM)。

当端口被错误触发时,引脚的输出使能控制被强制关闭

通过设置PSFCn_m寄存器开启安全状态功能。甚至双向模式的输出数据也是如此

在发出错误触发器期间由端口安全状态函数抑制。

注意:来自ECM的错误触发器由DeepSTOP Reset和引脚状态触发;当端口安全状态函数为时,位于AWO区域的位置成为高阻抗。

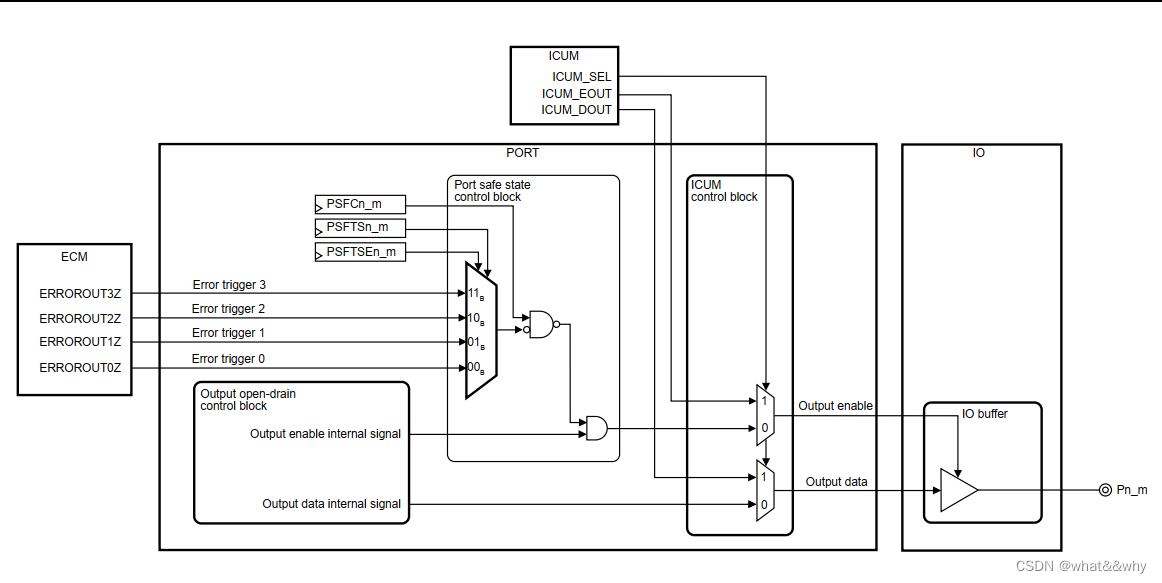

ICUM选择功能

目标引脚:ICUM Select Function在端口函数中优先级最高,用于控制端口的输出值。

注1:选择的可选功能信号。

注2:函数存在,需要"直接I/O控制"的备选函数有支持此配置。

注3:输出驱动强度可通过PDSCn_m和PUCCn_m设置。

注4:输入缓冲区类型可以通过PISn_m和PISAn_m设置。

注5:端口安全状态功能的详细描述安全状态功能。

注6:ICUM选择功能的目标引脚,需要额外的更高优先级控 制。

注7。支持LVDS缓冲区的备选函数具有来自LVDS寄存器的附加控制逻辑。,包含LVDS缓冲区的函数。

寄存器定义

|-----------------------------------------------------|-----------------------------|---|---|---|---|

| Port register | 引脚寄存器----引脚高电位还是低电位 | | | | |

| Port Set Reset register | | | | |

| Port NOT register | | | | |

| | | | |

| Port Pin Read register | 引脚读寄存器--只读--获取引脚是高还是低电位 | | | |

| Port Mode register | 引脚模式寄存器--引脚模式是输入还是输出 | | | |

| Port Mode Control register | 引脚模式控制寄存器---普通模式还是复用模式(备用) | | | |

| | | | |

| Port Function Control register | 引脚模式控制寄存器---普通模式还是复用模式(备用) | | | |

| | | | |

| Port Function Control Expansion register | 端口功能控制扩展寄存器--根据功能表配置io的输入输出 | | | |

| | | | |

| Port Mode Set Reset register | 引脚模式设置复位寄存器 | | | |

| Port Mode Control Set Reset register | 引脚模式控制复位寄存器 | | | |

| | | | |

| Port Function Control Additional Expansion register | 端口功能控制附加扩展表 | | | |

| Port output value Inversion register | 引脚反转 | | | |

| Port Input Buffer Control register | 引脚缓存 | | | |

|------------------------------------------------------|--------------------|---|---|---|---|

| Port Bi-Direction Control register | 引脚缓存和输出模式配置寄存器 | | | | |

| | | | |

| Port IP Control register | 引脚方向和功能控制 | | | |

| Pull-Up option register | 上拉配置寄存器 | | | |

| Pull-Down option register | 下拉配置寄存器 | | | |

| Port Open Drain Control register | 引脚开通控制控制寄存器 | | | |

| | | | |

| | | | |

| Port Drive Strength Control register | 引脚驱动能力寄存器 | | | |

| Port Input buffer Selection register | 引脚输入缓存寄存器 | | | |

| | | | |

| Port Input buffer Selection Advanced register | | | | |

| | | | |

| Port Universal Characteristic Control register | 引脚电压电气参数控制寄存器 | | | |

| | | | |

| Port Open Drain Control Expansion register | 控制开启仿真p通道寄存器 | | | |

| | | | |

| Port Control register | 引脚控制寄存器 | | | |

| | | | |

| | | | |

| Port Safe State Control register | 引脚安全状态控制寄存器 | | | |

| | | | |

| Port Safe State Trigger Selection register | 引脚安全状态触发选择寄存器 | | | |

| Port Safe State Trigger Selection Expansion register | 引脚安全状态触发器选择寄存器 | | | |

| | | | |

| Port Keycode Protection Register | 引脚写寄存器 | | | | |

| LVDS control A register | 低压差分输入输出配置寄存器 | | | | |

| LVDS control B register |

启用

通用场景

术语库

如果有这种情况,接收数据缓冲区将满*1时MSPInCFGm0。MSPInRXEm =

在主模式和直接存储器模式下,会产生一个额外的接收中断。的旗帜

MSPInRXDAm0。MSPInRXDAm0[31:0];MSPInRXRQFm受此影响

问题。

(2)第一期-(2)

如果有这种情况,接收数据缓冲区将满*1时MSPInCFGm0。MSPInRXEm =

1和MSPInCFGm0。MSPInFCCEm = 0在主模式和直接内存模式,必要的

在帧端不产生接收中断。的旗帜

MSPInRXDAm0。MSPInRXDAm0;MSPInRXRQFm受此影响

问题。

(3)第一期-(3)

如果接收帧数大于fifo数时

MSPInCFGm0。MSPInRXEm = 1在主模式和固定FIFO内存模式,接收

中断在接收完成之前产生。的旗帜

MSPInRXDAm0。MSPInCSTRm MSPInRXDAm0。MSPInFIRXNm[7:0]和MSPInRXRQFm

都受到这个问题的影响。

(4)第一期-(4)

如果有这种情况,接收数据缓冲区将满*1时MSPInCFGm0。MSPInRXEm = 1 at

从模式和直接内存模式,无法检测到超时错误。此外,如果数字

当MSPInCFGm0时,接收帧数大于FIFO数。MSPInRXEm

模式和固定的FIFO内存模式,不能检测到超运行错误。的旗帜

MSPInRXDAm0。MSPInCSTRm MSPInRXDAm0。MSPInFIRXNm 7:0, MSPInRXRQFm,

MSPInACTFm, MSPInCHENm, MSPInCFCNTm。MSPInCFCNTm ,

MSPInCESTm。MSPInOVREEm和MSPInOVRUEm受此问题影响。