描述

系统监视器HW_SYSMON是Xilinx上的一个模数转换器(ADC)电路

用于测量诸如温度和电压之类的操作条件的设备。这个

HW_SYSMON通过片上温度和电源监控物理环境

传感器。ADC为一系列应用提供了高精度模拟接口。这个

ADC最多可访问17个外部模拟输入通道。

HW_SYSMON具有存储当前

温度和电压值。当前硬件设备上这些寄存器中的值

可以通过Vivado Design Suite的硬件管理器功能访问,当

连接到硬件服务器和目标。HW_SYSMON在Virtex-7之间变化

设备和UltraScale设备。请参阅UltraScale体系结构系统监视器高级版

规范用户指南(UG580)[Ref 12]或7系列FPGA和Zynq-7000 SoC XADC

双12位1 MSPS模数转换器用户指南(UG480)[参考文献6]或更多信息

关于XADC的特定寄存器的信息以及如何对它们进行寻址。

尽管可以使用get_hw_sysmon_reg命令访问存储的十六进制值

在系统监视器的寄存器中,还可以将某些寄存器的值检索为

hw_sysmon对象的格式化属性。例如,以下代码检索

指定的hw_sysmon对象的TEMPERATURE属性,而不是直接

访问寄存器的十六进制值:

get_property TEMPERATURE[get_hw_sysmons]

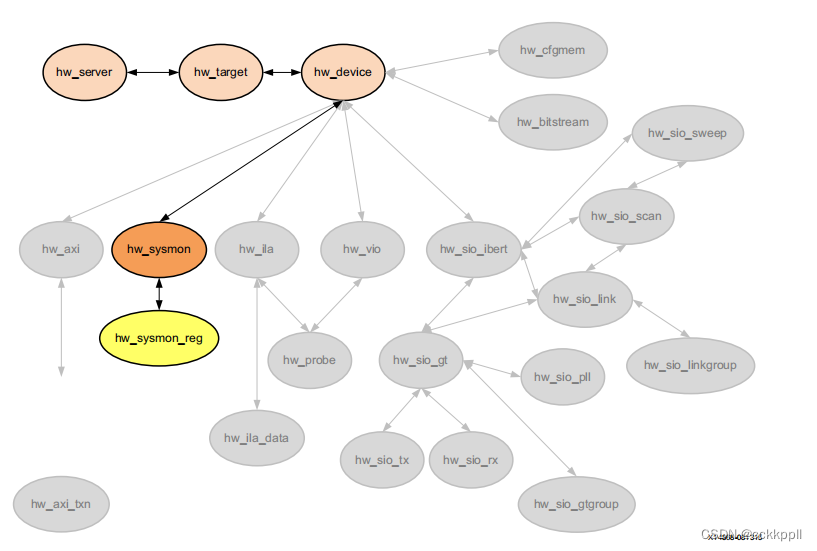

相关对象

HW_SYSMON对象可以在编程的上的硬件管理器中找到

在当前的hw_target和hw_server上。可以查询的hw_sysmon

hw_device如下:

get_hw_sysmons-共[get_hw_devices]

属性

可以使用report_property命令报告指定给的实际特性

HW_SYSMON对象。请参阅Vivado Design Suite Tcl命令参考指南

(UG835)[参考文献13]了解更多信息。

要报告HW_SYSMON的属性,可以复制并粘贴以下内容

命令输入Vivado Design Suite Tcl shell或Tcl控制台:

report_property-all[lindex[get_hw_sysmons]0]

以下是在hw_sysmon对象上找到的属性:

Property Type Read-only Visible Value

ADC_A_GAIN hex true true 0000

ADC_A_OFFSET hex true true 007e

ADC_B_GAIN hex true true 0000

ADC_B_OFFSET hex true true ffbb

CLASS string true true hw_sysmon

CONFIG_REG.ACQ binary false true 0

CONFIG_REG.ALM0 binary false true 0

CONFIG_REG.ALM1 binary false true 0

CONFIG_REG.ALM2 binary false true 0

CONFIG_REG.ALM3 binary false true 0

CONFIG_REG.ALM4 binary false true 0

CONFIG_REG.ALM5 binary false true 0

CONFIG_REG.ALM6 binary false true 0

CONFIG_REG.AVG binary false true 00

CONFIG_REG.BU binary false true 0

CONFIG_REG.CAL0 binary false true 0

CONFIG_REG.CAL1 binary false true 0

CONFIG_REG.CAL2 binary false true 0

CONFIG_REG.CAL3 binary false true 0

CONFIG_REG.CAVG binary false true 0

CONFIG_REG.CD binary false true 00000000

CONFIG_REG.CH binary false true 00000

CONFIG_REG.EC binary false true 0

CONFIG_REG.MUX binary false true 0

CONFIG_REG.OT binary false true 0

CONFIG_REG.PD binary false true 00

CONFIG_REG.SEQ binary false true 0000

DESCRIPTION string true true XADC

FLAG.ALM0 binary true true 0

FLAG.ALM1 binary true true 0

FLAG.ALM2 binary true true 0

FLAG.ALM3 binary true true 0

FLAG.ALM4 binary true true 0

FLAG.ALM5 binary true true 0

FLAG.ALM6 binary true true 0

FLAG.JTGD binary true true 0

FLAG.JTGR binary true true 0

FLAG.OT binary true true 0

FLAG.REF binary true true 0

LOWER_TEMPERATURE string false true -273.1

LOWER_TEMPERATURE_SCALE enum false true CELSIUS

LOWER_VCCAUX string false true 0.000

LOWER_VCCBRAM string false true 0.000

LOWER_VCCINT string false true 0.000

LOWER_VCCO_DDR string false true 0.000

LOWER_VCCPAUX string false true 0.000

LOWER_VCCPINT string false true 0.000

MAX_TEMPERATURE string true true 41.7

MAX_TEMPERATURE_SCALE enum false true CELSIUS

MAX_VCCAUX string true true 1.805

MAX_VCCBRAM string true true 0.997

MAX_VCCINT string true true 1.000

MAX_VCCO_DDR string true true 0.000

MAX_VCCPAUX string true true 0.000

MAX_VCCPINT string true true 0.000

MIN_TEMPERATURE string true true 37.3

MIN_TEMPERATURE_SCALE enum false true CELSIUS

MIN_VCCAUX string true true 1.800

MIN_VCCBRAM string true true 0.993

MIN_VCCINT string true true 0.997

MIN_VCCO_DDR string true true 2.999

MIN_VCCPAUX string true true 2.999

MIN_VCCPINT string true true 2.999

NAME string true true

localhost/xilinx_tcf/Digilent/210203336599A/xc7k325t_0/SYSMON

SUPPLY_A_OFFSET hex true true 006b

SUPPLY_B_OFFSET hex true true ffa9

SYSMON_REFRESH_RATE_MS int false true 0

TEMPERATURE string true true 37.8

TEMPERATURE_SCALE enum false true CELSIUS

UPPER_TEMPERATURE string false true -273.1

UPPER_TEMPERATURE_SCALE enum false true CELSIUS

UPPER_VCCAUX string false true 0.000

UPPER_VCCBRAM string false true 0.000

UPPER_VCCINT string false true 0.000

UPPER_VCCO_DDR string false true 0.000

UPPER_VCCPAUX string false true 0.000

UPPER_VCCPINT string false true 0.000

VAUXP0_VAUXN0 string true true 0.000

VAUXP1_VAUXN1 string true true 0.000

VAUXP2_VAUXN2 string true true 0.000

VAUXP3_VAUXN3 string true true 0.000

VAUXP4_VAUXN4 string true true 0.000

VAUXP5_VAUXN5 string true true 0.000

VAUXP6_VAUXN6 string true true 0.000

VAUXP7_VAUXN7 string true true 0.000

VAUXP8_VAUXN8 string true true 0.000

VAUXP9_VAUXN9 string true true 0.000

VAUXP10_VAUXN10 string true true 0.000

VAUXP11_VAUXN11 string true true 0.000

VAUXP12_VAUXN12 string true true 0.000

VAUXP13_VAUXN13 string true true 0.000

VAUXP14_VAUXN14 string true true 0.000

VAUXP15_VAUXN15 string true true 0.000

VCCAUX string true true 1.802

VCCBRAM string true true 0.995

VCCINT string true true 0.999

VCCO_DDR string true true 0.000

VCCPAUX string true true 0.000

VCCPINT string true true 0.000

VP_VN string true true 0.000

VREFN string true true 0.000

VREFP string true true 0.000