基于Nios-II实现流水灯的主要原理

涉及到FPGA(现场可编程门阵列)上的嵌入式软核处理器Nios II与LED控制逻辑的结合。以下是详细的实现原理,分点表示并归纳:

Nios II软核处理器介绍:

Nios II是Altera公司推出的一种应用于Intel FPGA的32位RISC嵌入式处理器。

它拥有强大的性能和可定制特性,允许用户在FPGA内部构建多个处理器,以完成复杂系统的各项功能。

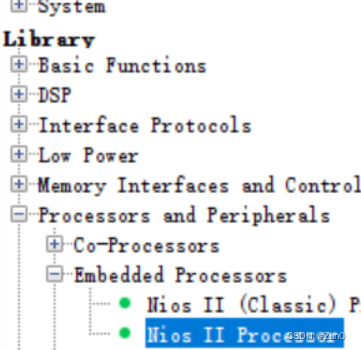

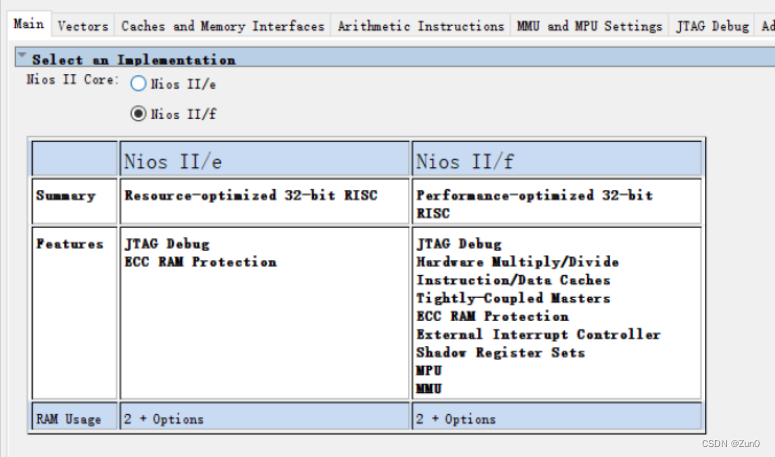

Nios II包括三种产品:Nios II/f(快速)、Nios II/s(标准)和Nios II/e(经济),分别对应不同的性能需求和FPGA使用量。

流水灯控制原理:

流水灯的实现依赖于LED灯和相应的控制逻辑。

通过Nios II软核处理器编写控制LED灯闪烁的用户程序代码,并将其固化在FPGA的片内ROM中执行。

变量、堆栈等空间使用FPGA的片内RAM,无需外部存储器。

基于Nios-II实现流水灯

1.新建项目,选择芯片

2.osys设计

2.1 进入Tools -> Platform Designer

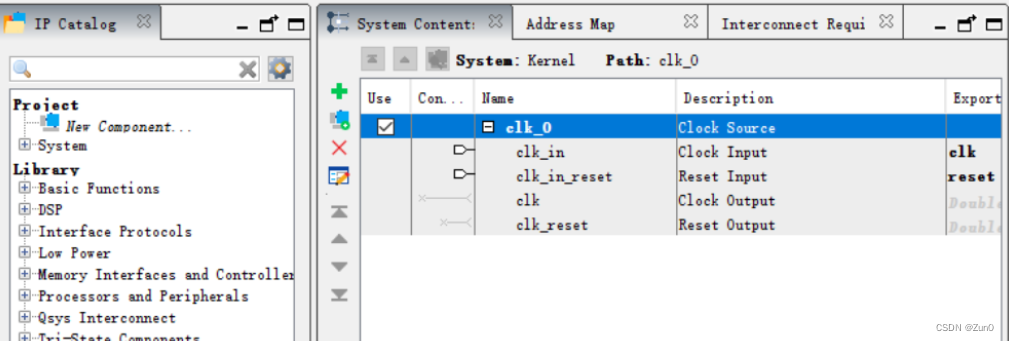

2.2 设置时钟主频

2.3 添加Nios-II Processor并设置

在"Advanced Features"标签栏中保持默认设置,

在"MMU and MPU Settings"标签栏中保持默认设置,

在"JTAG Debug Module"标签栏中保持默认设置(注意勾选 Include JTAG Debug),

点击 Finish 回到 PD 界面。

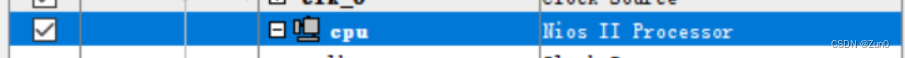

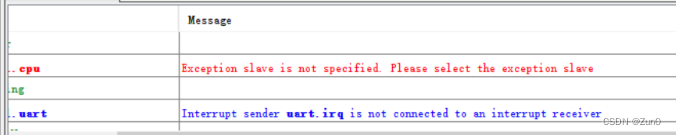

将 nios2_qsys_0 重命名为 cpu,点击"Rename"即可重新命名,操作完成后如下图所示。

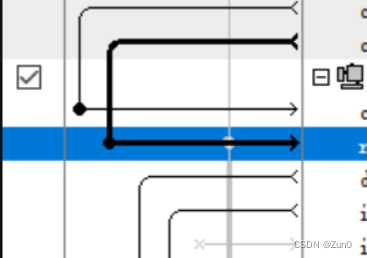

将 cpu 的 clk 和 reset 分别与系统时钟 clk_0 的 clk 和 clk_reset 相连。

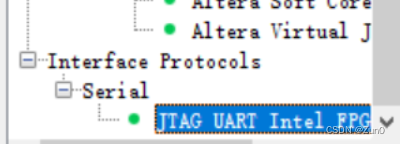

2.4 添加JTAG并配置

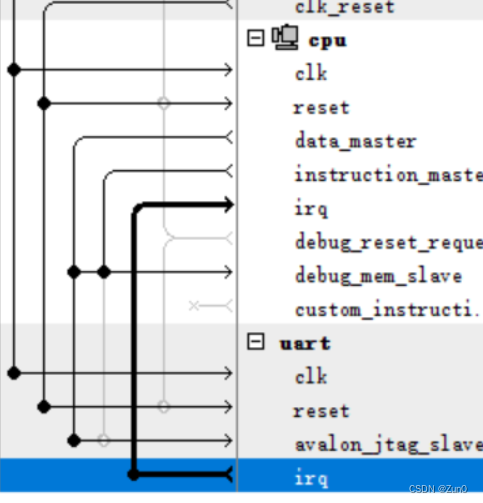

左边选择JTAG_UART_Intel_FPGA_IP,点击Add。右键重命名为uart,并按图进行时钟线,复位线,数据线的连接:同时还要连接中断

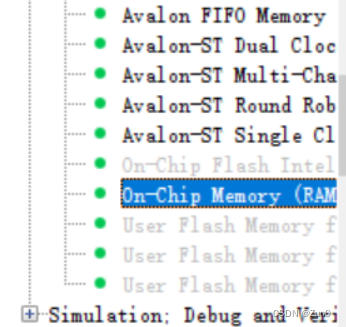

2.5 添加RAM

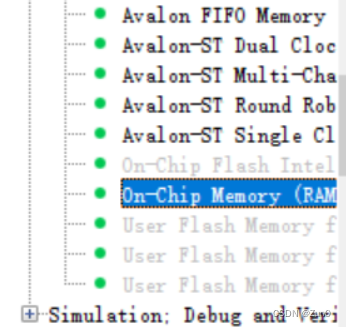

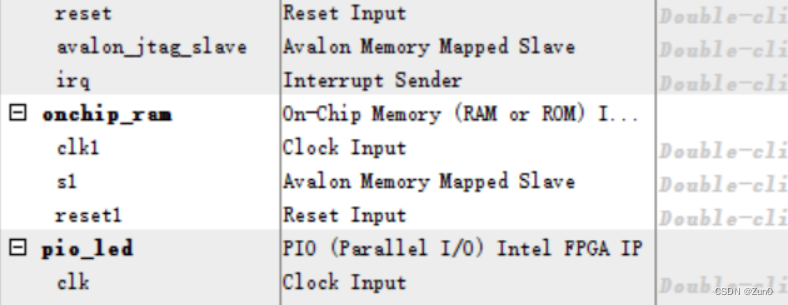

选择On-Chip Memory (RAM or ROM) Intel FPGA,点击Add加入。

更改名字并连线

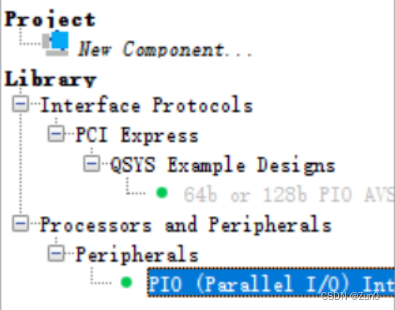

2.6 添加PIO

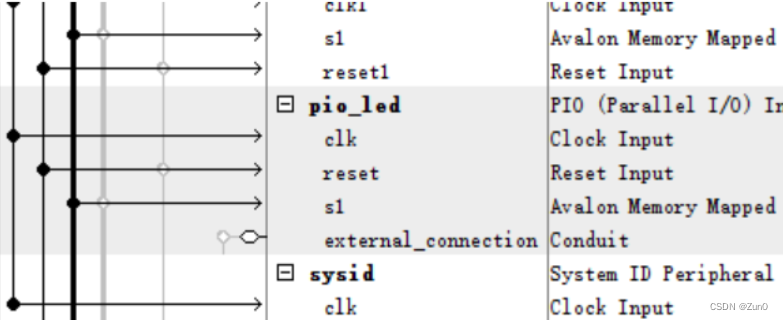

连接clk,reset,s1并导出输出端口:

这里将输出命名为out_led

2.7 添加System ID Peripheral

进行连接

2.8 其他设置

基地址分配:点击 PD 主界面菜单栏中的"System"下的"Assign Base Addresses"。

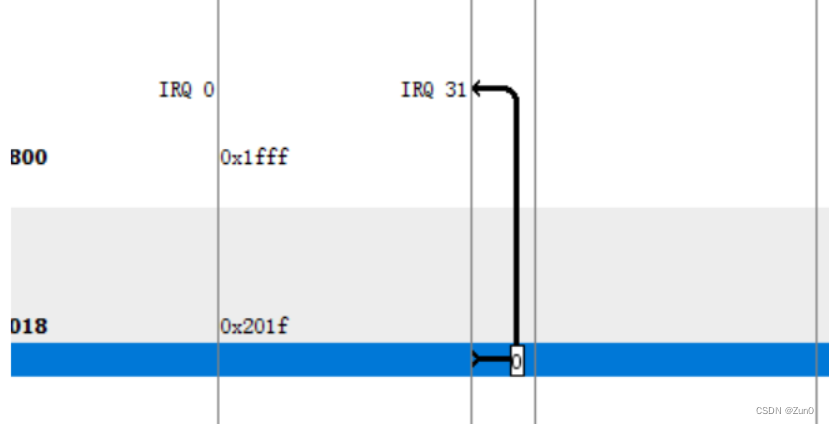

分配中断号:在"IRQ"标签栏下点选"Avalon_jtag_slave"和 IRQ 的连接点就会为"jtag_uart"核添加一个值为 0 的中断号。

指定 NIos II 的复位和异常地址:从"System Contents"标签栏

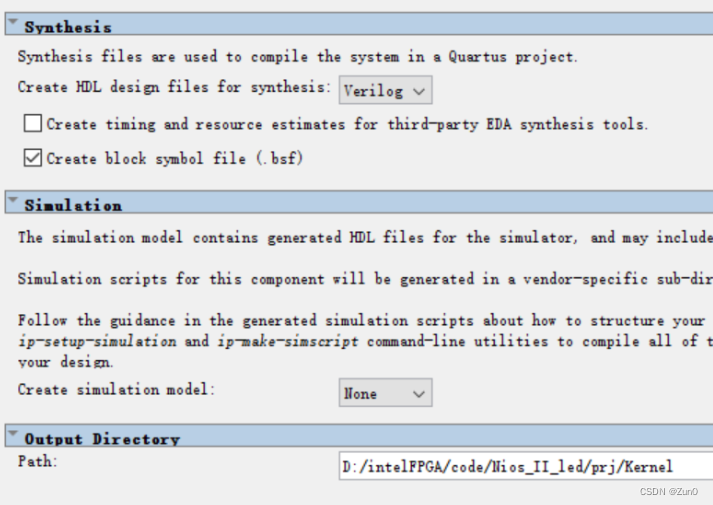

双击建立好的 cpu 进入 Nios II Processor 的配置界面,配置 Reset Vector 和 Exception Vector 为""onchip_ram.s1",点击 Finish。点击 Qsys 主界面菜单栏中的"System"下的"Create Global Reset Network"。完成后会自动连接所有复位端口。生成HDL

3.Quartus设计

3.1 添加原理图文件

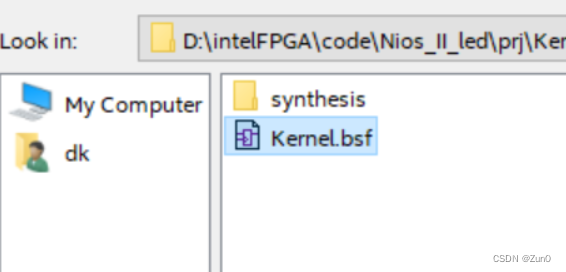

返回到Quartus页面,新建原理图文件:双击空白处,加入生成的bsf文件:

右键生成IO端口

3.2芯片引脚设置

(1)菜单里选择 Assignments-device,然后点击 Device pin options。

(2)进行 unused pin 设置,可能会收到外部信号的干扰,将未用引脚设置为 As input tri-stated。

在这里插入图片描述

3.3编译

回到 Quartus II 主界面后编译项目。如下图所示,编译成功后,点击 OK 完成。

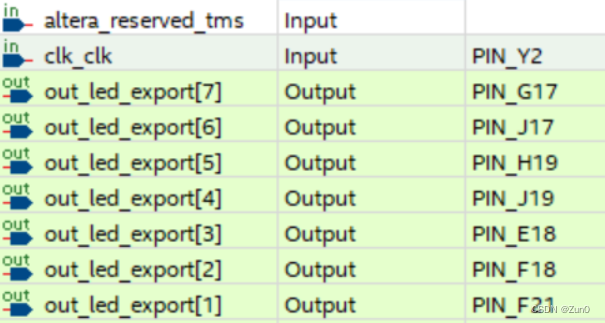

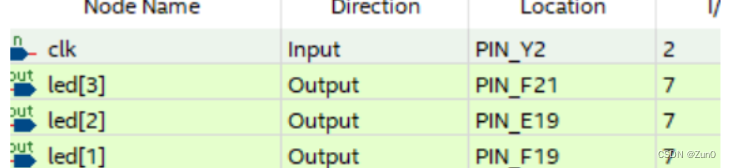

点击下图所指快捷键进入 Pin Planner 界面,按照开发板提供的管脚名称分配针脚,下图所示:

4.软件部分设计

4.1.启动 Nios II SBT

tool->Nios II Software Build Tools for Eclipse

出现 Nios II SBT for Eclipse 主界面

4.2创建工程

建立新工程

在"SOPC Information File name"窗口中选择 kernel.sopcinfo 文件,以便将生成硬件配置信息和软件应用关联,CPU 栏会自动选择"CPU

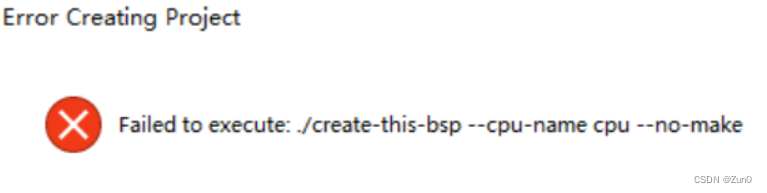

会弹出问题,点击finish出现问题

回到Platform Designer,将on-chip ram的指令线也连上

4.3修改程序

在 hell_word.c 里修改流水灯控制程序。

#include "system.h"

#include "altera_avalon_pio_regs.h"

#include "alt_types.h"

const alt_u8

led_data[8]={0x01,0x03,0x07,0x0F,0x1F,0x3F,0x7F,0xFF};

int main (void)

{

int count=0;

alt_u8 led;

volatile int i;

while (1)

{ if (count==7)

{count=0;}

else

{count++;}

led=led_data[count];

IOWR_ALTERA_AVALON_PIO_DATA(PIO_LED_BASE, led);

i = 0;

while (i<500000)

i++;

}

return 0;

}

编译工程

右键单击项目名称,在弹出的菜单中选择 Build Project

5.运行项目

启动 Quartus Prime Programmer并将sof文件烧录到板子

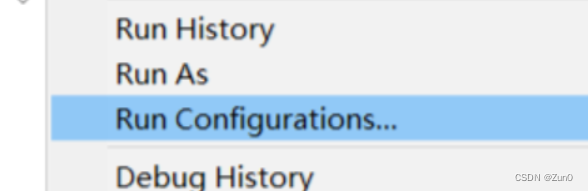

运行/调式程序

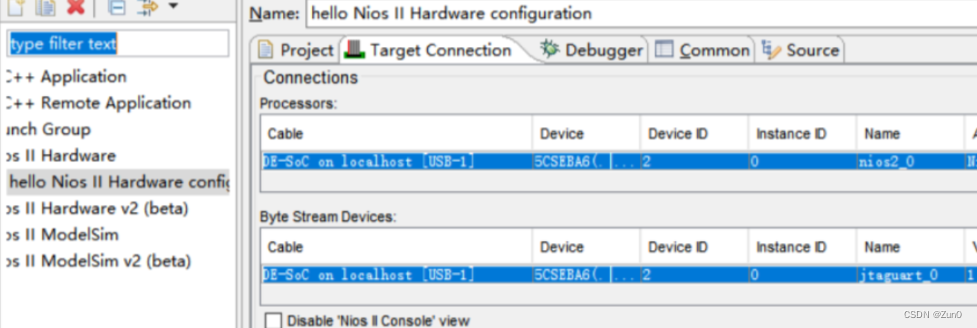

配置 Run Configurations,转到"Target Connection"标签栏,点击右侧的 Refresh Connections 将 USB-Blaster

加入Apply 后,Run。下载完成后,可以看见 Console 里打印信息"hello from Nios

"(第一段代码实现)流水灯实现:

IMG_4385

基于Verilog实现流水灯

1.Verilog代码撰写

module led #(parameter TIME_1_5s=75_000_000)(

input clk,

input rst_n,

output reg [3:0] led

);

//parameter TIME_1_5s=75_000_000;

reg [2:0] cnt;

reg [26:0] cnt_1;

wire add_cnt1;

wire end_cnt1;

wire add_cnt;

wire end_cnt;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_1<=27'b0;

end

else if(add_cnt1)begin

if(end_cnt1)begin

cnt_1<=1'b0;

end

else begin

cnt_1<=cnt_1+1'b1;

end

end

else begin

cnt_1<=cnt_1;

end

end

assign add_cnt1=1'b1;

assign end_cnt1=add_cnt1&&cnt_1 ==TIME_1_5s-1;

// always @(posedge clk or negedge rst_n)begin

// if(!rst_n)begin

// led<=4'b0001;

// end

// else if(end_cnt1)begin

// led<={led[2:0],led[3]};

// end

// else begin

// led<=led;

// end

// end

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt<=1'b0;

end

else if(add_cnt)begin

if(end_cnt)begin

cnt<=1'b0;

end

else begin

cnt<=cnt+1'b1;

end

end

else begin

cnt<=cnt;

end

end

assign add_cnt=end_cnt1;

assign end_cnt=add_cnt&&cnt==7;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

led<=4'b1111;

end

else begin

if(cnt==3'b000)begin

led<=4'b0001;

end

else if(cnt==3'b001)begin

led<=4'b0011;

end

else if(cnt==3'b010)begin

led<=4'b0111;

end

else if(cnt==3'b011)begin

led<=4'b1111;

end

else if(cnt==3'b100)begin

led<=4'b1110;

end

else if(cnt==3'b101)begin

led<=4'b1100;

end

else if(cnt==3'b110)begin

led<=4'b1000;

end

else if(cnt==3'b111)begin

led<=4'b0000;

end

else begin

led<=4'b1111;

end

end

end

endmodule

2.引脚绑定

3.烧录,运行

基于Nios-II实现流水灯的实验总结和心得

在基于Nios-II实现流水灯的实验的总结和心得。

实验准备阶段

在开始实验之前,我深入研究了Nios-II软核处理器的原理、特点和应用方法。我了解到Nios-II是Intel FPGA上的一种嵌入式处理器,具有高性能、可定制性强等优点。同时,我也熟悉了Quartus II、Platform Designer和Nios II SBT for Eclipse等开发工具的使用方法。

硬件设计

在硬件设计阶段,我使用Platform Designer工具在FPGA上搭建了一个包含Nios-II处理器、PIO(并行输入/输出)接口等组件的嵌入式系统。我选择了适当的FPGA芯片,并设置了合适的时钟频率。然后,我添加了必要的组件,并进行了相应的配置和连接。特别地,我通过PIO接口连接了8个LED灯,并配置了相应的输出端口。

软件设计

在软件设计阶段,我使用Nios II SBT for Eclipse工具创建了一个Nios II工程,并编写了C/C++代码以控制LED灯的闪烁。我通过PIO接口读取和写入数据,实现了对LED灯的亮灭状态的控制。为了实现流水灯效果,我采用了延时函数和循环语句相结合的方式。我调整了延时函数的时间参数,以控制LED灯闪烁的速度和顺序。

实验结果

将配置文件(.sof)和可执行文件(.elf)下载到FPGA后,我成功观察到了流水灯效果。LED灯按照预设的顺序依次亮起和熄灭,形成了循环变化的效果。这让我感到非常兴奋和满足,因为我不仅实现了预期的功能,还学到了很多实用的知识和技能。

三、实验心得与体会

深入理解嵌入式系统设计

通过这次实验,我深刻理解了嵌入式系统设计的复杂性和挑战性。在设计过程中,我需要考虑硬件和软件之间的协同工作、资源的合理分配以及性能的优化等方面的问题。这些经验对于我将来的学习和工作都非常重要。

掌握FPGA开发技术

通过这次实验,我掌握了FPGA开发技术的基本流程和工具使用方法。我了解了FPGA的工作原理、设计方法和优化技巧等方面的知识。这些技术对于我在未来的电子工程和嵌入式系统设计领域的发展具有重要意义。

提升实践能力和解决问题的能力

在实验过程中,我遇到了很多问题和挑战。但是通过不断地尝试、调试和修改代码,我最终成功地实现了流水灯效果。这个过程让我深刻体会到了实践能力和解决问题能力的重要性。我相信这些能力将对我未来的学习和工作产生积极的影响。

激发对电子工程的热爱

通过这次实验,我感受到了电子工程的魅力和乐趣。我喜欢通过编程和硬件设计来实现各种有趣的功能和效果。这种创造性和挑战性的工作让我感到非常兴奋和满足。我相信这种热爱将激励我在未来的学习和工作中更加努力和专注。