DDR4 SDRAM(Double-Data-Rate Fourth Generation Synchronous Dynamic Random Access Memory,简称为 DDR4 SDRAM),是一种高速动态随机存取存储器,它属于 SDRAM 家族的存储器产品,提供了相较于 DDR3 SDRAM 更高的运行性能与更低的电压,并被广泛的应用于计算机的运行缓存。

1 DDR4 介绍

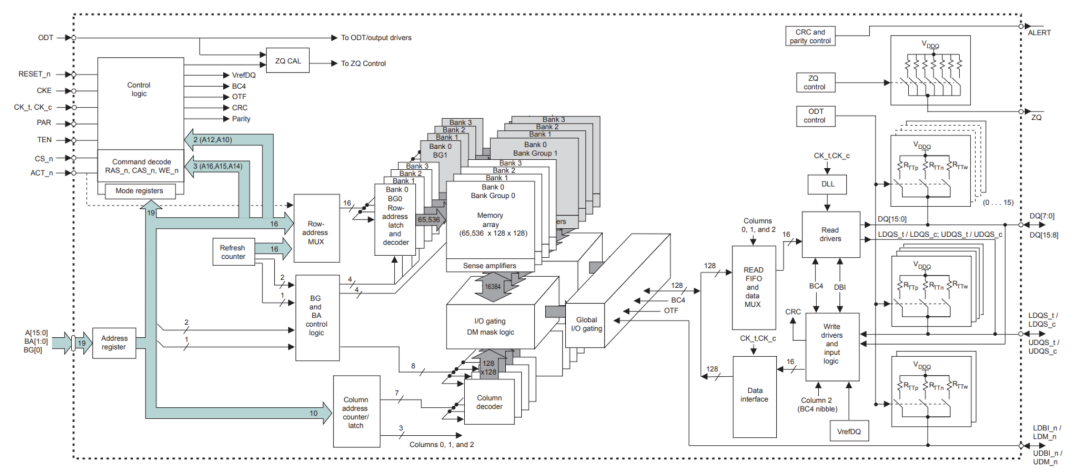

DDR4 芯片的行地址是 16bit 位宽,列地址是 10bit 位宽,而整个存储区域分为两个 BANK 组,每个 BANK 组又由 4 个子 BANK 组成,所以整片 DDR4 的容量就是2^16*2^10*8*16bit=512M*16bit。DDR4 相较于 DDR3 在指令引脚上也发生了变化,DDR4 取消了我们所熟悉的使能 WE、列激活 CAS 和行激活 RAS 这三个命令引脚,而是将这三个命令引脚和地址线 A14、A15 以及 A16 复用了。除此之外在寻址的时候也不再是直接去寻址 BANK,而是先寻址 BANK 组,然后再找到这个 BANK 组中的某个子 BANK。整个数据的吞吐是 8 倍预取,因此用户端数据在读写的时候就是16bit*8=128bit 的数据量进行吞吐(注意虽然是 8 倍预取,但是每一次 IO 引脚上的数据传输依旧是 16bit,因为数据线就 16 根,至于为何可以达到 8 倍预取和 DDR4 内部的双沿采样,FIFO 缓冲,写数据逻辑结构有关)。

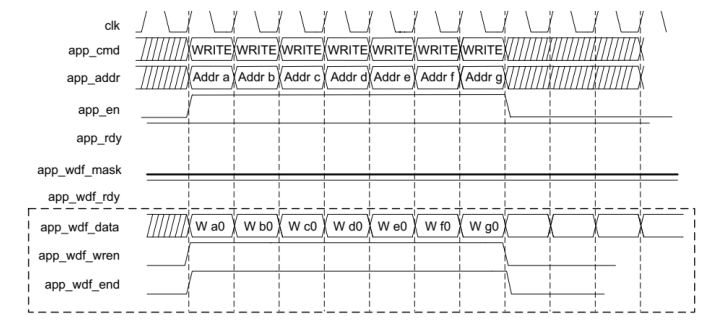

2 MIG IP介绍

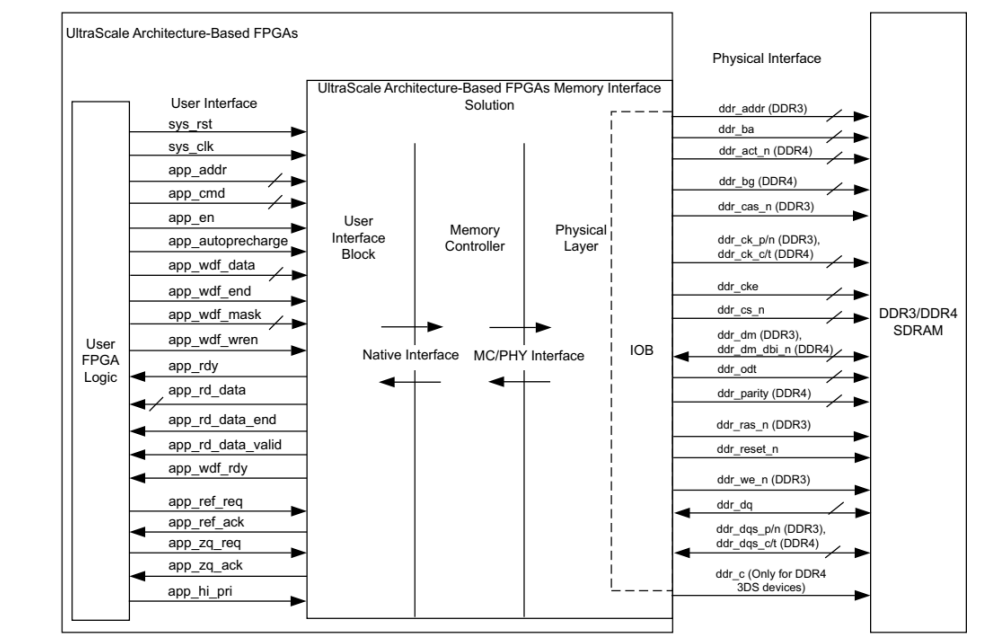

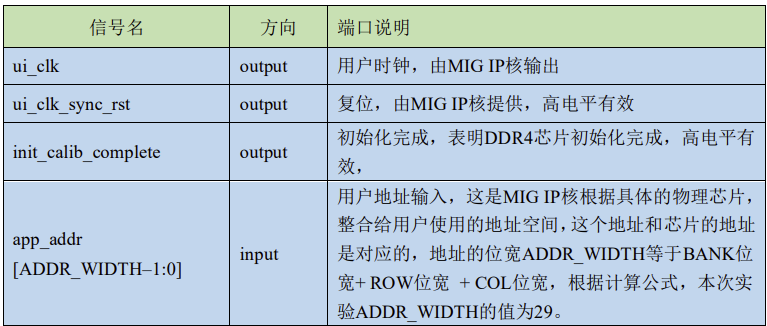

MIG IP 核是 Xilinx 公司针对 DDR 存储器开发的 IP,里面集成存储器控制模块,实现 DDR 读写操作的控制流程,下图是 MIG IP 核结构框图。MIG IP 核对外分出了两组接口,左侧是用户接口,就是用户(FPGA)同 MIG 交互的接口,用户只有充分掌握了这些接口才能操作 MIG;右侧为 DDR 物理芯片接口,负责产生具体的操作时序,并直接操作芯片管脚,这一侧用户只负责分配正确的管脚,其他不用关心。

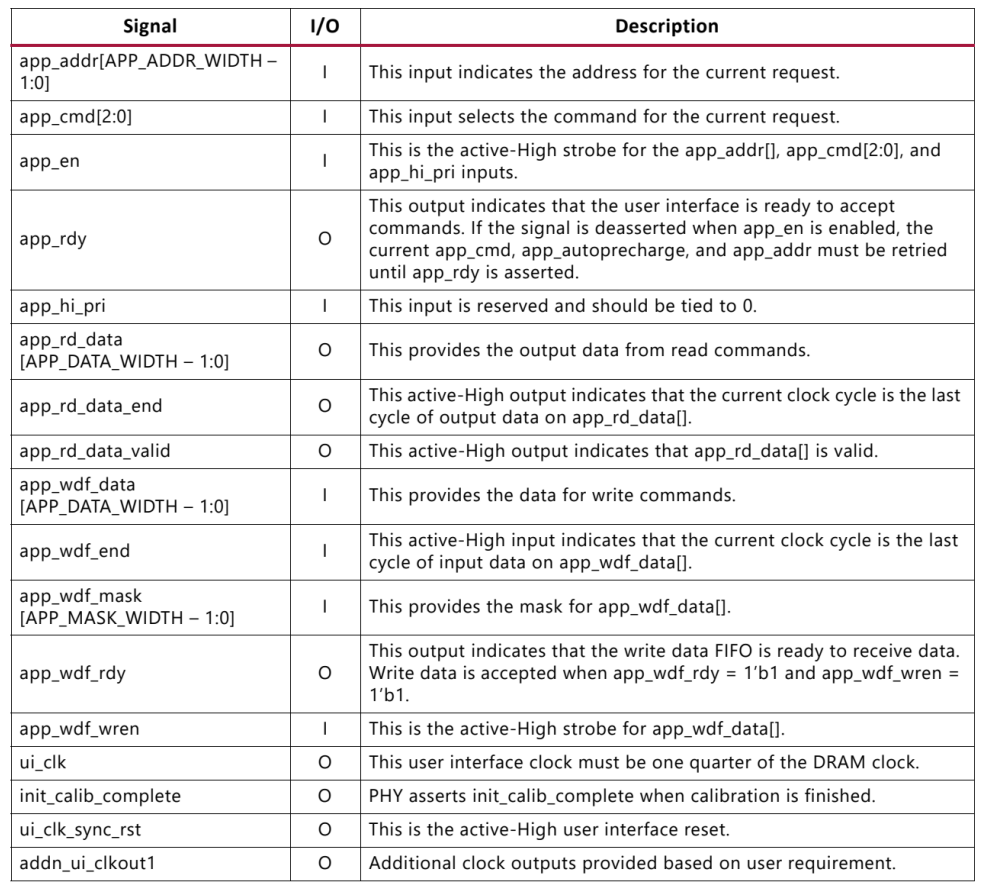

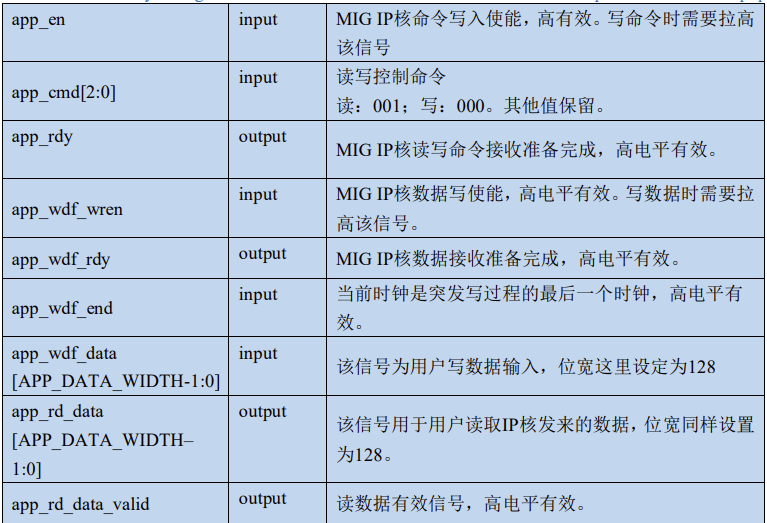

DDR4 的读或者写都包含写命令操作,其中写操作命令(app_cmd)的值等于 0,读操作 app_cmd 的值等于 1。首先来看写命令时序,如下图所示。首先检查 app_rdy,为高则表明此时 IP 核命令接收处于准备好状态,可以接收用户命令,在当前时钟拉高 app_en,同时发送命令(app_cmd)和地址(app_addr),此时命令和地址被写入。

写数据的时序

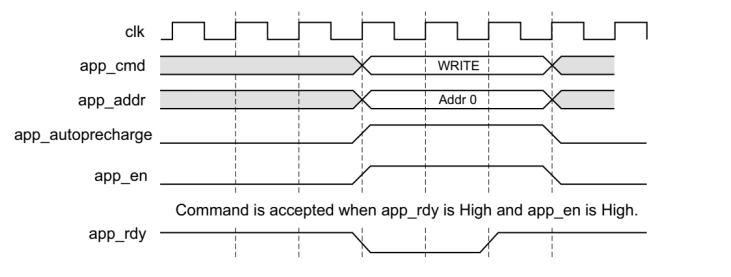

写数据有三种情形均可以正确写入:

(1)写数据时序和写命令时序发生在同一拍;

(2)写数据时序比写命令时序提前一拍;

(3)写数据时序比写命令时序至多延迟晚两拍;

写时序总结如下:首先需要检查 app_wdf_rdy,该信号为高表明此时 IP 核数据接收处于准备完成状态,可以接收用户发过来的数据,在当前时钟拉高写使能(app_wdf_wren),给出写数据(app_wdf_data)。这样加上发起的写命令操作就可以成功向 IP 核写数据。这里有一个信号 app_wdf_mask,它是用来屏蔽写入数据的,该信号为高则屏蔽相应的字节,该信号为 0 默认不屏蔽任何字节。

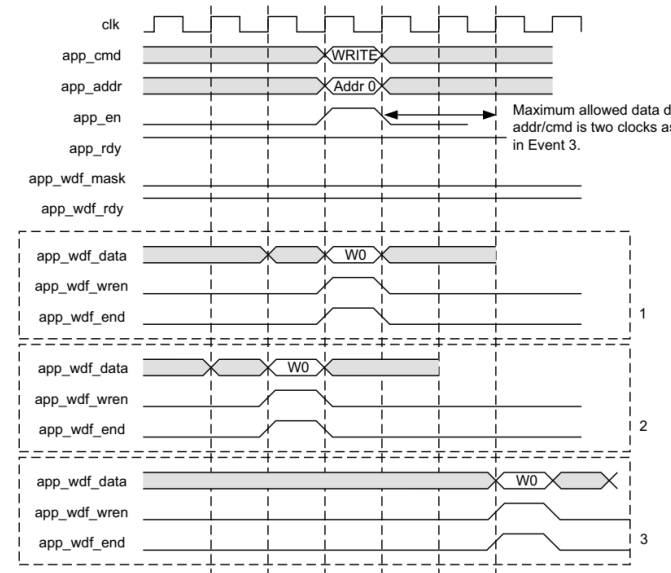

对于背靠背写,其实也有三种情形,唯一点不同的是,它没有最大延迟限制。

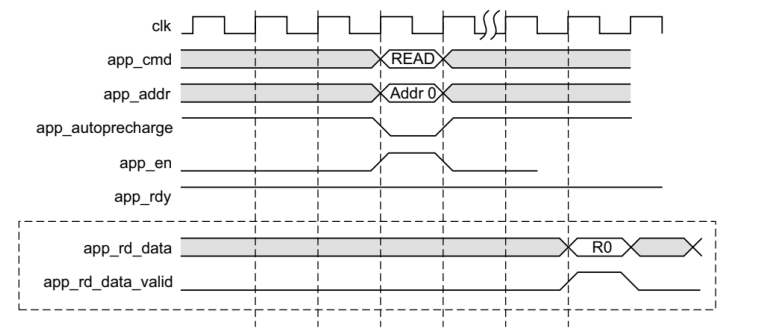

接着来看读数据

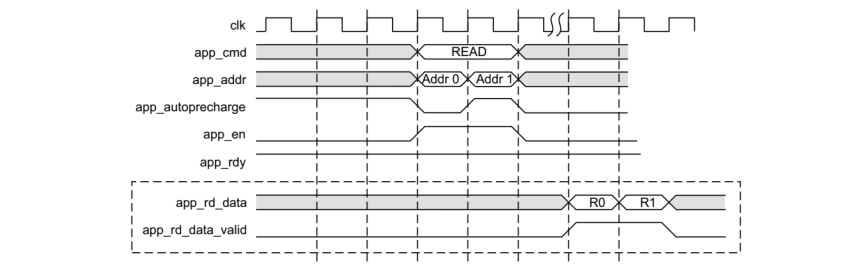

读时序比较简单,发出读命令后,用户只需等待数据有效信号(app_rd_data_valid)拉高,为高表明此时数据总线上的数据是有效的返回数据。需要注意的是,在发出读命令后,有效读数据要晚若干周期才出现在数据总线上。下面是背靠背读的情况。

需要注意的是,在连续读的时候,读到的数据顺序跟请求的命令/地址是相对应的。通常使用 DDR4 的时候,为了最大限度地提高 DDR4 效能,充分利用突发写的特点,非背靠背很少用,而更多地采用背靠背操作。