**引言:**本文开始学习第二章内容,本文重点介绍FPGA、Zynq和Zynq MPSoC器件技术演进以及Zynq和Zynq MPSoC器件的基本结构和特点。

第二章 FPGA、Zynq和Zynq MPSoC (1)

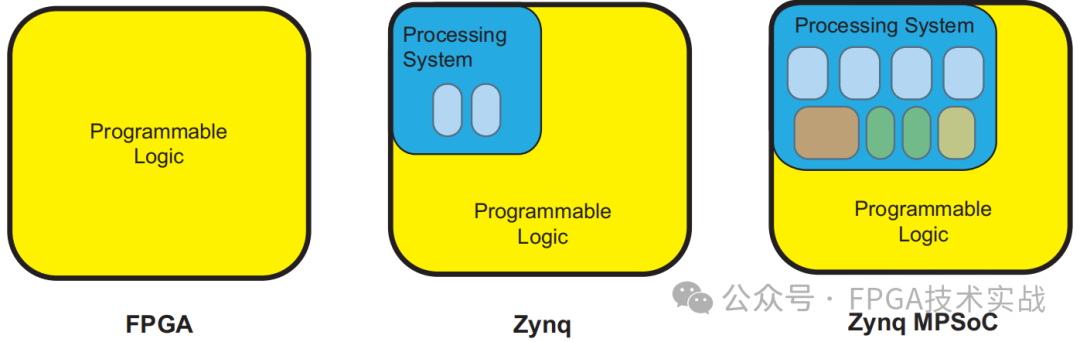

Zynq MPSoC是Xilinx发布的第一款SoC Zynq-7000片上系统(SoC)的演进。这两个器件都包括处理系统(PS)和可编程逻辑(PL),PL等效于现场可编程门阵列(FPGA)。如图1所示,它在高层次上比较了三种类型器件,Zynq MPSoC中的PS比Zynq中的PS更大、更复杂。

在本章中,将回顾这三种设备类型的特点,并强调它们之间的异同。我们还提出了一些潜在演进的原因。

图1:FPGA、Zynq和Zynq MPSoC的高层次比较

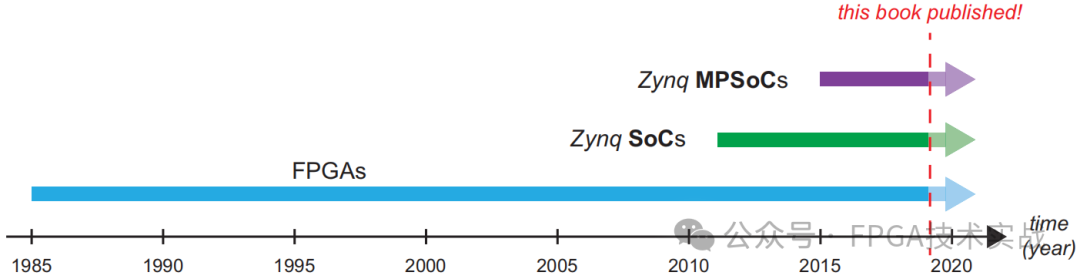

1. 技术演进时间表

Zynq、Zynq MPSoC和FPGA都是当前的技术,并且相互补充。"最佳"选择取决于正在创建的设计的特性。所有三种器件类别都有自己独特的功能平衡,这使得它们中的每一种都特别适合一系列不同的任务和应用程序。

图2:FPGA、Zynq和Zynq MPSoC演进时间表

这本书的许多读者可能都熟悉Zynq,所以我们从那里开始复习,可以将其与较新的Zynq MPSoC器件进行比较。FPGA是两个SoC的PL部分的基础,将在本章后面介绍。

2. Zynq-7000 SoC

Zynq-7000 SoC是Xilinx发布的第一款SoC设备,将基于FPGA的PL与基于Arm的PS相结合。在本节中,我们将简要介绍Zynq的架构和功能,读者可以参考我们上一本书中的详细内容[1]。

2.1 Zynq的结构和特点

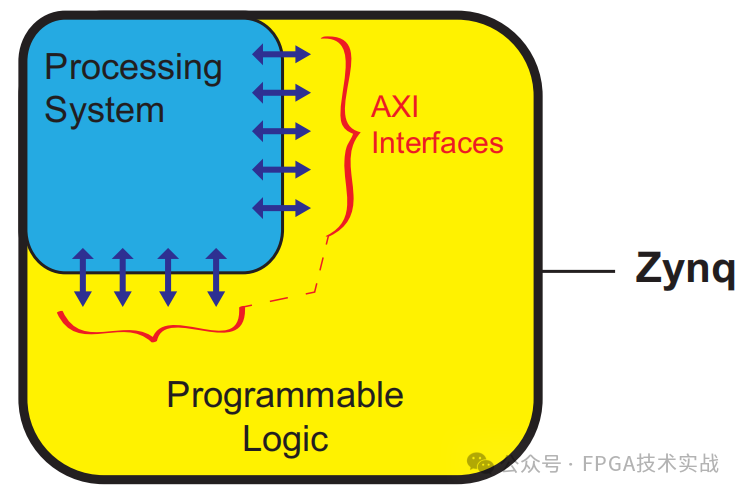

为了提供架构的高层次概述,Zynq架构有两个部分:PS和PL,它们之间有一组互连,如图3所示。这些互连基于先进可扩展接口(AXI)标准,这是Arm开发的片上通信标准。

图3:Zynq SoC设备的高级框图(来自"Zynq Book"[3])

将PS处理系统组件与PL耦合是运行嵌入式系统软件的基础要求,特别是操作系统和软件应用程序,需提供专用的优化资源,同时保留FPGA逻辑的所有优点(特别是其强大的并行性和可重配置性)。AXI接口形成了两个部分之间的连接。AXI是针对SoC应用程序进行优化的标准。

图3中PS和PL的相对尺寸未按比例绘制,事实上,Zynq系列中有几个器件,每个器件都具有相同的PS架构和不同大小的PL。

稍后将更详细介绍Zynq架构和Zynq MPSoC器件之间PS和PL架构的差异。

2.1.1 Zynq处理系统 (PS)

Zynq PS部分,如图3中的蓝色部分所示,包括一个应用级处理器和其他组件。这些概述如下(有关详细信息,请参见[3])。

++•应用处理器单元(APU):++该单元包括双核Arm Cortex-A9处理器以及256KB的片上高速缓存。

++•互连和存储器接口:++它们分别实现PS和PL之间以及与外部存储器之间的通信。

++•I/O外设组:++集成外设接口,涵盖通用标准,如USB、UART、SPI、I2C等。

Zynq中的PS有两个处理核,设计者可以选择将两个核心用于同一操作系统,或者在每个操作系统上使用不同的操作系统。稍后,我们将Zynq PS与Zynq MPSoC架构的PS进行比较,并注意到新器件中功能的扩展,特别是,Zynq MPSoC最多有六个处理核心!

2.1.2 Zynq可编程逻辑(PL)

Zynq的PL部分基于Artix-7 FPGA结构(适用于该系列中较小的器件)或Kintex-7 FPGA架构(适用于较大的器件)。这两个变体代表Xilinx 7系列FPGA的成员,其中还包括更高性能的Virtex-7。

与等效的FPGA一样,Zynq PL包括DSP48 Slice切片(用于高速算术的资源)、块RAM、高速收发器、集成通信块以及通用逻辑。在本章的后面,第2.4.3节提供了现代FPGA关于这些资源的更多信息。

2.1.3 PS和PL之间的接口

Zynq的两个区域之间有九个接口。其中四个互连被指定为"通用"接口,四个互连为"高性能"接口,其余互连为"加速器一致性端口"(ACP),它提供了应用程序处理单元(APU,位于PS内)和PL之间的直接路由。

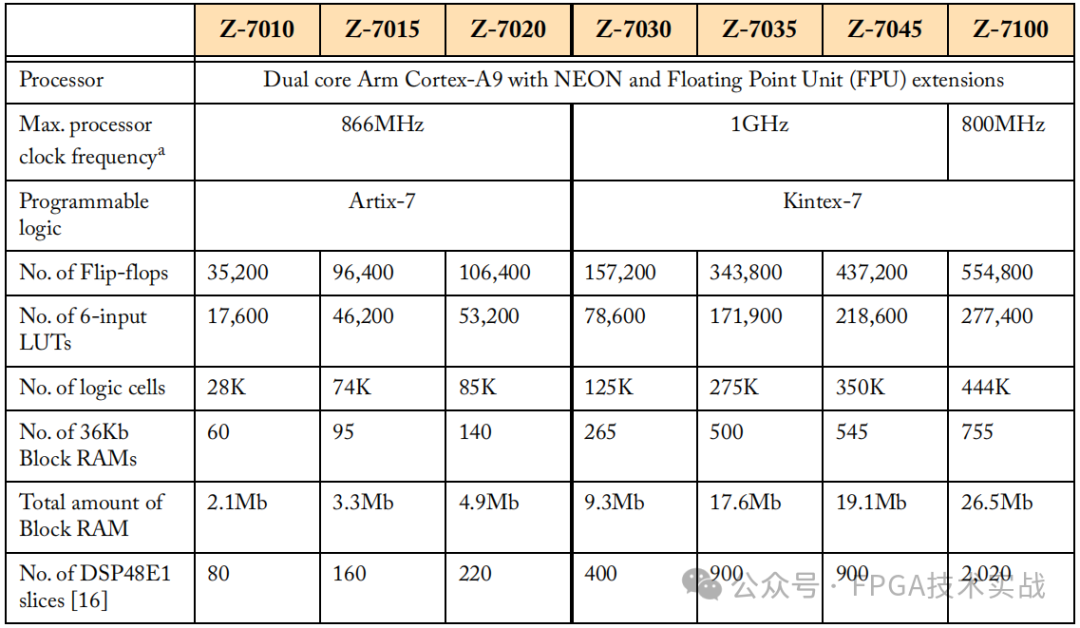

2.2 Zynq器件

为了对Zynq-7000系列中的器件进行简要比较,请考虑表1,该表汇总了每个芯片的关键特性和参数(请注意,单核Zynq-700S系列不包括在表中)。

表1:Zynq-7000 SoC系列家族器件的比较

a.支持的最大处理器时钟频率取决于器件速度等级。

所有Zynq-7000芯片的PS都是相同的,唯一的区别是支持的最大时钟频率。PL在整个系列中都是相似的,低端器件采用基于Artix-7的逻辑,其余器件采用Kintex-7中的逻辑。专业资源(如DSP片、块RAM存储器和输入/输出资源)的PL尺寸和数量也各不相同。

2.3 Zynq使用模式

设计者以前使用过FPGA,或者使用过处理器,或者两者兼而有之都可以采用Zynq。Zynq在推出时的卖点是提供一种解决方案,用于在单个器件上实现基于处理器的任务,如运行软件和操作系统,以及基于FPGA的处理,并具有高端性能和两个组件之间的高容量互连。如果以前只使用FPGA,那么添加专用硬处理器可以提高性能(与由通用PL资源构建的"软"处理器相比);而另一方面,如果以前单独使用处理器,FPGA逻辑的存在使某些任务能够在硬件中实现,从而提供加速并释放处理器用于其他任务。

以前需要专用处理器和FPGA的系统可以从两个物理器件减少到一个,从而节省了接口工作量、功耗、材料清单成本等。

这些考虑因素在[3]中进一步讨论,特别是Zynq-7000。然而,我们发现类似的因素促使Zynq MPSoC的使用。如接下来所述,Zynq MPSoC提供了处理单元的进一步集成,扩展了Zynq的PS部分,包括实时处理引擎、图形处理器和视频编解码器(某些器件具备),以及功能更强大的应用处理器。

3. Xilinx Zynq MPSoC

与Zynq相比,Zynq MPSoC代表了架构的扩展和扩展。尽管由相同的高级组件(PS和PL,使用AXI互连接口)组成,但PS更为复杂,PL从Xilinx的7系列升级为UltraScale+ FPGA架构。在大多数Zynq MPSoC系列中,PL的尺寸也比Zynq系列器件大。

3.1 Zynq MPSoC的发布

Zynq MPSoC于2015年首次发布,距离Zynq首次发布已有四年时间。在这段时间里,Zynq在各种应用领域得到了广泛应用,通过这一点,对完全集成的"FPGA+处理器"解决方案的需求已经根深蒂固。

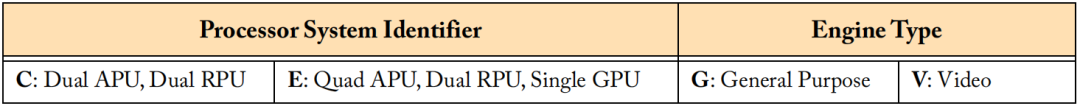

Zynq MPSoC提供了增强型PS和更大的PL(有多种不同尺寸可供选择)。Zynq MPSoC系列已经建立了子家族,以满足不同类型的应用及其需求,特别是在PS资源方面。这些子家族通过两个字母的名称来区分:CG、EG和EV,其中两个字符的含义如表2所示。

表2:Zynq MPSoC子族标识符

Zynq MPSoC并没有取代Zynq,而是提供了一种类似形式的扩展和增强解决方案。Zynq器件将继续是低成本、低复杂系统的合适选择。

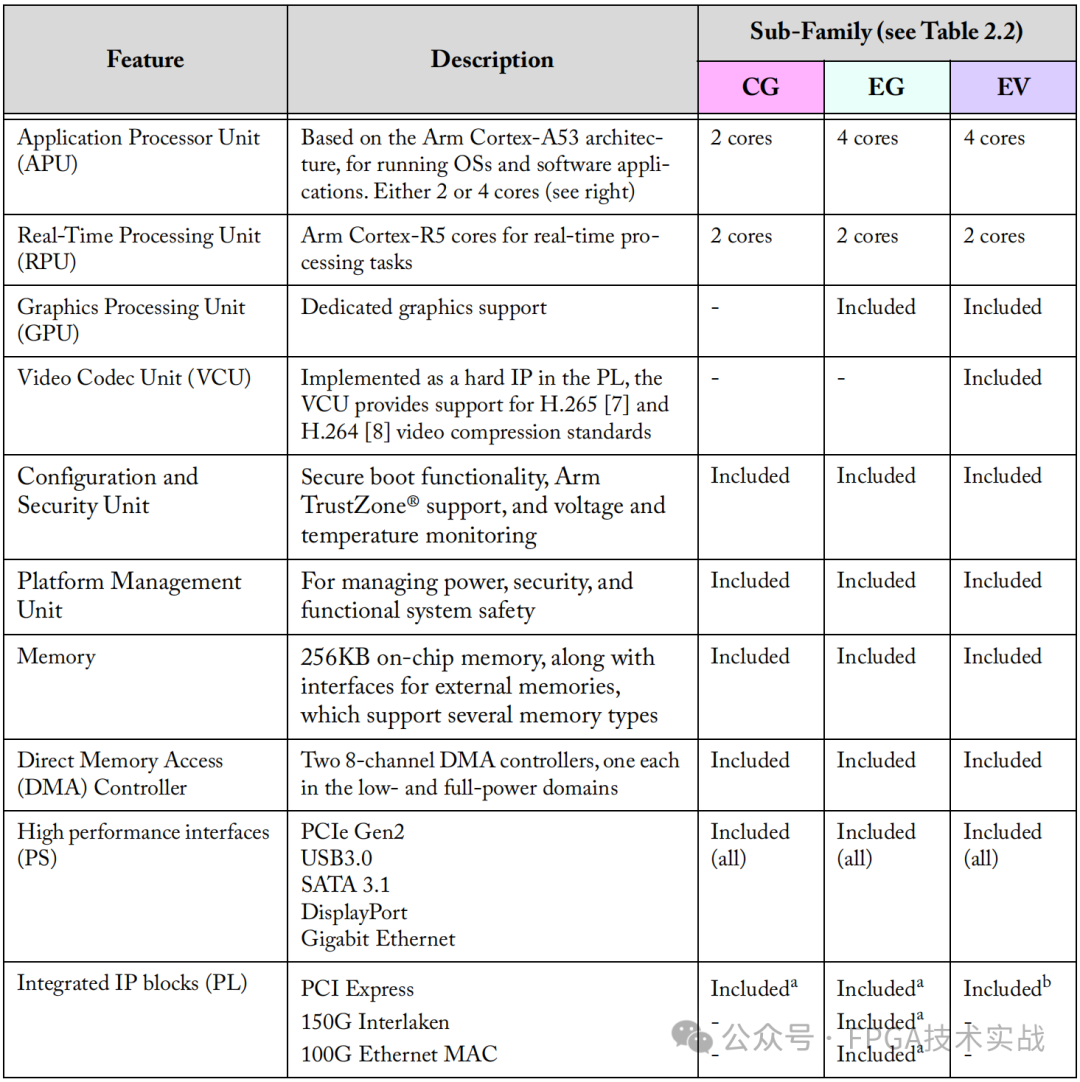

3.2 Zynq MPSoC体系结构和特点

与Zynq相比,Zynq MPSoC包括一组扩展的资源,有三种变体(即CG、EG和EV子家族)。PS和PL的主要特征如表2.4所示。在后面章节详细了解体系结构时,我们将详细介绍这些资源的功能。

Zynq MPSoC架构的另一个重要发展是其电源管理功能。器件被划分为四个独立的电源域,可以单独操作。这意味着设备的未使用部分可以在不需要时断电,从而提高整体电源效率。另外,安全功能也得到了增强。

此外,需要强调的是,Zynq MPSoC得益于UltraScale+ FPGA体系结构(将在第4.3节中进行介绍),其中包括对Zynq使用的7系列体系结构的某些改进。两个特别显著的区别特征是包含了UltraRAM,以及将DSP Slices进一步升级为DSP48E2(DSP48E1包含在Zynq中)。

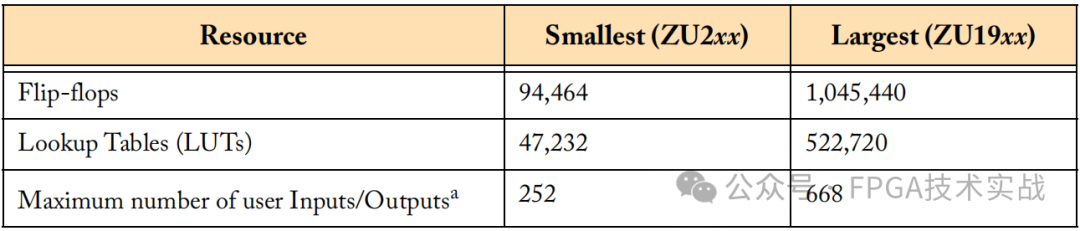

表3中突出显示了资源最小和最大的器件。通过与表1进行比较,请注意,Zynq MPSoC系列包括具有比Zynq系列大得多的PL面积的器件。这使得Zynq MPSoC在需要大量使用PL时成为更好的选择,例如,作为嵌入式系统设计的一部分,用于一组复杂算法的硬件加速。

表3:基本资源比较(最小和最大Zynq MPSoC的PL)

a.不包括高速串行接口。

表4:Zynq MPSoC的特性概述(按子家族)[24]

各种Zynq MPSoC芯片还包含不同数量的其他PL资源类型(DSP48x Slices、块RAM等)---有关完整信息,请参阅详细的技术手册。