在 FPGA 的神奇世界里,I/O 电平标准就像魔法咒语,掌控着芯片与外界交流的方式。对于初涉 FPGA 领域的小白来说,这些标准可能有点神秘莫测,但别担心,今天我就用最通俗易懂的方式为你揭开它们的面纱。

一、电平标准的魔法世界

1、为什么电平标准如此重要?

想象一下,FPGA 就像一个超级智能的城堡,它需要与外界(各种电子设备)进行信息交换。

而电平标准就是城堡与外界沟通的语言规则。

如果没有统一的电平标准,就好比城堡里的人说一种语言,外面的人说另一种语言,信息就无法准确传递,整个系统就会陷入混乱。

2、数字电路中的电平表示

在数字电路里,我们用电压来代表"0"和"1"这两个数字。

这就像用灯光的亮灭来传递信号一样,只不过这里是用电压的高低。

不同的电平标准规定了不同的电压范围来表示"0"和"1"。

3、常见电平标准的大家族

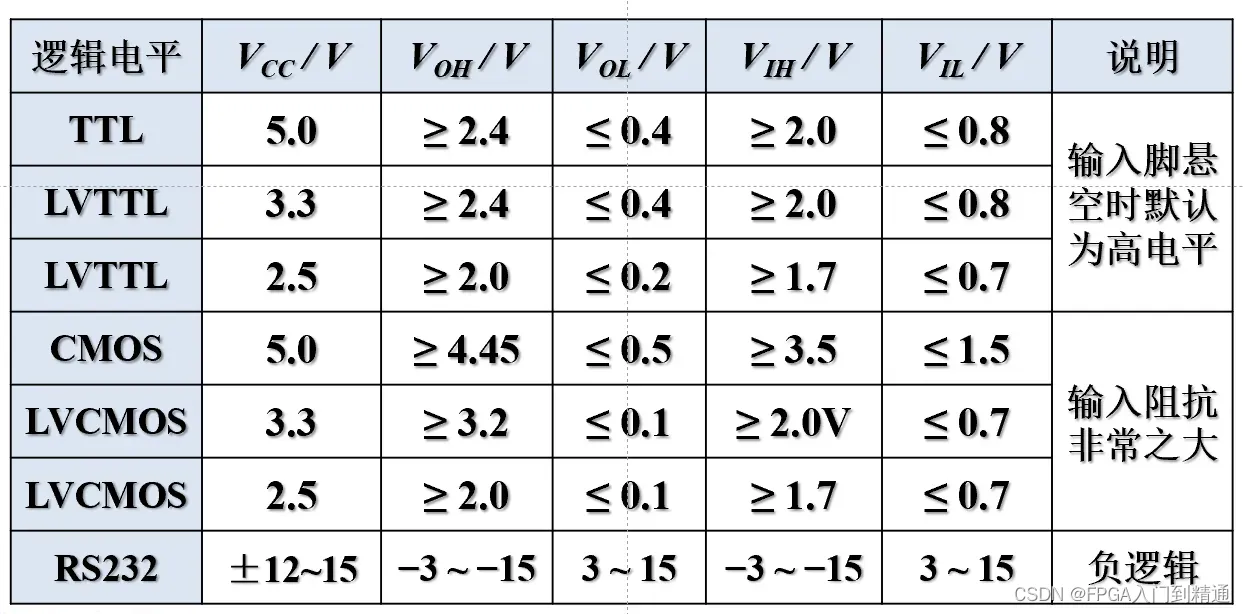

FPGA 常用的电平标准有很多成员,比如 TTL、LVTTL、CMOS、LVCMOS、LVDS 等等。

每个成员都有自己独特的特点和适用场景,接下来我们就一个一个地认识它们。

二、TTL 电平标准的传奇

1、基本特性

TTL(Transistor - Transistor Logic,三极管 - 三极管逻辑电平)可是电平标准家族中的元老级成员。

它的标准电源供给电压是 5V。

在输出端,当电压大于等于 2.4V 时,就代表逻辑"1";小于等于 0.5V 时,就是逻辑"0"。

在输入端,电压大于等于 2.0V 被判定为逻辑"1",小于等于 0.8V 则为逻辑"0"。

2、应用场景与局限

以前,TTL 在很多数字电路中都有广泛应用,尤其是在一些早期的电子设备中。但是,它也有一些小缺点。

比如说,在 2.4V 到 5V 之间的电压空间比较大,这就像给了信号一个比较宽松的"活动范围",但也容易造成一些信号的不稳定性。

而且,5V 的电源电压在现代一些对功耗要求较高的设备中显得有点高了,就像一个大功率的灯泡,比较耗电。

三、LVTTL 电平标准的革新

1、3.3V LVTTL 的特点

为了解决 TTL 的一些问题,LVTTL(Low Voltage Transistor - Transistor Logic,低压 TTL 电平标准)应运而生。

LVTTL3.3V 的电源供给电压降低到了 3.3V,这就像是把灯泡换成了更节能的小功率灯。

输出端,逻辑"1"的电压要求大于等于 2.4V,逻辑"0"小于等于 0.4V;

输入端,逻辑"1"判定大于等于 2.0V,逻辑"0"小于等于 0.8V。

2、2.5V LVTTL 的不同

LVTTL2.5V 则更加"节能",电源供给为 2.5V。

输出端逻辑"1"电压大于等于 2.0V,逻辑"0"小于等于 0.2V;

输入端逻辑"1"大于等于 1.7V,逻辑"0"小于等于 0.7V。

LVTTL 因为电压降低了,所以功耗也相应降低,而且在信号稳定性方面也有一定提升,在很多现代的中低速数字电路中得到了广泛应用。

四、CMOS 与 LVCMOS 电平标准的魅力

1、CMOS 的特性

CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体电平)也是一位重要成员。

它的标准电源供给同样是 5V。

输出端,逻辑"1"要求电压大于等于 4.45V,逻辑"0"小于等于 0.5V;

输入端,逻辑"1"判定大于等于 3.5V,逻辑"0"小于等于 1.5V。

CMOS 的优点是功耗比较低,就像一个智能的电源管理器,能根据电路的工作状态自动调整功耗。

2、LVCMOS 的优势与应用

LVCMOS(Low Voltage Complementary Metal Oxide Semiconductor,低压 CMOS 电平标准)则在 CMOS 的基础上进一步优化。

LVCMOS3.3V,电源供给 3.3V,输出端逻辑"1"大于等于 3.2V,逻辑"0"小于等于 0.4V;输入端逻辑"1"大于等于 2.0V,逻辑"0"小于等于 0.7V。

LVCMOS2.5V ,电源供给 2.5V,输出端逻辑"1"大于等于 2.0V,逻辑"0"小于等于 0.4V;输入端逻辑"1"大于等于 1.7V,逻辑"0"小于等于 0.7V。

LVCMOS 家族在现代的低功耗、中低速数字电路中非常受欢迎,像一些便携式设备、小型智能硬件等都经常能看到它们的身影。

五、LVDS 电平标准的独特之处

1、高速低功耗的特性

LVDS(Low Voltage Differential Signaling,低压差分信号)可是个"速度达人"。

它的电压摆幅非常小,只有 350mV 左右,电流也只有 3.5mA 左右。

这就像一个轻巧敏捷的运动员,能够以超快的速度传输数据,而且功耗还超低。

它采用差分信号传输方式,就像两个人一起传递信息,一个人说正的,一个人说反的,接收方通过比较两人的话来确定信息内容,这样可以大大提高抗干扰能力。

2、广泛的应用领域

因为 LVDS 的这些优点,它在很多高速数据传输的场景中得到了广泛应用,比如高清视频传输、高速通信接口等。

在高清视频监控系统中,摄像头采集到的海量视频数据需要快速、准确地传输到后端处理设备,LVDS 就能完美胜任这个任务。

六、注意事项

在实际使用 FPGA 的 I/O 电平标准时,我们需要注意以下几点:

1、根据需求选择合适标准

首先要仔细分析你的设计需求,看看需要连接的外部设备支持哪种电平标准,然后在 FPGA 中选择与之匹配的电平标准,这样才能确保信息的准确传递。

2、查阅芯片手册

不同的 FPGA 芯片对电平标准的支持情况可能会有所不同,所以一定要认真查阅相关芯片手册,了解芯片的具体能力和限制。

3、关注高速信号传输要求

如果涉及到高速信号传输,像使用 LVDS 等电平标准时,要特别注意信号完整性。

这包括合理的布线、阻抗匹配等,就像为高速跑车修建一条平坦、宽阔且没有干扰的赛道,这样才能让信号快速、稳定地传输。

4、重视电平标准兼容性

在一个复杂的系统中,可能会有多种不同电平标准的设备相互连接,这时候就需要考虑电平标准之间的兼容性。

可以通过电平转换芯片等方式,让不同"语言"的设备能够顺利沟通。

如果需要更多学习资料和源码,想要学习FPGA实战入门进阶,请阅读下面这篇文章: