由于需要进行一些FPGA的简单开发,但板载PL端没有焊接晶振,所以需要从PS端借用时钟到PL端使用。

首先新建项目,根据自己的板载选择芯片,我的板载芯片是zynq_7010。

一路next,在自己的vivado的工作文档新建文件夹并给自己新建的项目命名,随后进行芯片选型,由于我的板载芯片是zynq_7010,所以做如下选择。确认无误后点击finish即可。

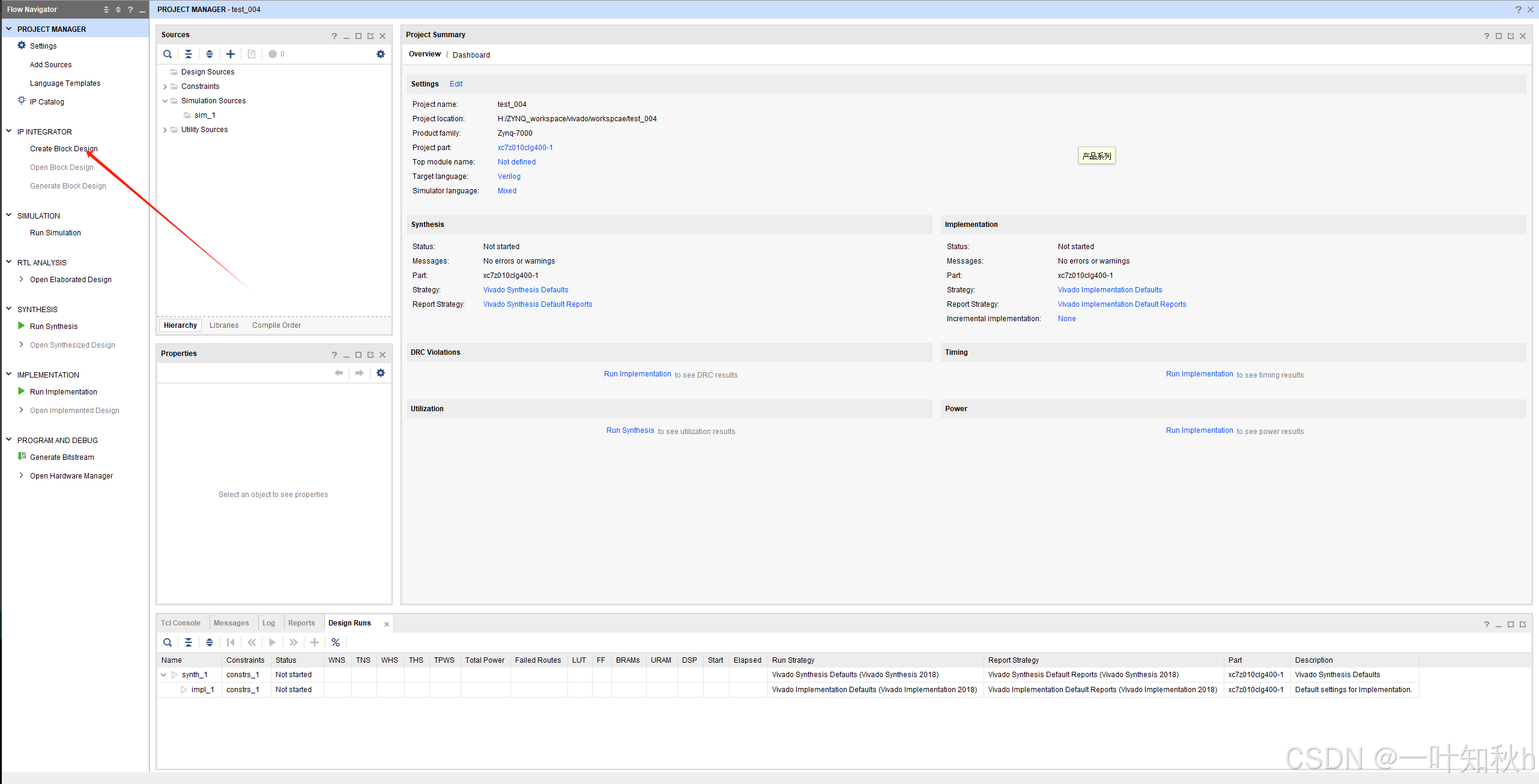

下面是创建好新工程的主界面,点击创建block_design

下面是创建好新工程的主界面,点击创建block_design

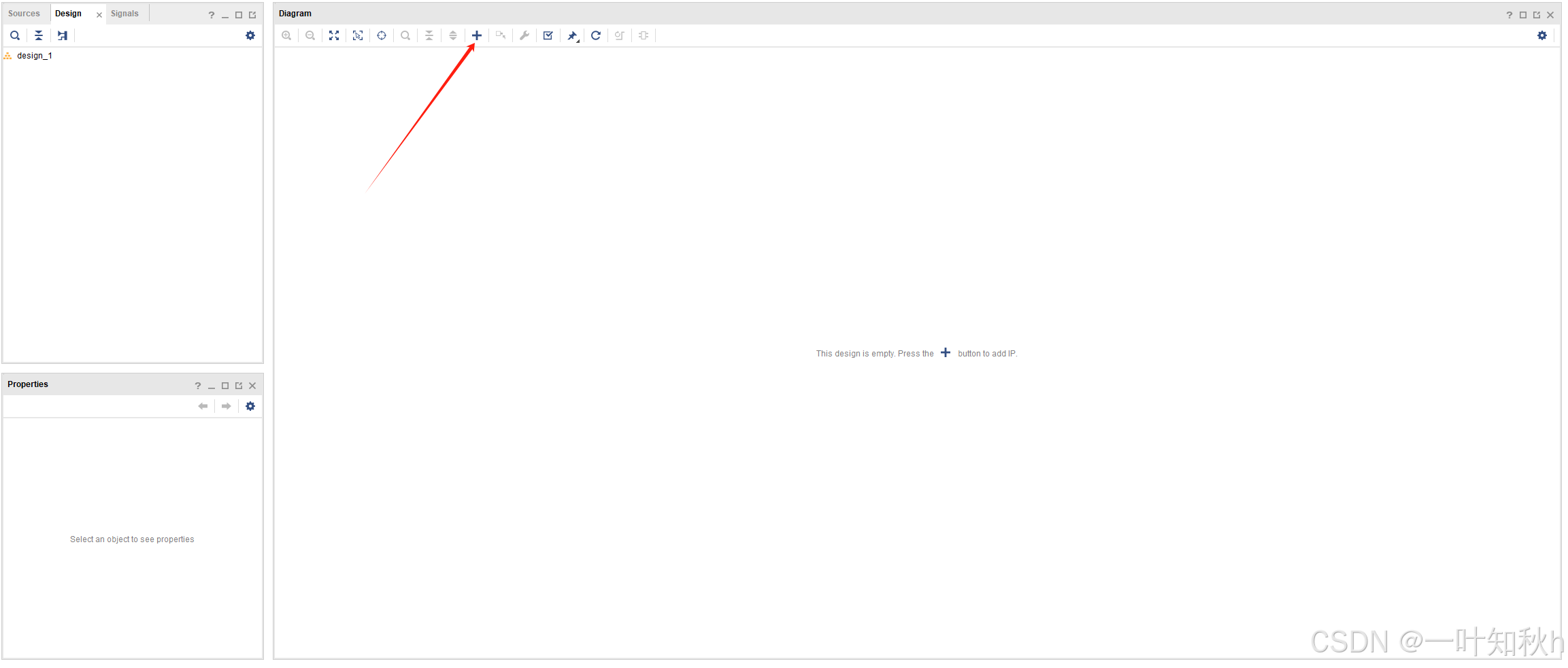

根据自己需要是否修改设计名字,不改也可。点击OK后进入如下界面,点击"+",在左上角搜索ZYNQ并选择唯一对应的Precessing System。

根据自己需要是否修改设计名字,不改也可。点击OK后进入如下界面,点击"+",在左上角搜索ZYNQ并选择唯一对应的Precessing System。

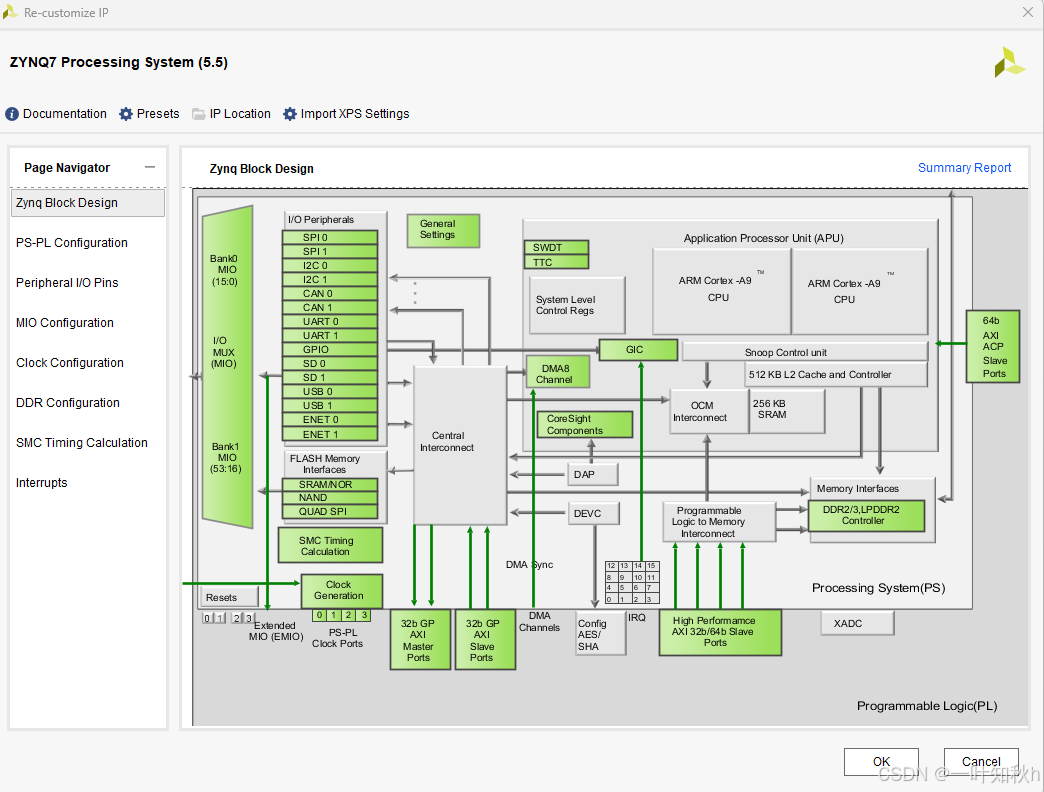

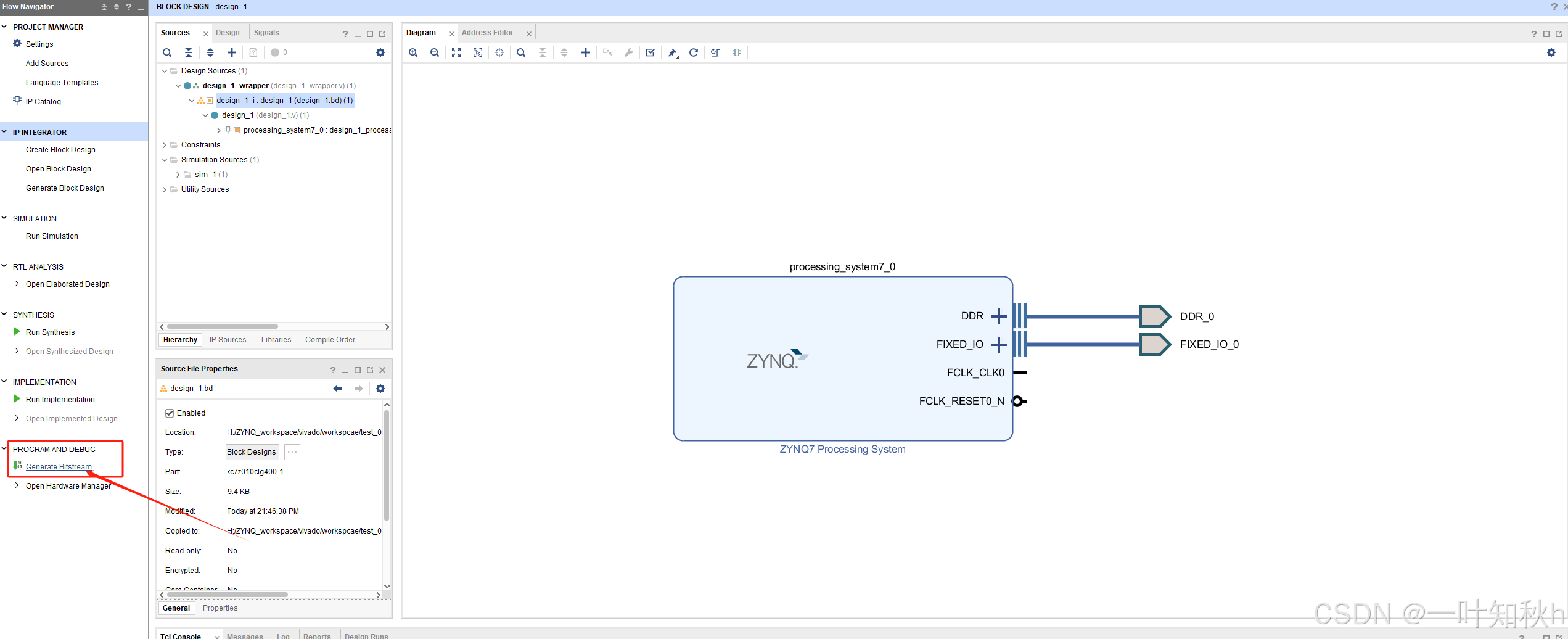

随后出现对应Processing System模块,双击进入设置

随后出现对应Processing System模块,双击进入设置

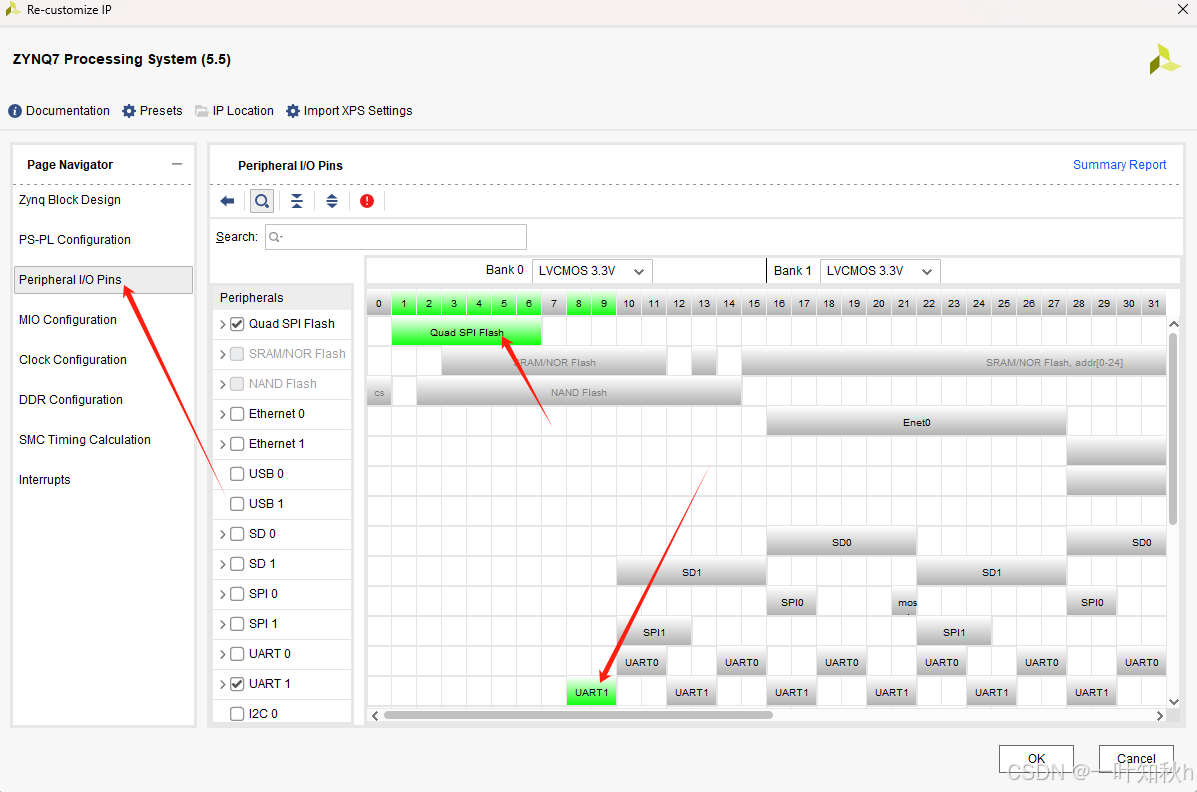

选择Preihpheral IO PIns,根据板载设置,一般设置好QuadSPI和UART即可简单使用。

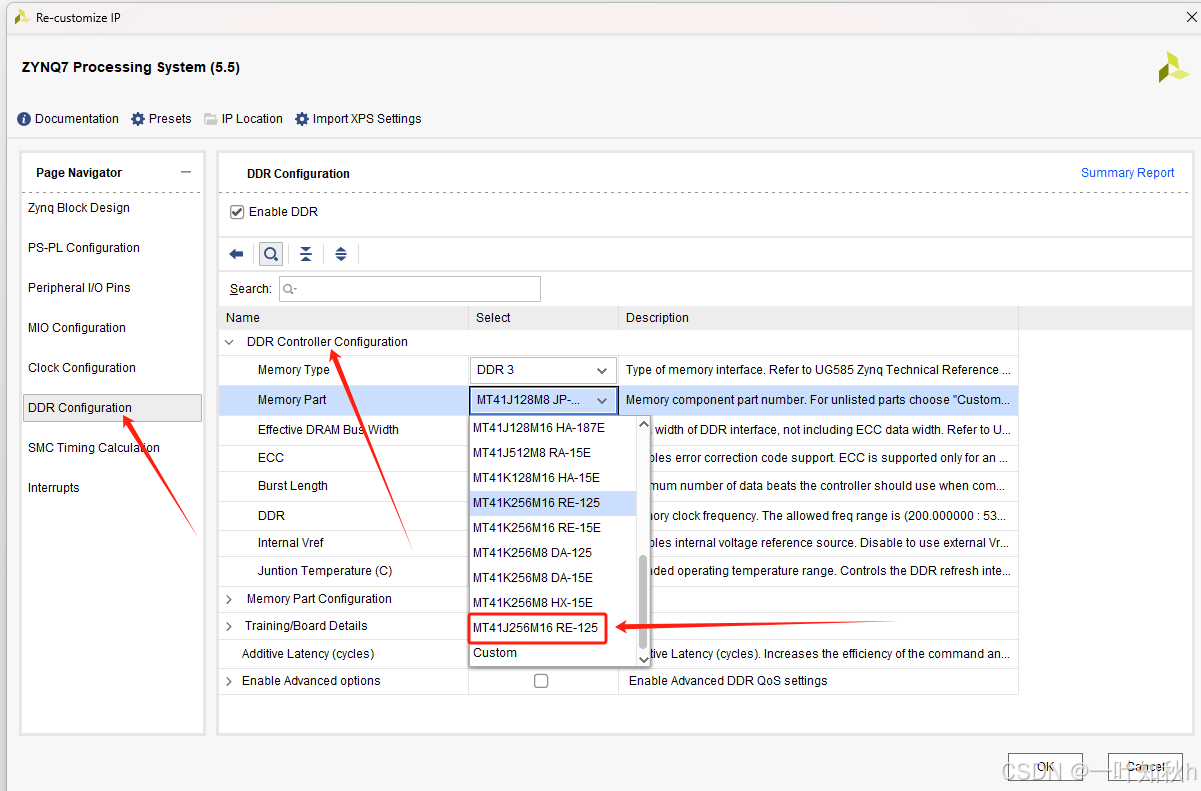

随后进入DDR的设置,按如下步骤选择MemoryPart(应是和板载芯片最接近的设置)

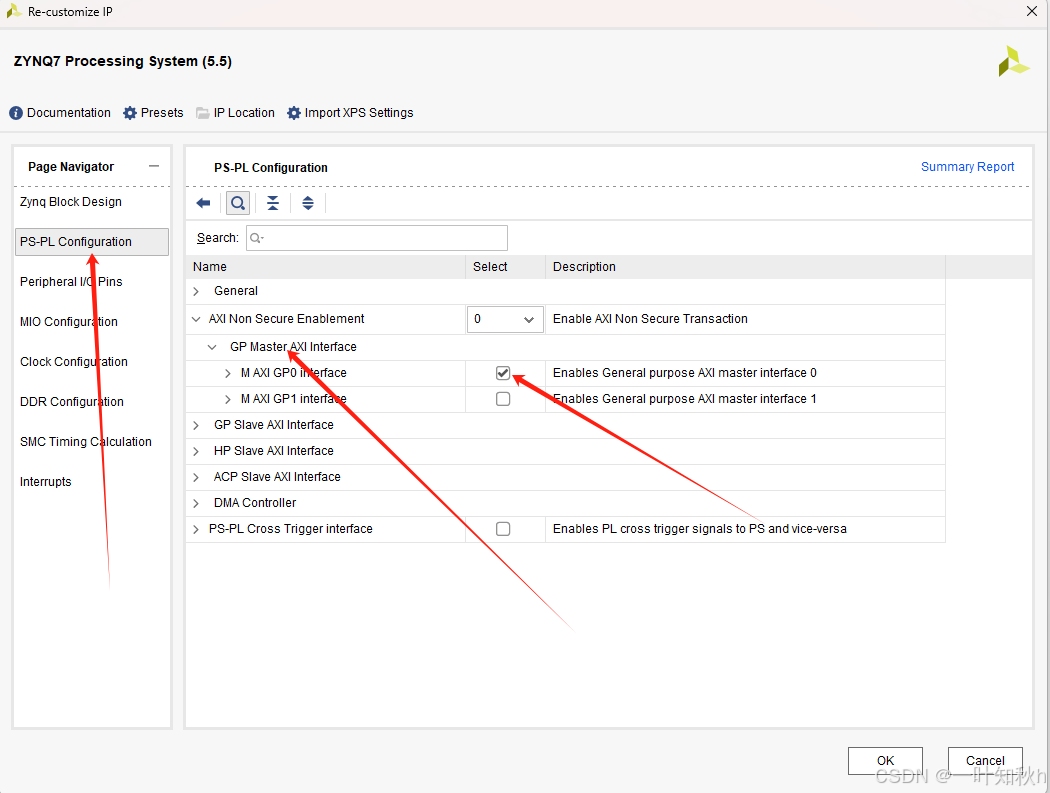

随后按如下操作取消勾选,得到最终的PrecessingSystem模块。

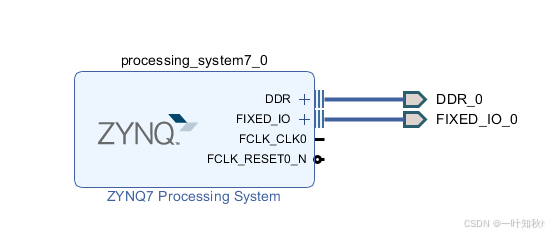

右键两个引脚,选择自动接出,如下图

右键两个引脚,选择自动接出,如下图

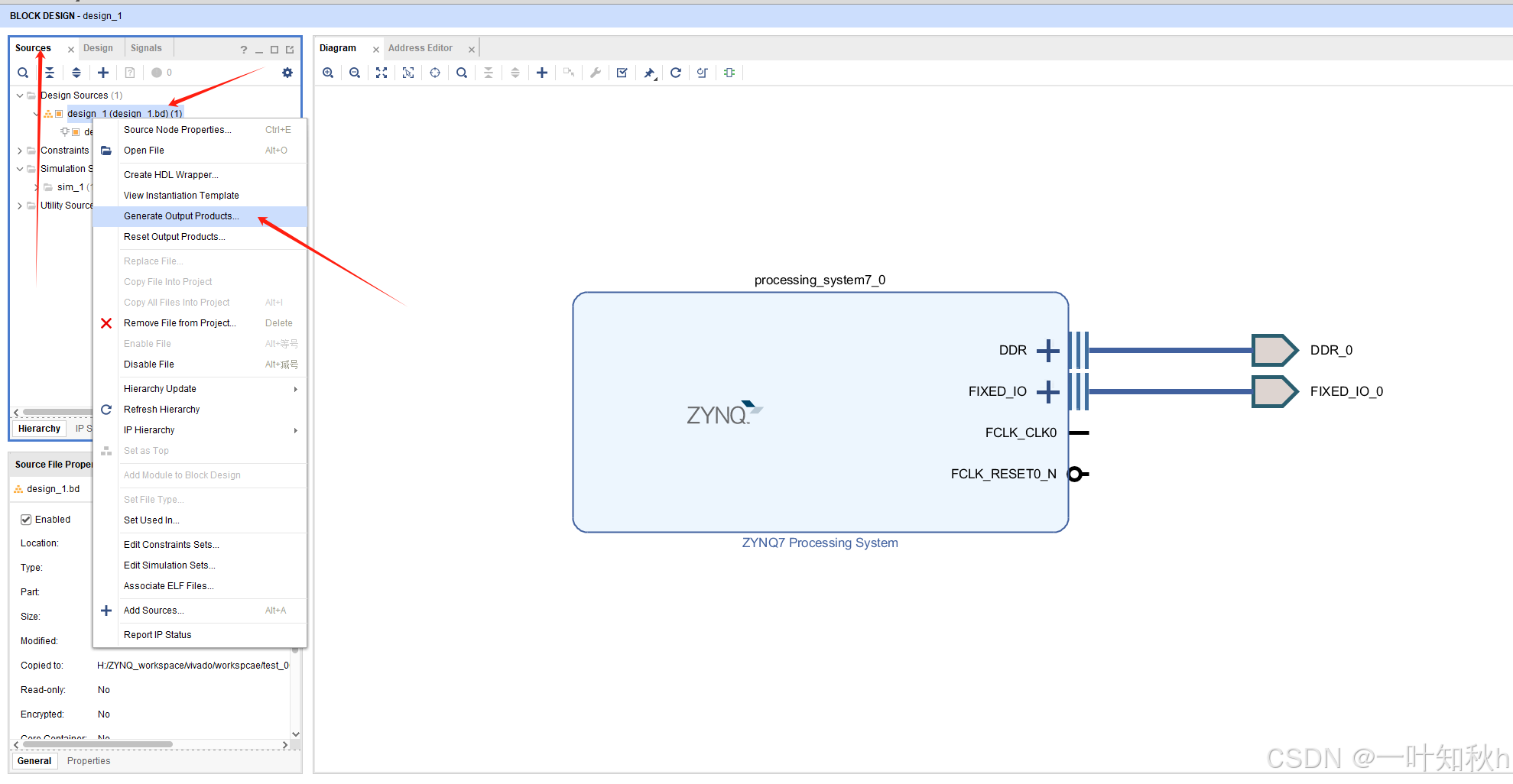

随后点击左上角Sources,选中刚刚创建的bp文件,右击选择生成输出项目

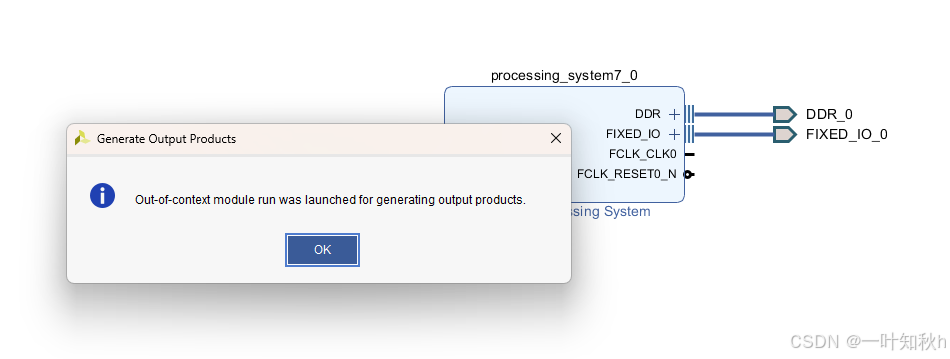

点击Generate即可。

点击Generate即可。

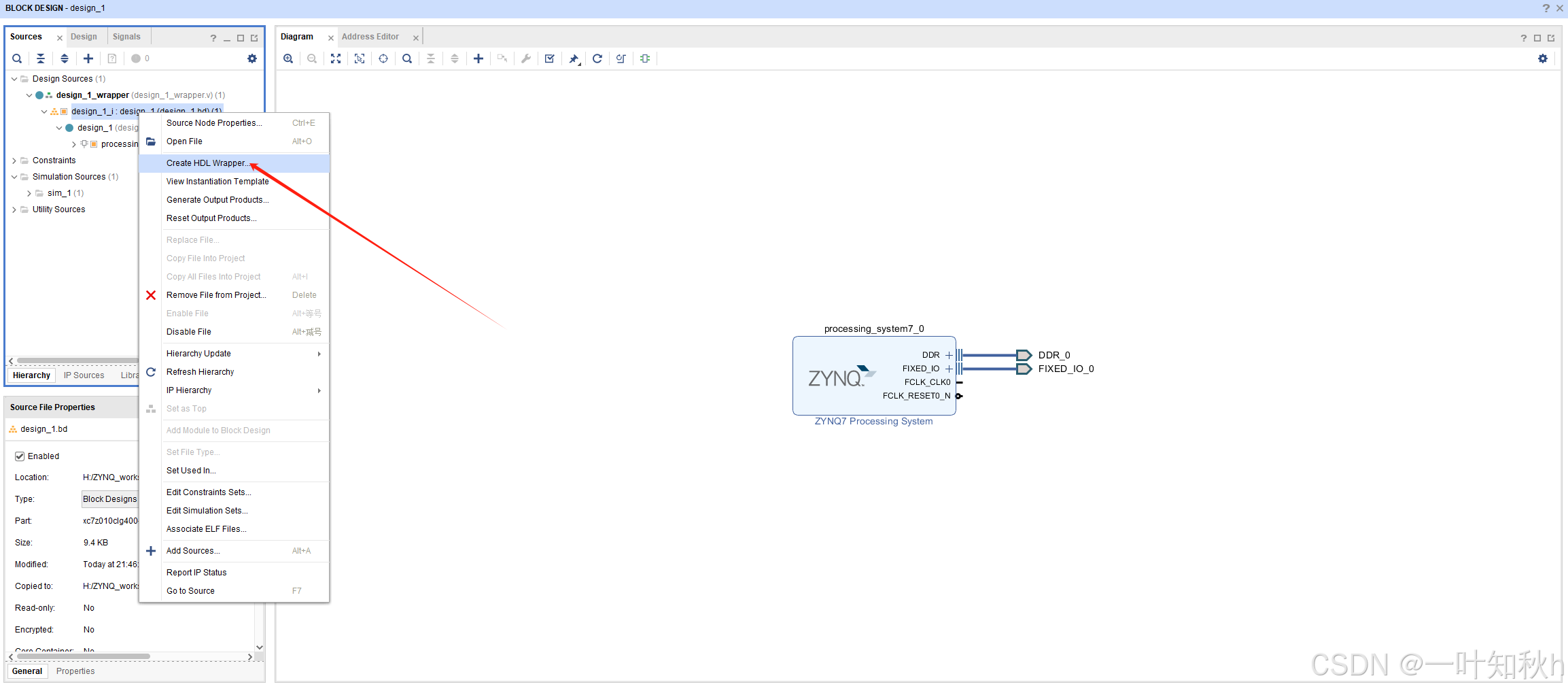

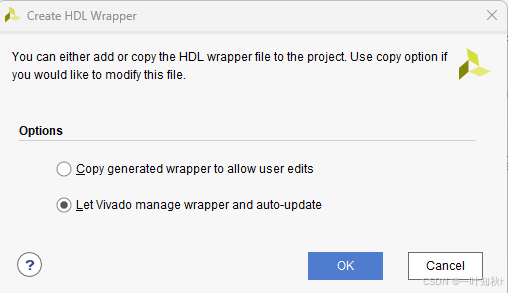

随后继续选中bp文件,右击选择创建顶层文件,点击OK

随后点击创建bit流文件,而后默认点击Yes,跳转后默认点击OK即可,生成文件后,弹出界面选择cancel即可,不需要进行修改。

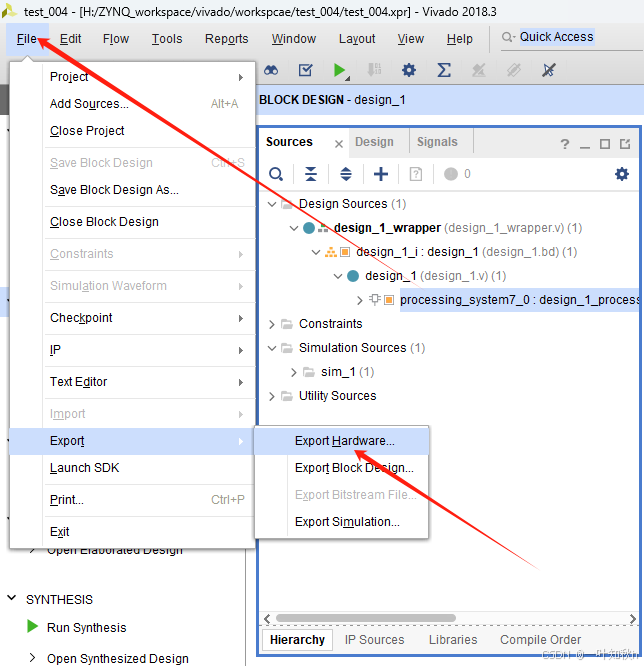

随后选择File,选择导出,将生成的bit流文件导出到硬件Hardware,默认点击OK即可。但需要勾选中包含流文件(including Stresming file)

随后选择Launch SDK,启动PS端,随后默认点击OK即可。

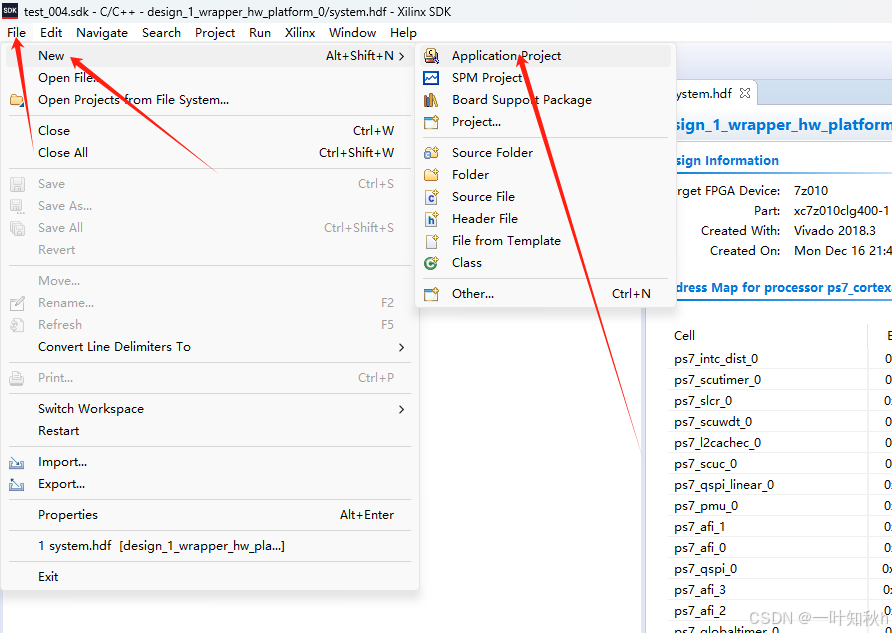

页面跳转至如下界面:

页面跳转至如下界面:

随后依次点击左上角File,选择New,选择Application Project进行文件创建:

根据自己情况为新创建的文件命名,随后选择提供的空模板,点击Finish即可。

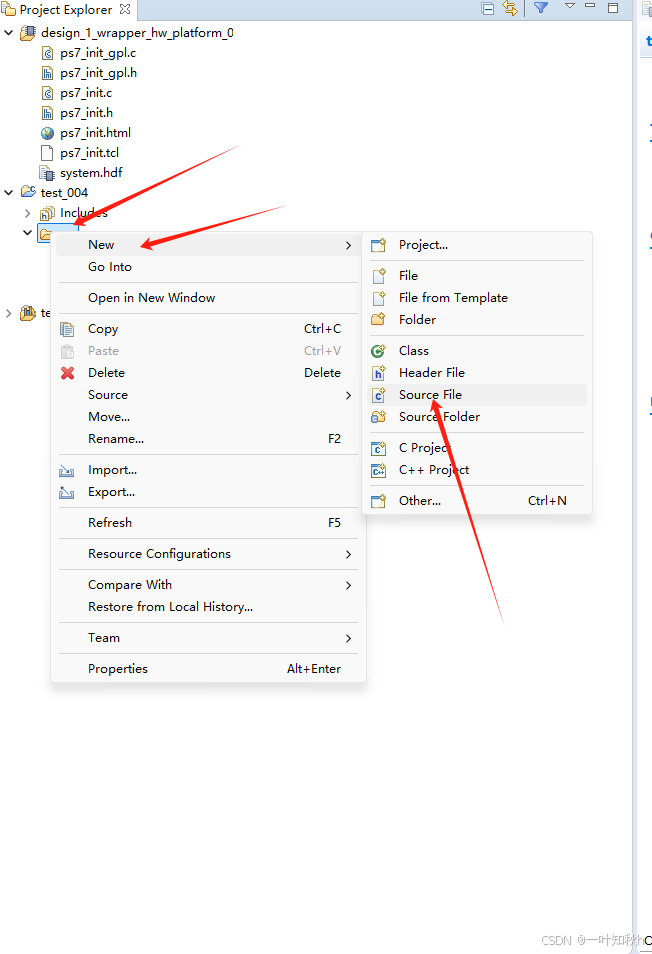

随后单击选择新建好的工程文件夹,找到src文件夹并新建main.c文件

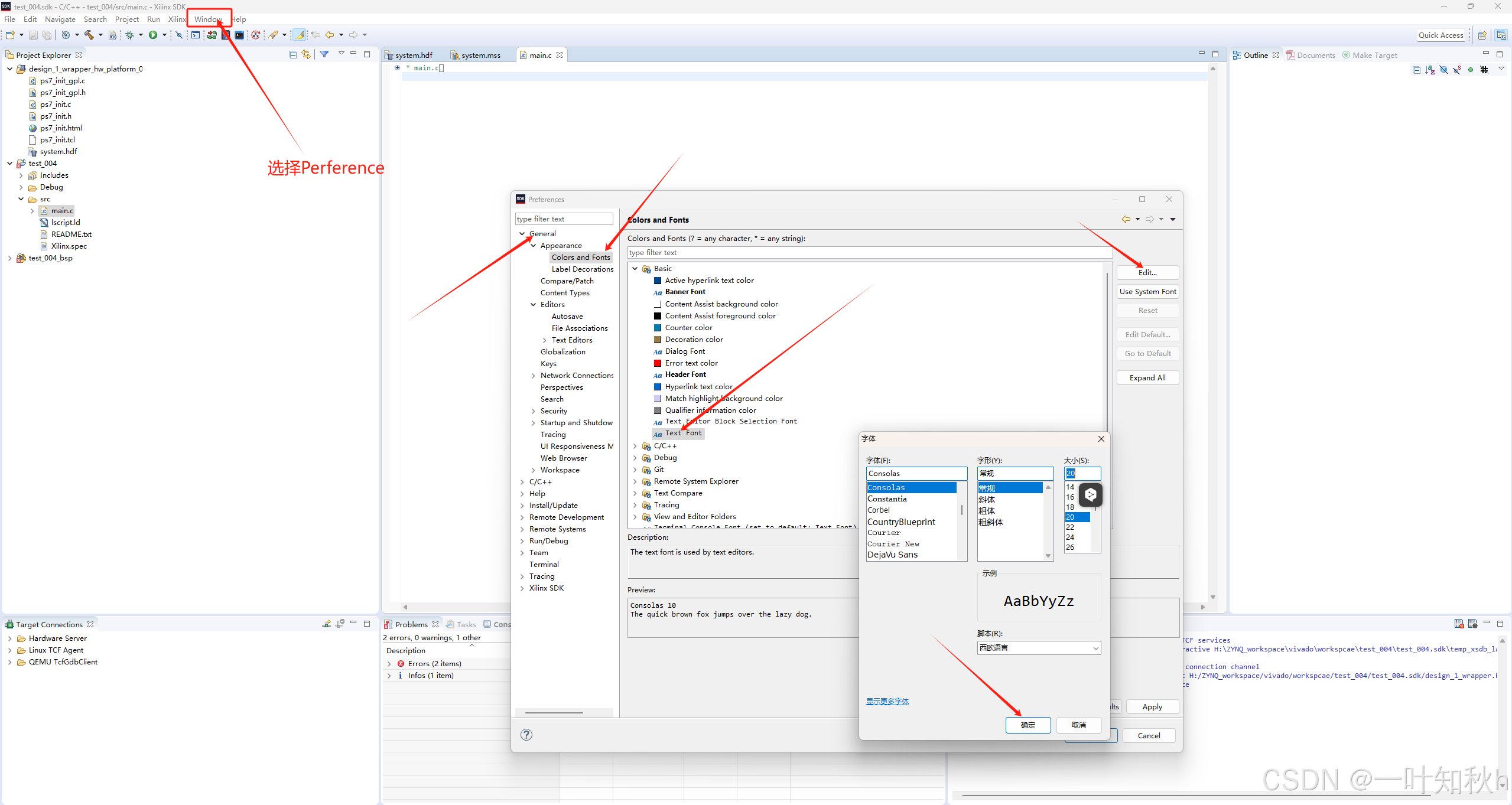

双击打开新建好的main.c文件,发现程序字号显示较小,按下操作调整主界面字号,选择Window->Preference->general->color and font,选择Text Font,点击左侧Edit,根据需要修改即可。

随后将下面的几行代码复制到新建的main.c文件中,保存(运行)。

cpp

int main(void){

while(1){

}

}

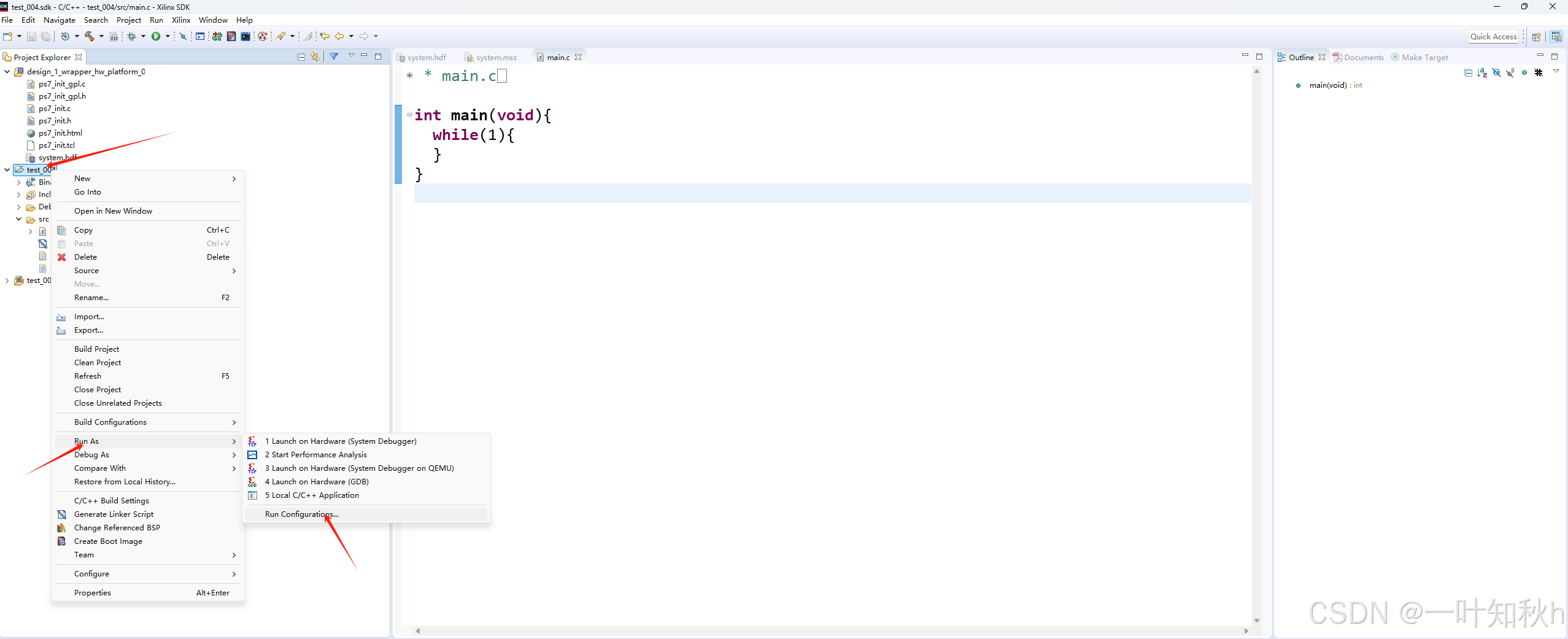

随后选择工程文件,选择Run as->Run Configuration

选中最下面的选项,双击后,勾选右侧界面的Reset entire system和ProgramFPGA,随后点击run

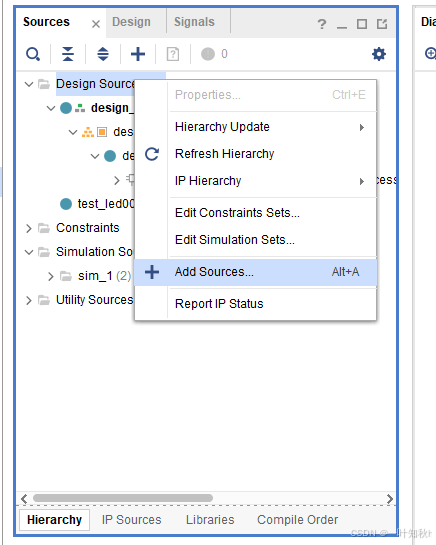

随后切换到PL端,给工程文件添加现有的LED闪烁的代码文件(源文件):

随后切换到PL端,给工程文件添加现有的LED闪烁的代码文件(源文件):

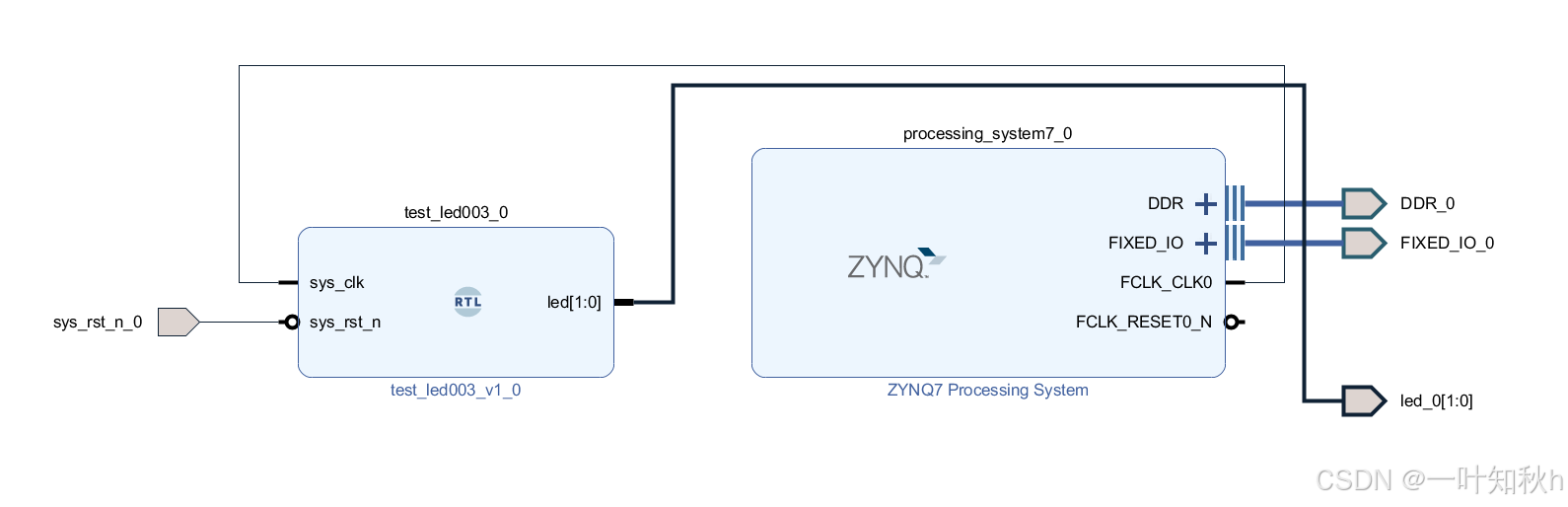

添加完后在Diagram主界面中右击选择添加model,将刚刚添加到工程文件中的led闪烁文件模块加入到Diagram界面并连线,将复位和led输出两个引脚选中,并点击Make Externalm,最终如下图:

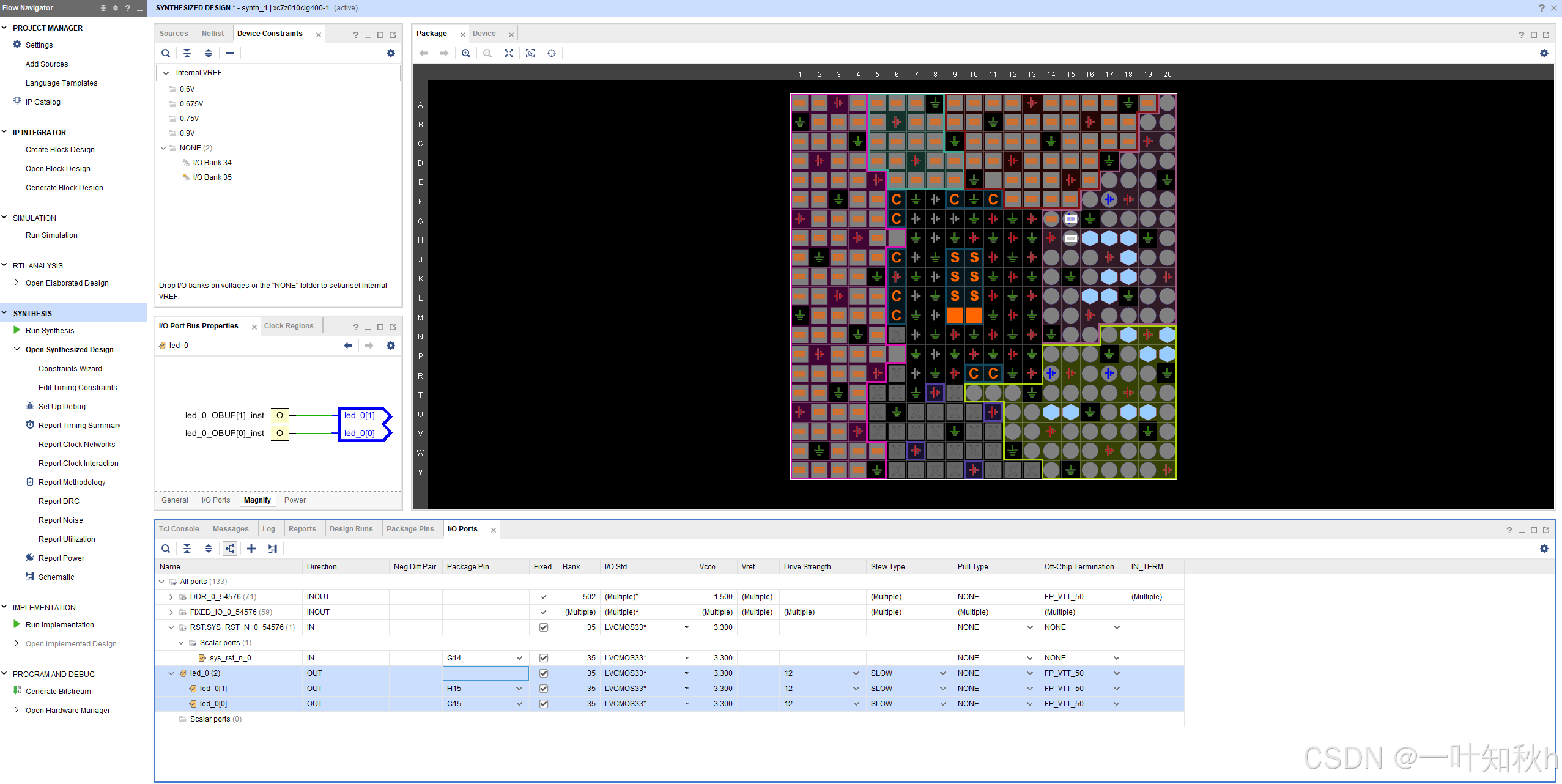

随后点击右侧的Run Synthesis,进行综合分析并进行IO引脚的配置(结合板载的原理图)

引脚配置完成后如下图:

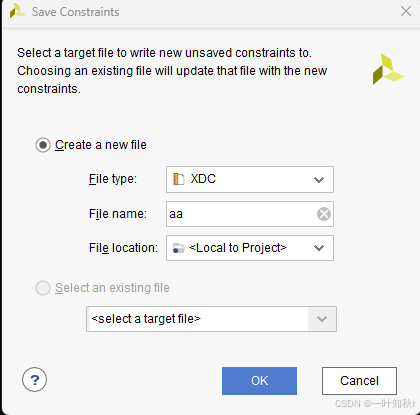

随后将保存的文件自行命名(不需要和工程文件名字统一,但不可以是中文字符),随后点击OK

点击左侧左下角的生成bit流文件,默认点击OK,等待生成即可。

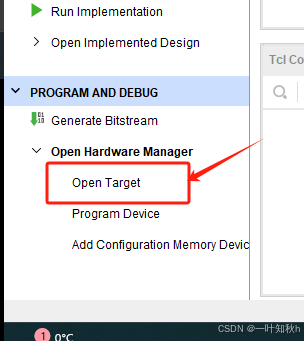

随后选中OpenTarget,选择自动连接 auto connect

随后依次点击Program device ->Program来将生成后的bit流文件下载烧写至板载中。

随后则可以观察到板载小灯闪烁,上述过程成功。

另外在下面附上FPGA两个小灯交替闪烁的代码:

`timescale 1ns / 1ps

module test_led003(

input sys_clk,

input sys_rst_n,

output [1:0] led

);

reg [25:0] cnt;

assign led = (cnt<26'd25_000_000) ? 2'b01 : 2'b10;

always @ (posedge sys_clk or negedge sys_rst_n)

begin

if(!sys_rst_n)

cnt <= 26'd0;

else if (cnt< 26'd50_000_000)

cnt <= cnt + 1'b1;

else

cnt <= 26'd0;

end

endmodule另附上修改后的三个小灯连续闪烁的代码:(注意修改对应的管脚分配)

`timescale 1ns / 1ps

module test_006(

input sys_clk,

input sys_rst_n,

output [2:0] led // 修改为3位宽,控制三个LED

);

//reg define

reg [25:0] cnt;

wire [2:0] led_state; // 定义一个3位宽的wire,用于存储LED状态

// 使用case语句来实现三个LED的交替闪烁

assign led_state = (cnt > 26'd25_000_000) ? 3'b001 : // 当计数器大于25,000,000时,LED1亮

(cnt > 26'd12_500_000) ? 3'b010 : // 当计数器大于12,500,000时,LED2亮

3'b100; // 否则,LED3亮

assign led = led_state; // 将led_state的值赋给led输出

always @ (posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

cnt <= 26'd0;

else if (cnt < 26'd50_000_000)

cnt <= cnt + 1'b1;

else

cnt <= 26'd0;

end

endmodule